## Low-cost scanner checks diode matrix automatically

by C. S. Chi Shrewsbury, Mass.

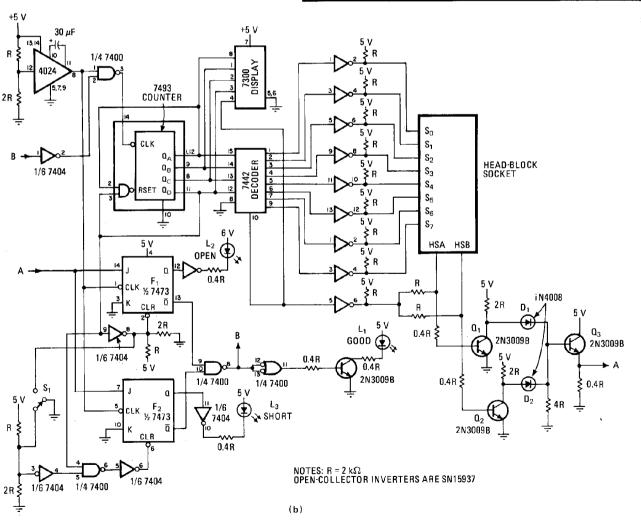

Manually testing a diode matrix for open or shorted elements is tedious, because every matrix point has to be checked to isolate failed diodes. But faults are detected automatically with the circuit shown in the figure.

This tester steps through each matrix row to find the location of any open diodes, then turns into a simple go/no-go matrix tester to check for the (rare) presence of a shorted diode. Although intended specifically for testing an eight-channel read/write head used for computer mass-storage applications, the circuit can be modified for testing a matrix of any kind or size.

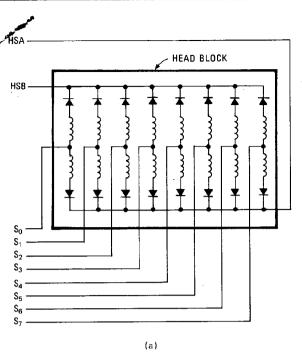

The eight ferrite-head assemblies forming the read/write 8 × 2 matrix are mounted in a head block, the

standard configuration (a). The head block is activated by asserting a logic 0 on the two control lines, HSA and HSB. Each individual ferrite head in the block is selected by means of lines  $S_0$ – $S_7$ .

Of the nine test sequences generated by the circuit, eight test the matrix channel by channel. Each activates a different channel sequentially and checks it for open elements. The ninth test sequence deactivates all channels simultaneously to check for shorted elements. Note that in this particular circuit either the diode or the ferrite coil may be faulty.

In the scanner (b), a voltage-controlled oscillator, the 4024, generates the 10-kilohertz clock signal required for the 7493 binary counter. The counter steps the 7442 decoder through each of the eight matrix points, while the 7300 displays the scanned location.

In the circuit's active mode (the first eight sequences), only the channel selected at the 7442 can force current into its respective head block terminal  $S_0$ – $S_7$ . If the elements in the channel are good, current flow will return to ground by way of the HSA and HSB lines.

When all is well,  $Q_1$  and  $Q_2$  will be saturated, and  $Q_3$

will be off; the signal at A will be low, and light-emitting diode  $L_1$  will be on, indicating no fault. If current fails to emanate from HSA or HSB, however,  $Q_1$ ,  $Q_2$ , or both will turn off,  $Q_3$  will turn on, and A will go to logic 1; thus the 7473 flip-flop  $F_1$  will set, disabling the clock, and  $L_2$  will turn on. The 7300 will indicate the channel which has the open diode.

After each channel has been activated in succession, the blocking mode is entered, which turns off all channels. Lines HSA and HSB are brought to logic 1, thus back-biasing all the diodes in the head. Should any of the diodes be leaking or shorted either  $Q_1$  or  $Q_2$  or both will turn off, causing  $F_2$  to set and  $L_3$  to light. The system clock is again disabled.

Detecting one fault in the matrix does not preclude the possibility of finding other faults. The reset switch,  $S_1$ , can be used to clear  $F_1$  and  $F_2$ , to start the system clock again. The circuit counter, which has been sitting at the location of the last matrix point found faulty, then continues on until the next fault is found.

Engineer's notebook is a regular feature in *Electronics*. We invite readers to submit original design shortcuts, calculation aids, measurement and test techniques, and other ideas for saving engineering time or cost. We'll pay \$50 for each item published.

Matrix tester. Circuit automatically scans diode matrix (a) to find open or shorted elements. It sequentially activates each channel in read/write head to locate open elements, deactivates all channels simultaneously to check for shorted components (b).