## A Micropower Voltage Reference

National Semiconductor Linear Brief 34

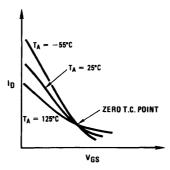

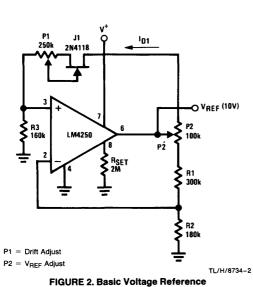

A low-drift voltage reference can be easily made by converting a zero temperature coefficient current to a voltage. JFETs biased slightly below pinch-off exhibit a zero temperature coefficient drain current ( $I_D$ ) as shown in *Figure 1*. With the above property and a micropower operational amplifier, used to convert the drain current to a voltage, a low power consumption voltage reference can be built as shown in *Figure 2*. The consumption of LM4250 op amp is programmed through resistor R<sub>SET</sub>. Potentiometer P1 should be adjusted for low output ( $V_{REF}$ ) temperature coefficient. Actually, it can be trimmed for positive, negative or zero temperature coefficient. The output voltage is trimmed through P2 and it is expressed by:

$$\begin{split} V_{REF} &= I_{D1} \, (P_2' + R1 + R2), \\ R2 &= R3, I_{D1} \cong I_{DSS} \left[ 1 - \frac{V_{GS}}{V_P} \right]^2 \end{split}$$

With the values shown in Figure 2, the temperature coefficient of the output is 0.002%/°C and the overall standby

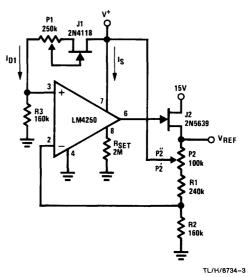

current less than 100  $\mu$ A. The characteristics of the LM4250 are a function of its supply current, which depends on R<sub>SET</sub>, and V<sup>+</sup>. V<sup>+</sup> can be provided by V<sub>REF</sub> through the addition of a second FET, J2, shown in *Figure 3*. This way the parameters of the op amp will be independent of the unregulated input. The reference voltage can be taken from the wiper of the potentiometer P2 (V<sub>REF</sub> = V<sup>+</sup>) or from the source of J2 (V<sub>REF</sub> > V<sup>+</sup>). In the first case, the output impedance of the circuit is quite high and buffering may be required according to the application. The output impedance in the second case is low, essentially the 1/gm of (J2) divided by the loop gain of the circuit. In this case, a small temperature coefficient due to the supply current of the LM4250 is going to be added and be compensated for by an additional trimming of P1. V<sub>REF</sub> is computed by:

$$\begin{split} V_{REF} &\cong I_{D1} \, [P2 + R1 + R2] + P_2^{v} \, [I_S + I_{D1}], \\ R2 &= R3, I_S \cong \frac{6 \, (V^+ - V_{BE})}{R_{SET}} \end{split}$$

FIGURE 1. FET Transfer Characteristics

TL/H/8734-1

FIGURE 3. Improved Voltage Reference