### **APPLICATION NOTE**

**By R. TIZIANI**

## THERMAL CHARACTERISTICS OF THE MULTIWATT PACKAGE

#### INTRODUCTION

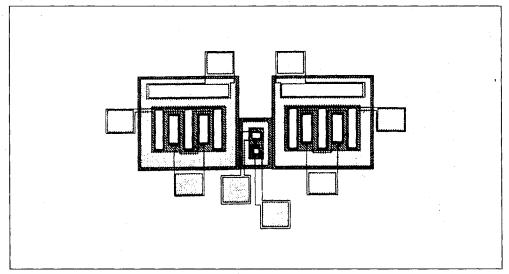

This Application Note provides a complete thermal characterization of the Multiwatt ® package (multilead double TO-220 - fig. 1).

**7** SGS-THOMSON MICROELECTRONICS

Characterization is performed according with recomandations included in the G32-86 SEMI guideline, by means of a dedicated test pattern. It refers to :

- 1. Junction to case thermal resistance Rth(j-c)

- Junction to ambient thermal resistance Rth(j-a)

- Junction to ambient thermal impedance for single pulses and repated pulses, with different pulse width and duty cycle;

- 4. Thermal resistance in DC and pulsed conditions, with a typical external heat sink.

Most of the experimental work is related to the thermal impedance, as required by the increasing use of switching techniques.

Figure 1 : Multiwatt Assembly.

#### EXPERIMENTAL CONDITIONS

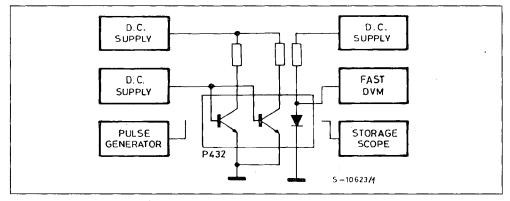

The thermal evaluation was performed by means of the test pattern P432, which is a 20K mils<sup>2</sup> die with a dissipating element formed by two transistors working in parallel and one sensing diode. In order to characterize the worst case of a high power density IC, the total size of the element is 2K mils<sup>2</sup> with a power capability of 20W. Measurement method is described in Appendix A.

Samples with the indicated characteristics were prepared :

Package Multiwatt 15 leads

| Frame Material            | Copper      |

|---------------------------|-------------|

| Slug Thickness            | 1.5mm       |

| Slug Thermal Conductivity | 3.9W/cm°C   |

| Die Attach                | Soft (PbSn) |

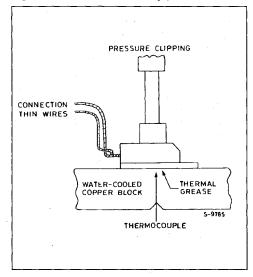

Measurement of junction to case thermal resistance  $R_{th(j-c)}$  is performed by holding the package against a water cooled heat sink, according with fig. 2. A thermocouple placed in contact with the slug measures the reference temperature of the case.

For junction to ambient thermal resistance  $R_{th(j;a)}$  the samples are suspended horizontally in a one cubic foot box, to prevent drafts.

Both DC and pulsed conditions are used ; in the second case the contribution of package thermal capacitance is effective and transient thermal resistances much lower than the steady stata  $R_{th(j-a)}$  can be found, according to pulse length and duty cycle.

The effect of the external heat sink is quantified, using as test vehicle the commercially available heat sink THM7023 especially developed by Thermalloy for the Multiwatt package, whose thermal resistance in still air is about 9°C/W.

The measurement circuit shown in fig. A3 was used for all the thermal evaluations.

#### JUNCTION TO CASE THERMAL RESIS-TANCE

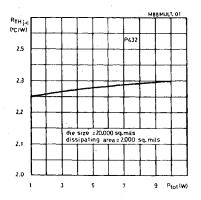

The dependance of  $R_{th(j\cdot c)}$  on the dissipated power is reported in fig. 3.

It is well known that the main contribution to  $R_{th(j-c)}$  of power packages in given by the silicon die.

AN257/0189

Figure 2 : Measurement of Rth (j-c).

Figure 3 : Rth (j-c) of Multiwatt Package vs. Power Level.

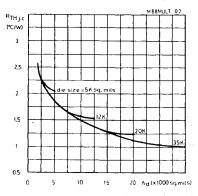

FOR DEVICES OTHER THAN THE TEST PAT-TERN P432 THE CALIBRATION CURVE OF FIG. 4 IS NEEDED.

It shows the relationship between  $R_{th(j-c)}$  and the dissipating area existing on the silicon die (power diodes, power transistors, high current resistors), for different die sizes.

Figure 4 : Rth(j-c) Thermal Resistance vs. Die Size and on Die dissipating Area.

#### JUNCTION TO AMBIENT THERMAL RESISTANCE

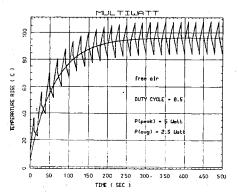

In medium power applications (1.5-2W), the Multiwatt package can be used without external heat sink, thanks to the significant size (about 3.5cm<sup>2</sup>) of its integrated thermal mass.

Its  $R_{th(j;a)}$  has two contributions : the  $R_{th(j;c)}$ , mainly due to the silicon die (as shown in fig. 4) and the thermal resistance of the copper slug  $R_{th \ slug}$ .

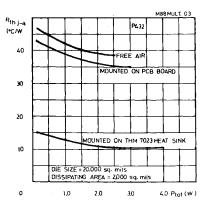

Figure 5 : R<sub>th(j-a)</sub> of Multiwatt Package vs. dissipated Power.

Fig. 5 gives the relationship between  $R_{th(j-a)}$  and the power dissipation level for the P432 test pattern is still air, on PC board and on a commercial heat sink.

IN ORDER TO HAVE AN ACCURATE VALUE FOR OTHER DEVICES, WITH DIFFERENT DIE SIZE AND DISSIPATING AREA, VALUES OF FIG. 5 SHOULD BE CORRECTED THROUGH THE CALI-BRATION CURVE OF FIG. 4 CORRECTION TERM IS ALWAYS IN THE RANGE OF 0-2°C/W ; THEREFORE, IT AFFECTS THE Rth(j=a) OF NO MORE THAN 5% IN STILL AIR OR WITH THE PACKAGE MOUNTED ON PC BOARD.

#### TRANSIENT THERMAL RESISTANCE IN PULSED CONDITION (without external heat sink)

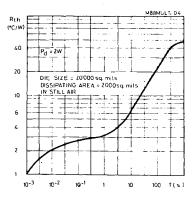

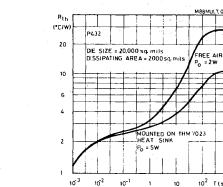

The effect of single pulses of different length and height for the Multiwatt package without any external heat sink is shown in fig. 6.

This behaviour is discussed in Appendix B. Due to a significant thermal capacitance (C =  $2J/^{\circ}$ C) and correspondingly long risetime ( $\tau = 80$ s), single pulses up to 30W can be delivered to the Multiwatt package for 1s with acceptable junction temperature increase.

IN ORDER TO HAVE ACCURATE  $R_{th}$  (to FOR OTHER DEVICES, WITH DIFFERENT DIE SIZE AND DISSIPATING AREA, VALUES OF FIG. 7 MUST BE CORRECTED AS DESCRIBED IN EXAMPLE 2 OF THE LAST SECTION.

# Figure 6 : Transient Thermal Resistance for Single Pulse.

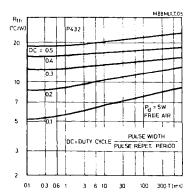

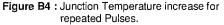

Repetition of pulses with defined  $P_d$ , period and duty cycle DC (ratio betwen pulse length and signal period), gives rise to oscillations in junction temperature as described in Appendix B.

The transient thermal resistance corresponding to the upper limit of the curve of fig. B4 (peak transient thermal resistance) is reported in fig. 7 and depends on pulse length and duty cycle. It can be noticed that DC becomes less effective for longer pulses.

#### TRANSIENT THERMAL RESISTANCE IN PULSED CONDITION (with external heat sink)

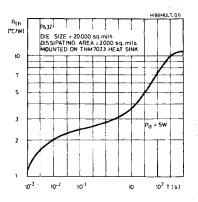

Characterization has been repeated with a commercial heat sink (Thermalloy THM7023) in order to have an example of the effect of an external thermal mass on the impedance of the thermal module.

Relationship between transient R<sub>th</sub> and pulse length is reported in fig. 8.

The effect of the increased thermal capacitance is evident in fig. 9, where thermal data of fig. 6 and 8 are compared : it can be noticed that the curves are definitely different for pulses longer than 1s, corresponding about to the rise time of the slug. The effect of the thermal mass is to keep low the heating rate of the silicon die thus allowing a better power management of long power pulses. This conclusion has general validity and can be applied to other heat sinks than the one considered in this note.

Figure 7 : Peak Transient Rth vs. Pulse width and Duty Cycle.

Figure 8: Transient Rth for single pulses, with Heatsink.

#### APPENDIX A

The thermal resistance evaluation is performed with the especially designed test chip P432 which has two bipolar power transistor and one sensing diode (fig. A1). The active area is about 2000 mils<sup>2</sup> on a 35000mils<sup>2</sup> chip. Its lay-out was optimized in order to have a uniform temperature area, once the two transistor are powered ; the sensing diode is placed at the center of this area.

Figure A1 : Test Pattern P432 Lav-out.

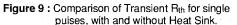

The relationship between the forward voltage Vf of the diode at the constant current of 100µA and the temperature is shown in fig. A2. The curve calibrates the junction temperature through the voltage drop of the diode.

10 10<sup>2</sup> T(s)

10-3

The measurement circuit is shown in fig. A3. A storage oscilloscope or a fast digital voltmeter can be used for recording the Vf value.

- 2 W

Figure A2 : Calibration Curse (sensing diode).

Figure A3 : Measurement Circuits.

#### APPENDIX B - THERMAL MANAGEMENT IN PULSED CONDITION

### THERMAL RESISTANCE AND CAPACITANCE

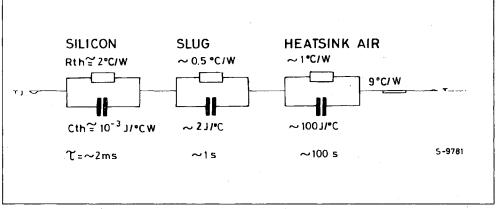

The electrical equivalent of heat dissipation, for a thermal module formed by the active device with its package and the external heat sink is shown in fig. B1.

To each cell of the thermal chain are associated a value of thermal resistance  $\mathsf{R}_{th}$  (°C/W) and a value of thermal capacitance  $\mathsf{C}_{th}$  (J/°C). The former informs about temperature increase due to the element represented by the cell ; as, in the example under consideration, heat transfer is mainly based on conduction for the silicon, the copper integrated heat sink and to metallic body of the external heat sink  $\mathsf{R}_{th}$  can be calculated from the relationship :

$$R_{th} = \frac{\gamma}{K \times S}$$

where K is the thermal conductivity of the material, the length of the conductive path and S its section.

Thermal capacitance  $C_{th}$  is the capability of heat accumulation ; it depends on the specific heat of the material and on the volume effectively interested by heat exchange (this means that the parts which are not heated during heat dissipation DO NOT contribute to thermal capacitance). Thermal capacitance is given by :

#### $C_{th} = d \times c_t \times V$

where d is the density of the material,  $c_t$  its specific heat and V the volume interested to heat accumulation.

The last element of the network, assumed as purely resistive, is due to convection and radiation from the external heat sink towards the ambient.

Figure B1 : Electrical Equivalent of Multiwatt Package Mounted on the External Heatsink.

Each cell has its own risetime  $\tau$  , given by the product of the thermal resistance and capacitance :

$$\tau = R_{th} \times C_{tl}$$

The value of the time constant determines whether a cell approaches equilibrium rapidly of slowly if  $R_{th}$  or  $C_{th}$  increases, equilibrium is reached at a slower rate. The following relationship is valid for each cell :

$$\Delta \mathsf{T} = \mathsf{R}_{\mathsf{th}} \times \mathsf{P}_{\mathsf{d}} \left[ 1 - \mathrm{e}^{-\mathrm{t/r}} \right] (1)$$

Typical values of  $R_{th},\,C_{th}$  and  $\tau\,$  for Multiwatt application are shown in fig. B1.

When power is switched on, temperature increase is ruled by subsequent charging of thermal capacitances while the value reached in the steady state depends on thermal resistances only. Qualitative behaviour of the network of fig. B1 is shown in fig. B2.

Figure B2 : Qualitative T<sub>j</sub> increase (network of fig. B1) for repeated Power Pulse.

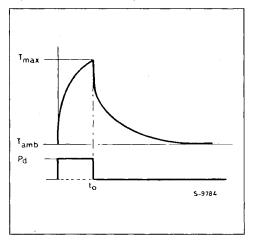

#### SINGLE POWER PULSE

When the pulse length has an assigned value, effective  $T_j$  can be significantly lower than the steady state  $T_j$  (fig. B3.).

Figure B3 : Effect of a Single Power Pulse.

For any pulse length t<sub>o</sub>, a transient thermal resistance R<sub>th</sub> (t<sub>o</sub>) is defined, from the ratio between the junction temperature at the end of the pulse and the dissipated power. Obviously, for shorted pulses, R<sub>th</sub> (t<sub>o</sub>) is lower and a higher power can be dissipated, without exceeding the maximum junction temperature T<sub>j-max</sub> allowed to the IC from reliability considerations. Fig. 7 and 9 of this Application Note give experimental values of R<sub>th</sub> (t<sub>o</sub>) for the two cases of the Multiwatt package without and with external heat sink.

#### REPEATED PULSES

When pulses of the same height  $P_d$  are repeated with a defined duty cycle DC and pulse length is short in comparison with the total risetime of the system (many tens of seconds) the train of pulses is seen by the system as a continuous source, at a mean power level of

$P_{davg} = P_d \times DC$

The average temperature increase is :

$\Delta T_{avg} = R_{th} \times P_{davg} = R_{th} \times P_{d} \times DC$

On the other hand, the silicon die ( $\tau s = 1-3ms$ ) is able to follow frequencies of some KHz and junction temperature oscillates about the average as qualitatively shown in fig. B4.

The thermal resistance corresponding to the peak of the oscillation at equilibrium (peak thermal resistance  $R_{th \, peak}$ ) is now given by fig. 5, and can be obtained if pulse length and duty cycle are known;  $P_{dmax}$  is derived from the same figure.

#### APPLICATION EXAMPLES

EXAMPLE 1 - MAXIMUM Pd FOR SINGLE PULSE OF ASSIGNED LENGTH

PROBLEM : define the maximum  $P_d$  for a single pulse with a length of 20ms in the case of Multiwatt package used without heat sink. Ambient temperature is 50°C ; maximum temperature is 130°C. Die size is 20K mils<sup>2</sup>, with dissipating area of 2K mils<sup>2</sup> (as in P432 test pattern).

SOLUTION : allowed temperature increase  $\Delta T$  is 80°C. Having a R<sub>th(j-a)</sub> of 39°C/W, Multiwatt package can dissipate about 2W in steady state. From fig. 7 the transient thermal resistance corresponding to one single pulse of 20ms is R<sub>th</sub> (20ms)P<sub>432</sub> = 2.2°C/W. A peak of 80/2.2 = 36.3W can be applied to the circuit.

# EXAMPLE 2 - CORRECTION FOR DIE SIZE AND DISSIPATING AREA

PROBLEM : correct the results obtained in example 1, for assigned die size and dissipating area. Practical case : IC having a die size of 35K mils<sup>2</sup> with a dissipating area of 20k mils<sup>2</sup>.

SOLUTION : from fig. 5, thermal resistances of P432 and of the IC under consideration are  $R_{th P432} = 2.3^{\circ}C/W$  and  $R_{th(i-c)IC} = 1.2^{\circ}C/W$ .

As the length of the pulse is 10-15 times longer than the rise time of the silicon, the die (first cell of fig. B1) can be assumed to have reached its equilibrium condition.

$R_{th}$  (20ms) found in previous example has to be corrected in order to take into account the new value of  $R_{th(j\text{-}c)}$  :

$\begin{aligned} R_{th} & (20ms)_{IC} = R_{th} & (20ms)_{P432} \\ & - R_{th(j-c)P432} + R_{th(j-c)IC} = \\ & = 2.2 - 2.3 + 1.2^{\circ}C/W = 1.1^{\circ}C/W \end{aligned}$

A single pulse of 80/1.1  $\cong$  72W can be delivered to such device.

When the pulse has the same order of silicon rise time  $\tau$  P432 is about 1ms) another type of correction is needed. In first approximation,  $\tau$  increase with dissipating area with the relationship :

$t_{IC} = \sqrt{20K_{IC}/2K_{P432}} \times \tau_{P432} \equiv 3.1 \text{ms}$

Expansion of the exponential term of relationship (1) limited to the first term term, is :

Rth IC (to) ≅ Rth P432 (to) /3.1

for  $t_0 = 1 \text{ ms}$ :

$R_{th IC}$  (1ms) = 1.05/3.1°C/W  $\cong$  0.34°C/W

A single pulse of  $80/0.34 \cong 235W$  can be delivered to such device.

EXAMPLE 3 - Rth WITH REPEATED PULSES

PROBLEM : find the peak power which can be dissipated by Multiwatt package without heatsink, when power is continuously switched on 10ms and switched off 90ms. Ambient temperature is 50°C, maximum temperature is allowed to be 125°C.

SOLUTION : a maximum  $\Delta T = 75^{\circ}$ C has to be considered. Fig. 5 indicated that for a pulse width of 10ms and a duty cycle of 0.1, R<sub>th peak</sub> is 6.7°C/W. Maximum P<sub>d</sub> is 75/6.7 = 11.2W, with an average temperature increase  $\Delta T_{peak}$  of 39 x 0.1 x 11.2  $\cong$  43°C.