## **Application Briefs**

## GATE RESPONSES SIMPLIFIED A GUIDE FOR THE OCCASIONAL USER OF LOGIC

If you're an experienced logic circuit designer, an expert on Boolean logic, or a recent graduate, the chances are that you'll find this discussion elementary and somewhat obvious.

If, on the other hand, you've spent a good part of a long and productive lifetime with analog circuitry or other matters, and have had only occasionally to reason out the expected behavior of a circuit diagram that contains logic gates, you may wonder why no one has bothered to provide this sort of discussion before.

One will recognize the two basic gate forms in the table below: "AND" with straight-backed input and rounded output, and "OR" with concave input and sharp output. One will also recognize the small circles that indicate "negation," i.e., reversal of logic polarity of the signal appearing at an input or output. And finally, consider that this discussion applies to "positive true" logic, i.e., "0" implies a voltage near ground potential (less than 0.8V for TTL inputs), and "1" implies a positive voltage (greater than 2.0V for TTL inputs).

The key that unlocks the ability to interpret these diagrams (or choose the correct one) quickly is to observe that each diagram goes with an easily recognized statement, such as "All 1's give 1" (AND), "Any 1's give 0" (NOR). This is done by reading direct inputs or outputs as "1" and negated inputs or outputs as zero (think of the circle as a "0"), and the relationship as either all (AND form) or any (OR form).

Any function that is provided by one form of gate can be identically provided with the other form by complementing all input and output markings. Thus the "OR" equivalent to the "AND" gate will still have the response "All 1's give 1,"

but will in addition indicate that the statement "Any 0's give 0" is identical. The equivalent forms are logically derived by "De Morgan's Theorem," but the beauty of this approach is that you don't have to write a logic equation to know what a gate will do, nor do you have to memorize anything further. Just be sure that the person who draws the diagram and the reader of it are both using positive-true logic.

## MIXED INPUTS, COMPLEMENTARY LOGIC, REALIZABILITY

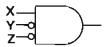

If a gate has both negated and direct inputs, like so,

its function can be read in the same way, applying "all as indicated" for AND gates and "any as indicated" for OR gates. Thus, if X is 1 and Y and Z are 0, the output will be 1. The equivalent statement is: if X is 0, or Y or Z is 1, the output will be 0.

The indicated function must be understood to work independently of the polarity convention for the logic signals. That is, if complementary (i.e., negative true) logic is used for any of the applied signals, it should be inverted; otherwise confusion may arise.

Any of the logic functions indicated on the table can be performed using "NAND" or "NOR" gates only, by using the equivalent functions and additional gates to perform the indicated inversions.

|                | DIRECT<br>FUNCTION        | EQUIVALENT<br>(DEMORGAN'S<br>THEOREM) | RESPONSE |                      |                  |

|----------------|---------------------------|---------------------------------------|----------|----------------------|------------------|

|                |                           |                                       | ALL 0'S  | 0'S AND 1'S<br>01101 | ALL 1'S<br>11151 |

| "AND"          | X Y Z ALL I'S GIVE 1      | X · V · Z<br>ANY ZERO'S GIVE O        | o        | 0                    | 1                |

| "NAND"         | X Y Z  ALL 1'S GIVE 0     | X · Y · Z<br>ANY ZERO'S GIVE 1        | 1        | 1                    | 0                |

| "OR"           | X · Y · Z  ANY I'S GIVE I | X V Ž<br>ALL ZERO'S GIVE O            | 0        | 1                    | 1                |

| "NOR"          | X+Y+Z ANY 1'S GIVE 0      | X V Z                                 | 1        | 0                    | 0                |

| XCLUSIVE<br>OR |                           | DIFFERENT INPUTS GIVE 1               | 0        | 1                    | 0                |

BASIC LOGIC GATES, POSITIVE - TRUE LOGIC