## Single wire connects microcontrollers

### ABEL RAYNUS, ARMITRON INTERNATIONAL, MELROSE, MA

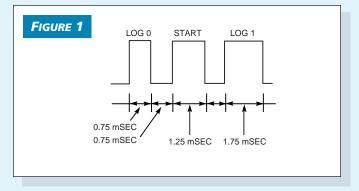

Low-cost  $\mu$ Cs, such as Motorola's 68HC705 Series, offer great simplicity at the expense of some useful functions—notably, serial data transmission. Unlike their predecessors, these  $\mu$ Cs do not have serial communication interfaces (SCIs), serial peripheral interfaces (SPIs), or simple serial I/O ports (SIOPs). This method describes how you can overcome this deficiency by creating an asynchronous serial interface through  $\mu$ C software. The most obvious way to effect the interface is to use pulse-width coding to differentiate the start pulse and the logic 1 and 0 pulses. You can use any value of pulse-width ratio, depending on your design objectives. This application uses the 1-to-2-to-3 ratio, slightly modified for easy programming. So, logic 0, start, and logic 1 have widths of 0.75, 1.25, and 1.75 msec, respectively (**Figure 1**).

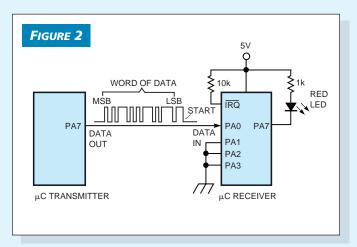

This example uses  $68HC705J1A \ \mu Cs$ . The information to transmit accumulates in the output data register of the transmitting  $\mu C$  (**Figure 2**). The data-transmission subroutine (**Listing 1** shows a fragment) generates the start pulse, which is followed by an 8-bit data word that reflects the state of the

### LISTING 1—TRANSMITTER-PROGRAM FRAGMENT

|                          | 1        |               |                 |                   | *******                              |  |

|--------------------------|----------|---------------|-----------------|-------------------|--------------------------------------|--|

|                          | 2        |               |                 |                   | FRAGMENT *                           |  |

|                          | 4        |               |                 |                   |                                      |  |

|                          | 5        | * of da       | ata acco        | ording to         | the content of register REG.         |  |

|                          | 6        | *nclist       |                 | ********          | ************************************ |  |

| 0000                     | 8        |               |                 | -jla.asm"         |                                      |  |

|                          | 9        | *list         |                 | 5                 |                                      |  |

|                          | 10       |               | PORTS           |                   |                                      |  |

| 0000                     | 11       |               | ut equ          | 7 ;prti           | A                                    |  |

| 0000                     | 12<br>13 | * VAR.        | IABLES<br>org   | RAM               |                                      |  |

| 0000                     | 14       | REG           | rmb             |                   | put data register                    |  |

| 00C1                     | 15       | num           | rmb             |                   | test register                        |  |

|                          | 16       | * INI'        | FIALIZAT        | FION              | -                                    |  |

| 07F1                     | 17       |               |                 | (OR               |                                      |  |

| 07F1 00<br>0300          | 18<br>19 |               |                 | \$00<br>ROM       |                                      |  |

| 0300 9C                  | 20       | init          | org H<br>rsp    |                   | stack pointer to Sff                 |  |

| 0301 A680                | 21       | 11110         | lda             |                   | pA7 as output                        |  |

| 0303 8704                | 22       |               | sta             | ddrA              |                                      |  |

| 0305 3F00                | 23       |               | clr             | prtA              |                                      |  |

| 0307 3FC0                | 24       |               | clr             | REG               |                                      |  |

| 0309 3FC1                | 25       | * המתו        | clr             | num               |                                      |  |

| 030B AE7D                | 26<br>27 | * DATA        | ldx             |                   | UBROUTINE                            |  |

| 030D CD0335              | 28       |               | jsr             | #125T<br>pulse    | ;start pulse (1.25ms)                |  |

| 0310 A601                | 29       |               | lda             | #\$01             | ;0-bit test prepare                  |  |

| 0312 B7C1                | 30       |               | sta             | num               | , and and property                   |  |

| 0314 B6C0                | 31       | w1            | lda             | REG               | ; is tested bit = 0?                 |  |

| 0316 B4C1                | 32       |               | and             | num               |                                      |  |

| 0318 270B                | 33       |               | beq             | w2                |                                      |  |

| 031A AEAF<br>031C CD0335 | 34<br>35 |               | ldx             | #175T             | ;logic1 pulse (1.75ms)               |  |

| 031F 98                  | 36       | W3            | jsr<br>clc      | pu_se             | ;0 -> C-carry bit                    |  |

| 0320 38C1                | 37       |               | lsl             | านต               | ;go to next tested bit               |  |

| 0322 24F0                | 38       |               | bcc             | w1                | ; is it NOT a last bit?              |  |

| 0324 81                  | 39       |               | rts             |                   | from DATA TRANSMISSION               |  |

| 0325 AE4B                | 40       | w2            | ldx             | #75T              | ;log0 pulse (0.75ms)                 |  |

| 0327 CD0335              | 41       |               | jsr             | pulse             |                                      |  |

| 032A 20F3                | 42<br>43 | ******        | bra             | w3                | ****                                 |  |

| 032C A602                | 44       | dly01x        | lda             | #2                |                                      |  |

| 032E 4A                  | 45       | rep0          | decA            | #2                | ;Delay =0.01*x [ms]                  |  |

| 032F 26FD                | 46       | •             | bne             | rep0              |                                      |  |

| 0331 5A                  | 47       |               | decx            | -                 |                                      |  |

| 0332 26F8                | 48       |               | bne             | dly01x            |                                      |  |

| 0334 81                  | 49<br>50 | *****         | rts             |                   | ;return from dly01x                  |  |

| 0335 1E00                | 50<br>51 | pulse         | *******<br>bset |                   |                                      |  |

| 0335 1E00<br>0337 CD032C | 51       | purse         | jsr             | data_ou<br>dly01x | t,prtA ; width = x                   |  |

| 033A 1F00                | 53       |               | bclr            | data_ou           | it.prtA                              |  |

| 033C AE40                | 54       |               | ldx             | #64T              | · *                                  |  |

| 033E CD032C              | 55       |               | jsr             | dly01x            |                                      |  |

| 0341 81                  | 56       |               | rts             |                   | return from pulse                    |  |

| 0342 80                  | 57<br>58 | *******<br>un | *******<br>rti  |                   | *****                                |  |

| 07F8                     | 59       | un            |                 | VECTORS           | from unused interrupts               |  |

| 07F8 0342                | 60       |               | org<br>Edb      |                   | Timer Interrupt unused               |  |

| 07FA 0342                | 61       |               | fdb             |                   | External Interrupt unused            |  |

|                          | 62       |               | fdb             |                   | SWI unused                           |  |

| 07FC 0342<br>07FE 0300   | 63       |               |                 |                   |                                      |  |

Pulse-width ratios provide a convenient way to transmit serial data between  $\mu$ Cs lacking communications amenities.

# With the help of some $\mu C$ software, a simple one-wire connection provides serial communications between low-cost $\mu Cs.$

output data register. This pulse sequence goes, LSB-first, to the data-in input of the receiving  $\mu$ C. In the  $\mu$ C transmitter, you can use any output pin as data out. In the  $\mu$ C receiver, you can use any one of the four lower PortA pins (PA0 through PA3) as data in.

You should program the input pins as positive-edge, external-interrupt inputs. Because pins PAO to PA3 combine in a logic-OR operation in the  $\mu$ C, you should connect the unused pins to ground to avoid false interruption. You should disable the  $\overline{IRQ}$  pin by connecting it to 5V. The external-interrupt subroutine (**Listing 2**) restores the data word, which can generate the proper response according to your design objectives. **Listing 3** shows a fragment of the receiver routine. The program's watchdog utility lights a red LED to indicate that the communication link between the  $\mu$ Cs is broken or that it received the wrong sequence. The method also applies to

wireless applications with minor modifications. You can download the complete **listings** from *EDN*'s Web site, www.ednmag.com. At the registered-user area, go into the Software Center to download the files from DI-SIG, #2265. (DI #2265).

#### To Vote For This Design, Circle No. 349

### LISTING 2—EXTERNAL-INTERRUPT SUBROUTINE

| ART10.ASM              |          | Assemb           | led with       | n IASM 04/      | 09/1998 11:26 PAGE 2       |

|------------------------|----------|------------------|----------------|-----------------|----------------------------|

|                        |          |                  |                |                 |                            |

|                        | 57       |                  |                | ERRUPT SUBRO    | UTINE                      |

| 032E 3FC1              | 58       | ExtInt:          |                | Т               |                            |

| 0330 3FC0              | 59       |                  | clr            | W               | -1 Wigh level 0            |

| 0332 000011            | 60       | e0               | brset<br>brclr | WF,flag,e2      | el ;High lovel ?           |

| 0335 01C31C            | 61<br>62 |                  | lda            | WF,IIdg,Ez<br>W | 7 W2 # 0 ?                 |

| 0338 B6C0              | 63       |                  |                | W<br>#1         | ; W=1 ?                    |

| 033A A101<br>033C 2724 | 64       |                  | cmp<br>beq     | 10q0            | ,                          |

| 033C 2724<br>033E A103 | 65       |                  | cmp            | #3              | ; W=3?                     |

| 0340 2728              | 66       |                  | bea            | Log1            | ,                          |

| 0342 11C3              | 67       |                  | bclr           | WF, flag        | ;0 -> WF                   |

| 0344 2041              | 68       |                  | bra            | e3              | , -                        |

| 0346 3CC1              | 69       | el               | inc            | T               |                            |

| 0348 B6C1              | 70       |                  | lda            | T               |                            |

| 034A A137              | 71       |                  | Cmp            | #55T            |                            |

| 034C 26E4              | 72       |                  | bne            | e0              |                            |

| 034E 3FC1              | 73       |                  | clr            | Т               |                            |

| 0350 3CC0              | 74       |                  | inc            | ы               |                            |

| 0352 20DE              | 75       |                  | bra            | e0              |                            |

| 0354 B6C0              | 76       | e2               | lda            | W               |                            |

| 0356 A102              | 77       |                  | cmp            | #2              | ; W=2?                     |

| 0358 262D              | 78       |                  | bne            | e3              |                            |

| 035A 10C3              | 79       |                  | bset           | WF,flag         | ;1 -> WF                   |

| 035C A6FE              | 80       |                  | lda            | #\$fe           | ;0 -> 0-bit of num         |

| 035E B7C4              | 81       |                  | sta            | num             |                            |

| 0360 2025              | 82       |                  | bra            | e3              |                            |

| 0362 B6C5              | 83       | log0             | lda            | reg             | ,put 0 into given bit of   |

| 0364 B4C4              | 84       |                  | and            | num             | ;reg. without changing     |

| 0366 B7C5              | 85       |                  | sta            | reg             | ;of the rest of its bits.  |

| 0368 200C              | 86       | 1 1              | bra<br>1da     | e4              | ;put 1 into given bit of   |

| 036A B6C4              | 87<br>88 | log1             | sta            | num<br>mem      | ;req. without changing     |

| 036C B7C6<br>036E B4C5 | 89       |                  | and            |                 | of the rest of its bits    |

| 0370 3306              | 90       |                  | COM            | reg<br>mem      | JOI THE TEST OF ITS DICS   |

| 0370 33C6<br>0372 B8C6 | 91       |                  | eor            | men             |                            |

| 0374 B7C5              | 92       |                  | sta            | req             |                            |

| 0376 99                | 93       | e4               | sec            | 109             | ;1 -> Carry bit            |

| 0377 3904              | 94       | ~ <del>.</del> . | rol            | num             | ;go to the next bit        |

| 0379 250C              | 95       |                  | bcs            | e3              | is it NOT the last bit?    |

| 0378 1103              | 96       |                  | bclr           | WF,flag         | ;0 -> WF word process flag |

| 0370 17C3              | 97       |                  | bclr           | WDF, flag       | ,                          |

|                        |          | *****            |                |                 | ******                     |

### LISTING 3—RECEIVER-PROGRAM FRAGMENT

|                          | 1        | * RECEIVER PROGRAM FRAGMENT             |                     |                       |                                                                                                                |  |  |  |

|--------------------------|----------|-----------------------------------------|---------------------|-----------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

|                          | 4        | * RECEIVER FROGRAM FRAGMENT             |                     |                       |                                                                                                                |  |  |  |

|                          | 4        | * Transfers the received serial data    |                     |                       |                                                                                                                |  |  |  |

|                          | ŝ        | * into content of the register WORD.    |                     |                       |                                                                                                                |  |  |  |

|                          | 6        | *************************************** |                     |                       |                                                                                                                |  |  |  |

|                          | 7        | *nolist                                 |                     |                       |                                                                                                                |  |  |  |

| 0000                     | 8        | \$include "std-jla.asm"                 |                     |                       |                                                                                                                |  |  |  |

|                          | 9        | *list                                   | MOT                 |                       | Test Test comments                                                                                             |  |  |  |

| 07F1                     | 10       |                                         | org MOR<br>fcb \$24 |                       | Ext.Interrupt<br>- pA3 enable                                                                                  |  |  |  |

| 07F1 24                  | 11<br>12 | *I/0 PO                                 |                     | ; on pao              | - pas enabre                                                                                                   |  |  |  |

| 07F2                     | 13       |                                         |                     | ;prtA Data            | fucut pin                                                                                                      |  |  |  |

| 07F2                     | 14       | RedLED                                  |                     |                       | ED output pin                                                                                                  |  |  |  |

| 0.112                    | 15       |                                         | ic equat            |                       |                                                                                                                |  |  |  |

| 0782                     | 16       | WF                                      |                     | ;Word proces          |                                                                                                                |  |  |  |

| 07F2                     | 17       | F1                                      | equ 1               | ;signal pres          |                                                                                                                |  |  |  |

| 07F2                     | 18       |                                         | equ 3               | ;watch-dog :          | Elag                                                                                                           |  |  |  |

|                          | 19       | * VARIA                                 |                     |                       |                                                                                                                |  |  |  |

| 0000                     | 20       |                                         | org                 | RAM                   | and a second |  |  |  |

| 0000                     | 21<br>22 | W<br>T                                  | rmb                 |                       | idth counter<br>.5 ms) counter                                                                                 |  |  |  |

| 00C1                     | 22       | udc                                     | rmb                 | 1 ;watch-de           |                                                                                                                |  |  |  |

| 00C2<br>00C3             | 23       | flag                                    | rmb                 | 1 ;flag red           |                                                                                                                |  |  |  |

| 00C4                     | 25       | num                                     | rmb                 |                       | r to form word                                                                                                 |  |  |  |

| 0005                     | 26       | rea                                     | rmb                 |                       | ry word register.                                                                                              |  |  |  |

| 0006                     | 27       | mem                                     | 1-mb                | 1 ;memory :           | register                                                                                                       |  |  |  |

| 0007                     | 28       | WORD                                    | r mb                |                       | eceived word register.                                                                                         |  |  |  |

|                          | 29       | * INITI                                 | ALIZATIC            |                       |                                                                                                                |  |  |  |

| 0300                     | 30       |                                         | org                 | ROM                   |                                                                                                                |  |  |  |

| 0300 9C                  | 31       | init                                    | rsp                 |                       | set stack pointer to \$ff                                                                                      |  |  |  |

| 0301 A6F0                | 32       |                                         | lda<br>sta          | #\$£0<br>ddrA         | pA0 - pA3 as input;<br>pA4 - pA7 as output                                                                     |  |  |  |

| 0303 B704<br>0305 CD0318 | 33<br>34 |                                         | isr                 | in set                | ;go to initial set                                                                                             |  |  |  |

| 0305 CD0318<br>0308 1E0A | 35       |                                         | bset                | IROE, ISCR            | ;ExtInt enable                                                                                                 |  |  |  |

| 030A 1A08                | 36       |                                         | bset                | TOIE, TSCR            | TOF interrupt enable                                                                                           |  |  |  |

| 030C 9A                  | 37       |                                         | cli                 |                       | interrupt enable                                                                                               |  |  |  |

| 030D 06C303              | 38       | mO                                      | brset               | WDF, flag, m          | 1 ;WDF=1? No data-in?                                                                                          |  |  |  |

| 0310 00C3FA              | 39       |                                         | brset               | WF,flag,m0            | ;WF=1? wait for word end                                                                                       |  |  |  |

| 0313 CD0318              | 40       | ml                                      | jar                 | in_set                |                                                                                                                |  |  |  |

| 0316 20F5                | 41       |                                         | bra                 | m0 <sup></sup>        |                                                                                                                |  |  |  |

|                          | 42       |                                         |                     |                       | ***********************************                                                                            |  |  |  |

| 0318 3F00                | 43<br>44 | in_set                                  | clr<br>clrx         | prtA                  | ;set red LED on<br>;start to clear                                                                             |  |  |  |

| 031A 5F<br>031B 6FC0     | 45       | a0                                      | clr                 | RAM, x                | ; 8 variables in RAM                                                                                           |  |  |  |

| 031D 5C                  | 46       | av                                      | incx                | IG # 17 M             | ,                                                                                                              |  |  |  |

| 031E A308                | 47       |                                         | срх                 | #8T                   |                                                                                                                |  |  |  |

| 0320 25F9                | 48       |                                         | blo                 | a0                    |                                                                                                                |  |  |  |

| 0322 81                  | 49       |                                         | rts                 |                       | ;return from in_set                                                                                            |  |  |  |

|                          | 50       | ******                                  | *******             |                       | ****************                                                                                               |  |  |  |

| 0323 3CC2                | 51       | TOFint                                  | inc                 | wdc                   |                                                                                                                |  |  |  |

| 0325 3DC2                | 52       |                                         | tst                 | wdc                   | ;wdc / 0 ?                                                                                                     |  |  |  |

| 0327 2602                | 53       |                                         | bne                 | t0                    | ;1 -> WDF                                                                                                      |  |  |  |

| 0329 16C3                | 54<br>55 | - 0                                     | bset<br>bset        | WDF,flag<br>TOFR.TSCR | TOP reset                                                                                                      |  |  |  |

| 032B 1608<br>032D 80     | 55       | t0                                      | pset<br>rti         | TOLK, TOCK            | return from TOFint                                                                                             |  |  |  |

| ADSD OA                  | 20       |                                         |                     |                       | ,                                                                                                              |  |  |  |

|                          |          |                                         |                     |                       |                                                                                                                |  |  |  |

|                          |          |                                         |                     |                       |                                                                                                                |  |  |  |

|                          |          |                                         |                     |                       |                                                                                                                |  |  |  |

|                          |          |                                         |                     |                       |                                                                                                                |  |  |  |

|                          |          |                                         |                     |                       |                                                                                                                |  |  |  |