### The National Semiconductor Linear Seminar

#### Forward

National Semiconductor has long been regarded as the industry's Linear Leader. The breadth of our product line is unequaled, and we have developed more industry-standard linear products and processes than any other manufacturer in the world.

The Linear Seminar will focus on solutions to your applications problems and introduce you to our latest products. The range of linear solutions that National offers is constantly expanding, and this Seminar will help bring you up-to-date with our most current offerings. The three volume, 3200 page Linear Databook contains complete specifications for over 500 different items, many with several members to a family, and over 100 new products since our last publication at the time of the 1987 Linear Seminar. It should prove to be an invaluable reference for all of your linear designs.

There is more to the Linear Seminar than simply providing information about our products. Since many of our key products are the result of customer inputs, we value the opportunity to talk with you directly about what we are doing and to understand your future needs.

Graham Baskerville Director of Linear Design National Semiconductor Corporation

#### The National Semiconductor Linear Seminal

#### Diswin F

Vational Semiconductor has leng been regarded as the initiatry's Linear Leaded. The creation of our product time is unequaled, and we have developed more industry stringed linear products and processes their any other menufacturar in the work.

The Linear Symbols will focus on solutions to your applications problems and introduce you a our latest products. The range of linear solutions that National offers is constantly reparding, and this Saminar will help oring you up to date with our most current offerings. The finite volume, 3200 page Linear Desbook contains complete specifications for over 300 offerent term, many with several members to a family, and over 100 new products arose our last gublication at the one of the 1907 Linear Seminar. It chould prove to he and another be an an or way the several members to a family. And over 100 new products arose our last gublication at the one of the 1907 Linear Seminar. It chould prove to he an available reference for all of your linear designs.

here is store to the Europe details of the simply providing information about our problem. Since means of our lines products are the mean of discorner inputs, we value fits opportuning to this with you discuty foods what we are doing and to understand your future needs.

minam Batherville rector nt Linear Design sticmat Stimiconductor Connection

## Contents

| Section 1: OPERATIONAL AMPLIFIERS1-1Current Feedback vs. Voltage Feedback1-2VIP AMPLIFIERS1-8LM6313, LF400, DAC1020 & LM369 High Speed Power Supply1-9LM6313 3-Pole Low Pass Filter1-10LM6118 Dual High-Speed Op Amp1-12LM6218 60 kHz High Q Bandpass Filter1-13PRECISION AMPLIFIERS1-14LM607 Precision Op Amp1-15LM627 & LM637 Fast, Precision Op Amps1-16LM627 Remote Transmitter1-18LM627 Remote Transmitter1-19CMOS Op Amps Piezo or Pyroelectric Amplifiers1-20SUPER-BLOCK™ Combinations1-29Selection Guide and General Description1-31Supply Current Sink1-334-to-20 mA Current Sink1-33Ambient Temperature Monitor1-43Temperature Sensor Background1-45 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 2: MODELING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

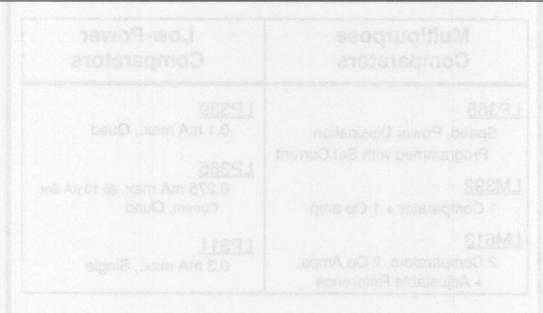

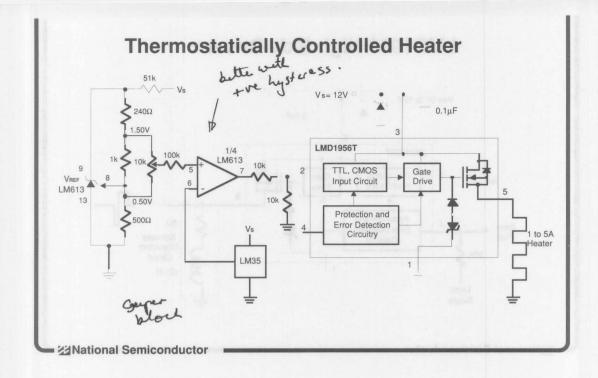

| Section 3: COMPARATORS3-1Selection Guide3-3Response Time Adds Error3-5LM393 Response Time3-6LM311 Response Time3-7LM360 Response Time3-7LM360 Response Time3-7LM360 Response Time3-8Comparator Input Voltage Range3-10Differential Input Voltage Rating3-11LM311 Sensitivity3-12LM339 Sensitivity3-13Hysteresis Improves Switching3-14Use of Op Amp as Comparator3-16LM1946 Load Current Monitor3-18LM613 SUPER-BLOCK™3-20Multipurpose and Low Power Comparators3-21                                                                                                                                                                                           |

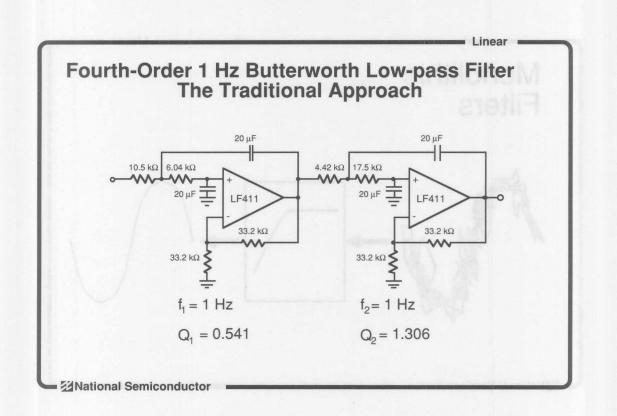

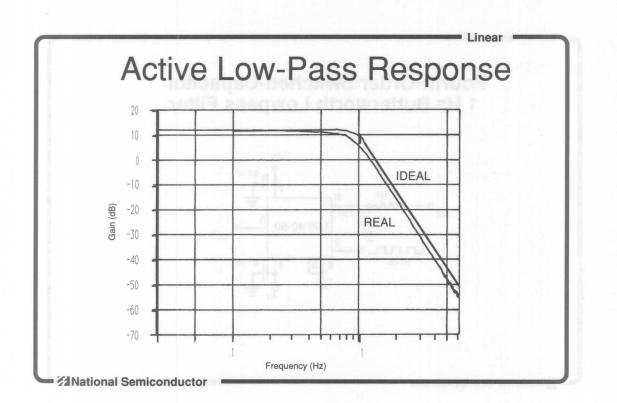

| Section 4: MONOLITHIC FILTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### Section 4: MONOLITHIC FILTERS (continued)

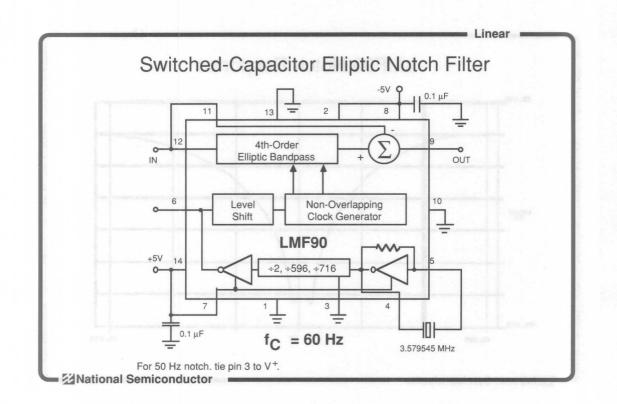

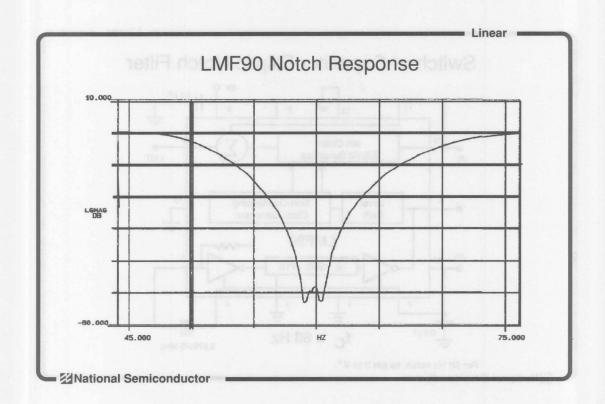

| LMF90 Switched-Capacitor Notch Filter                |  |

|------------------------------------------------------|--|

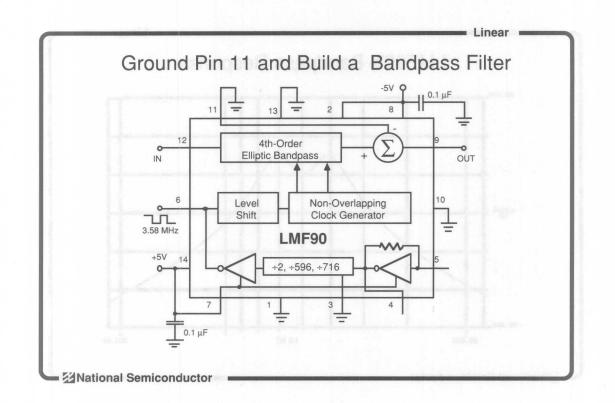

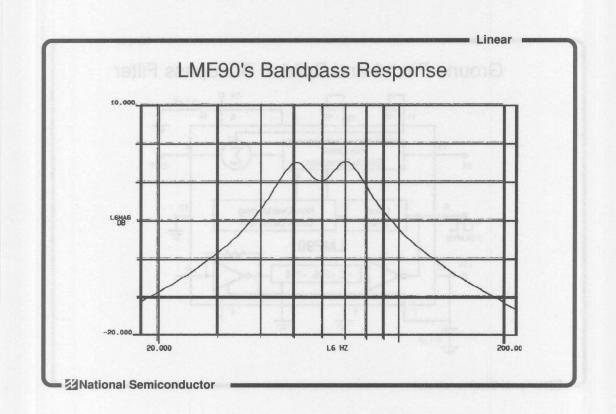

| LMF90 Bandpass Application                           |  |

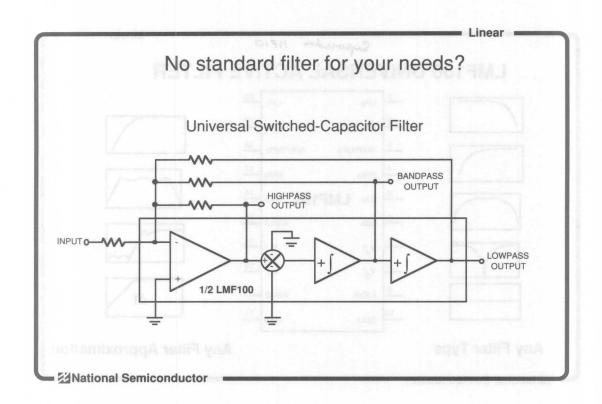

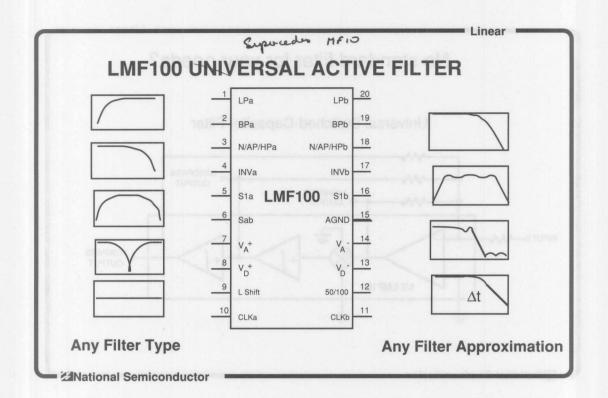

| Universal Filters                                    |  |

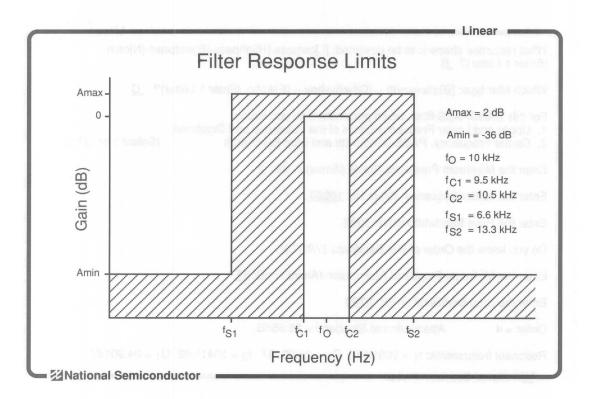

| LMF100 Computer-Aided Design Example                 |  |

| Active Filter Design Hints                           |  |

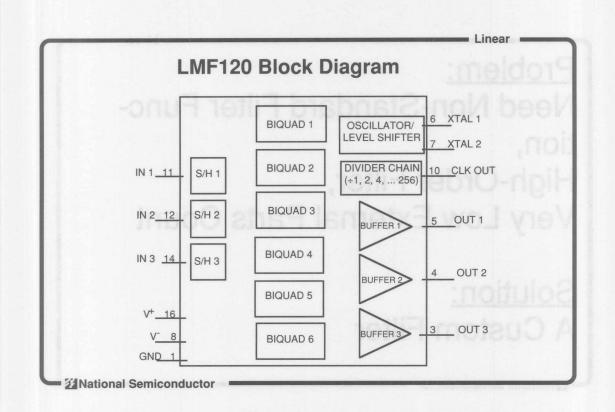

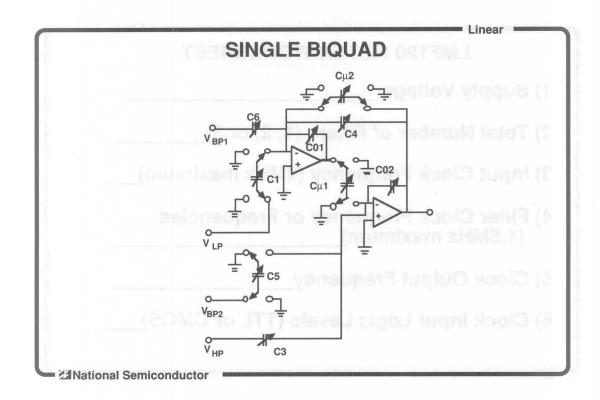

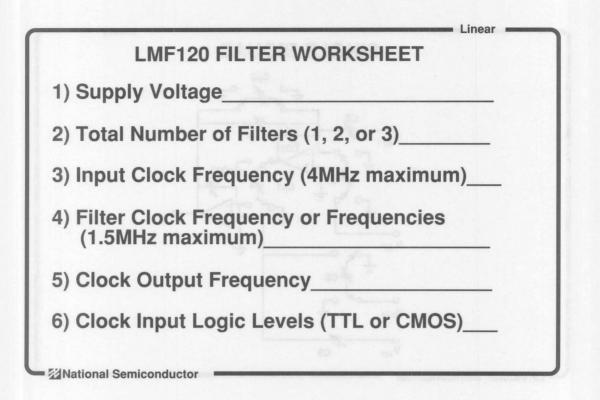

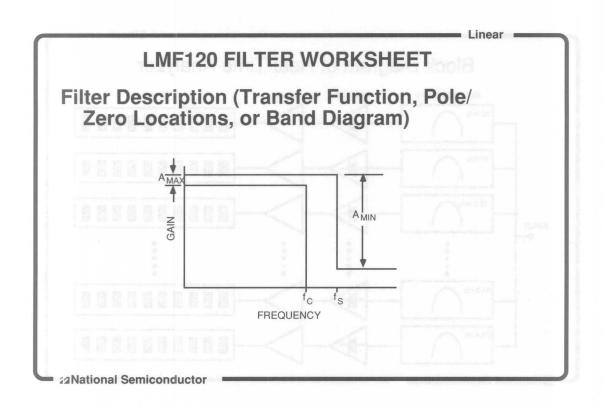

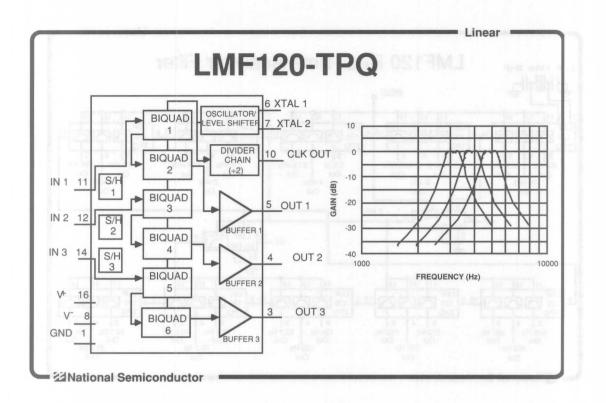

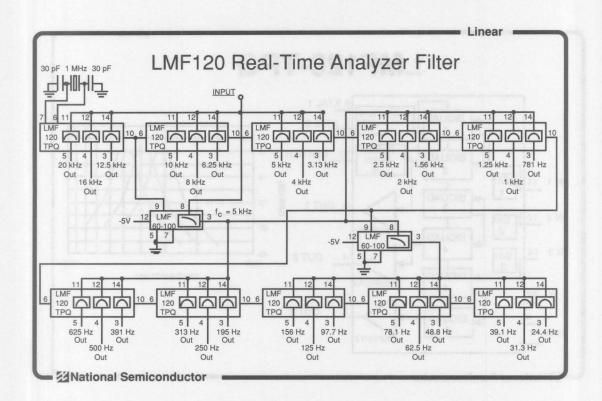

| LMF120 Custom 12th-Order Universal Monolithic Filter |  |

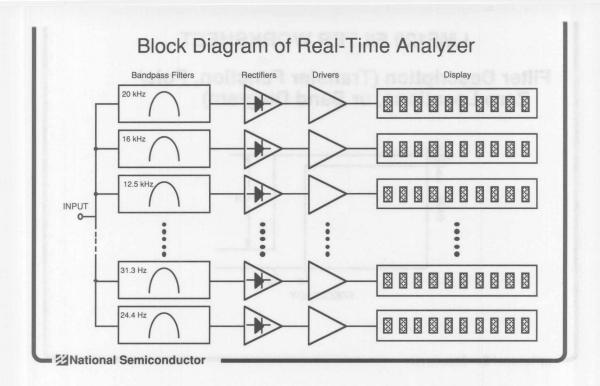

| LMF120 Realtime Analyzer                             |  |

####

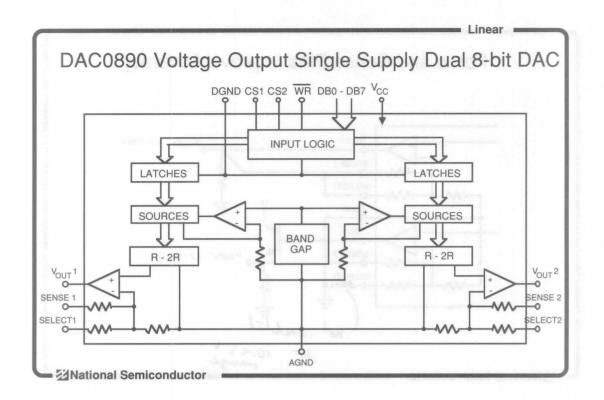

| Digital-to-Analog Conversion on +5V             |      |

|-------------------------------------------------|------|

| DAC0890 Complete +5V Dual DAC                   |      |

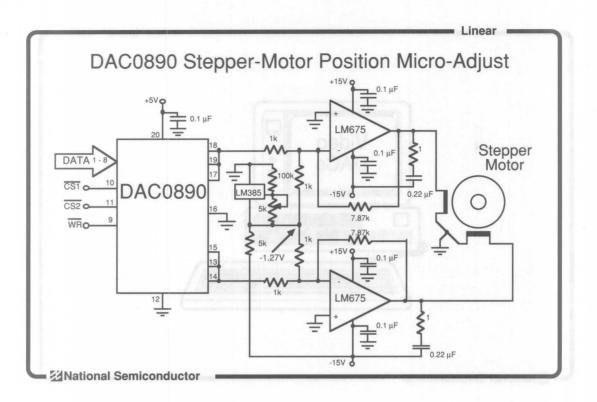

| DAC0890 Stepper Motor Micro-Adjust              |      |

| Video DACs                                      |      |

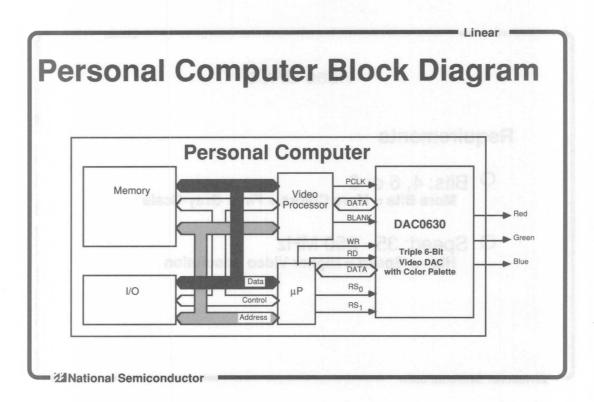

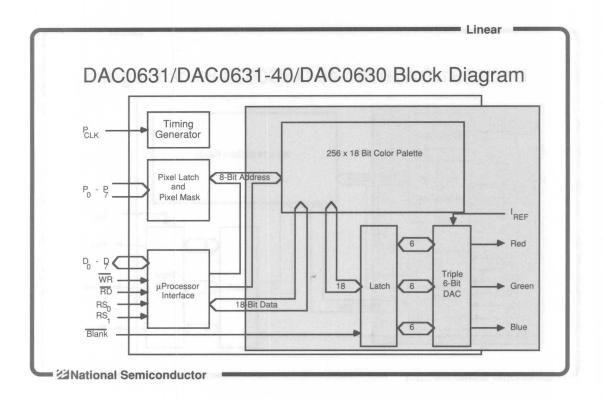

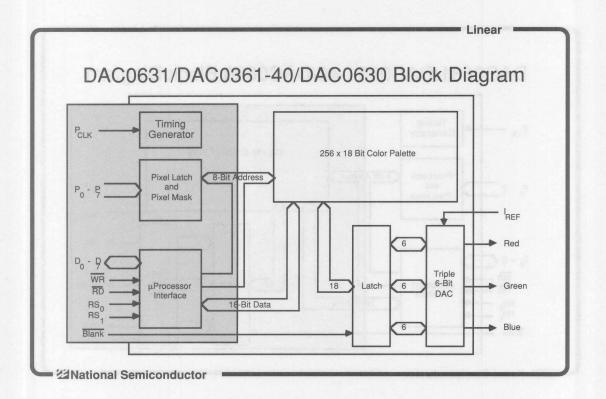

| DAC0630/DAC0631 Video DAC Block Diagram         |      |

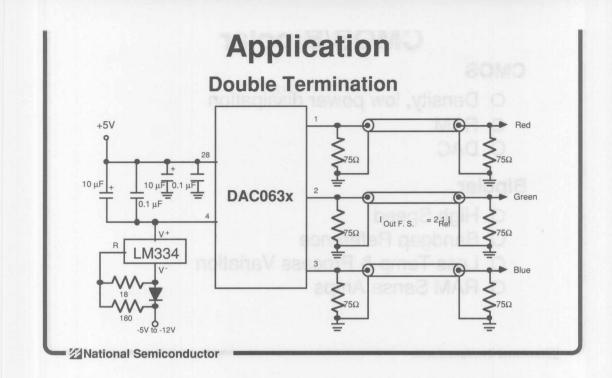

| Video DAC Application Circuit                   |      |

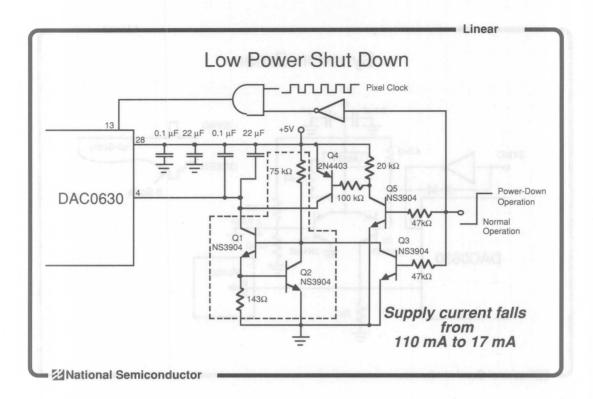

| DAC0630 Low-Power Shutdown For Laptop Computers |      |

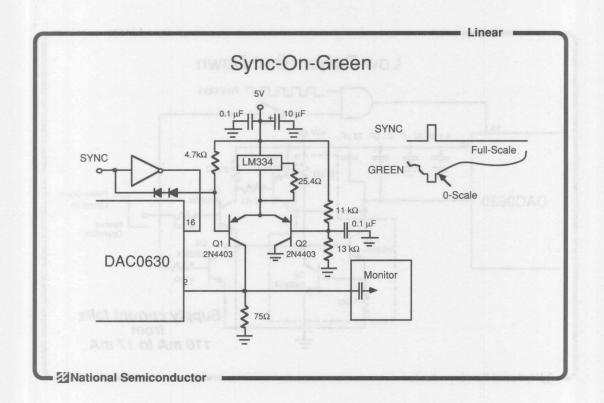

| DAC0630 with Sync on Green                      | 5-16 |

| Section 6: ANALOG-TO-DIGITAL CONVERTERS                 |      |

|---------------------------------------------------------|------|

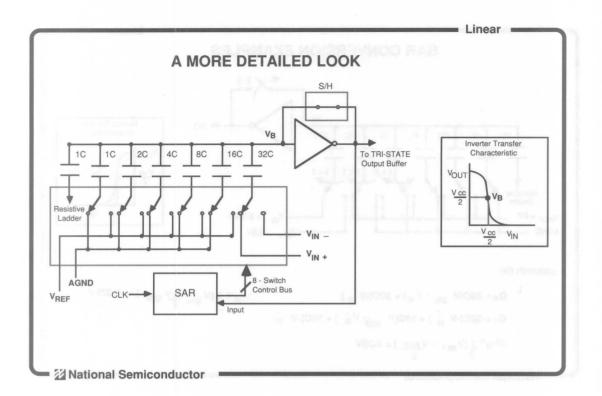

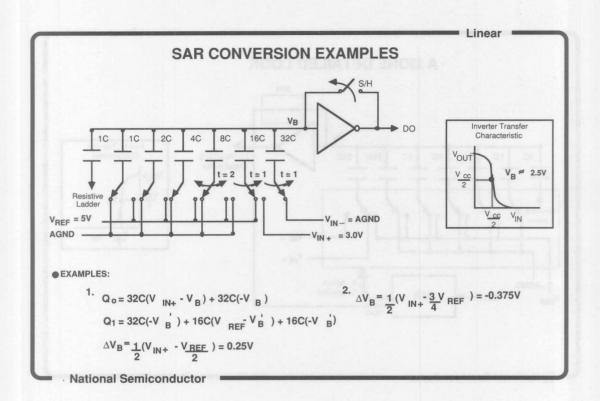

| Successive Approximation                                | 6-2  |

| Serial A/D Converters                                   |      |

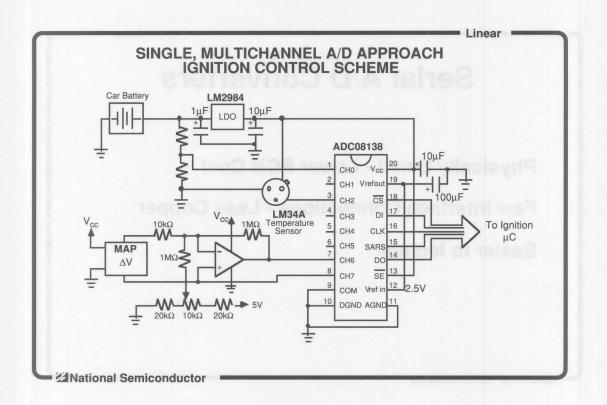

| ADC08138 in Engine Control System                       | 6-6  |

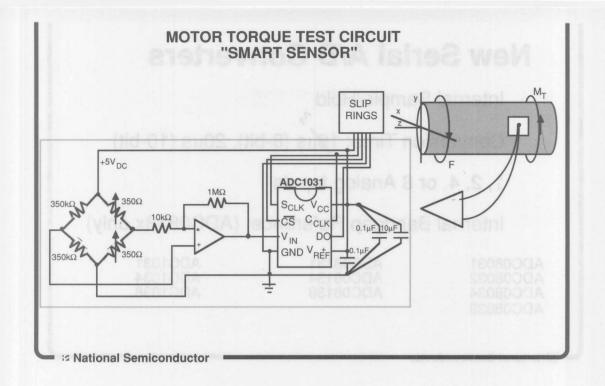

| ADC1031 in Motor Torque Digitizer                       | 6-7  |

| New Serial A/D Converter Families                       | 6-8  |

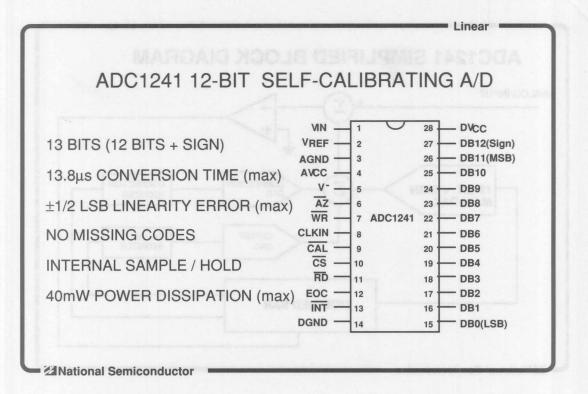

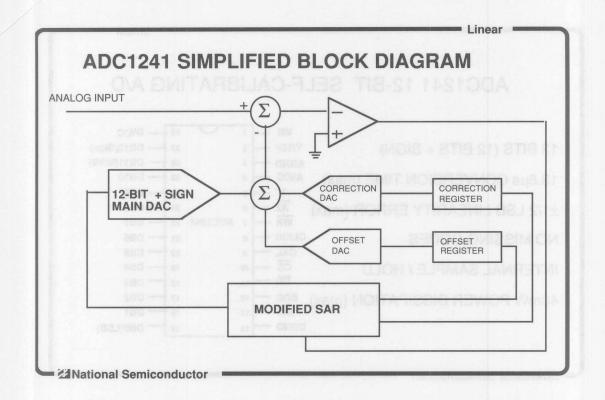

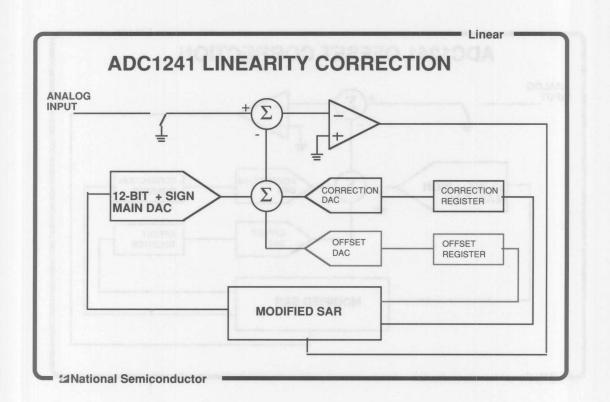

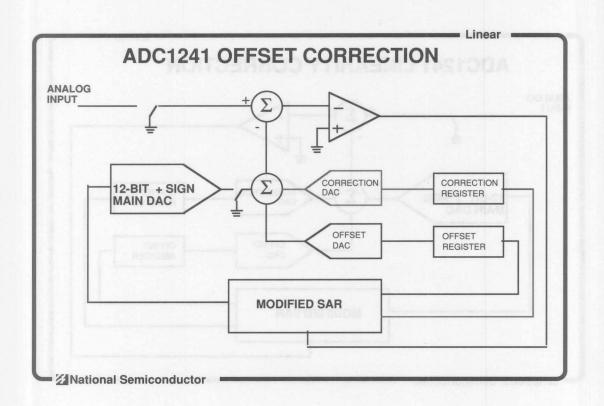

| ADC1241 12-Bit (Plus Sign)Self-Calibrated A/D Converter | 6-9  |

| ADC1241 Auto-Zero and Self-Calibration                  | 6-11 |

| Voltage References for Data Acquisition                 | 6-13 |

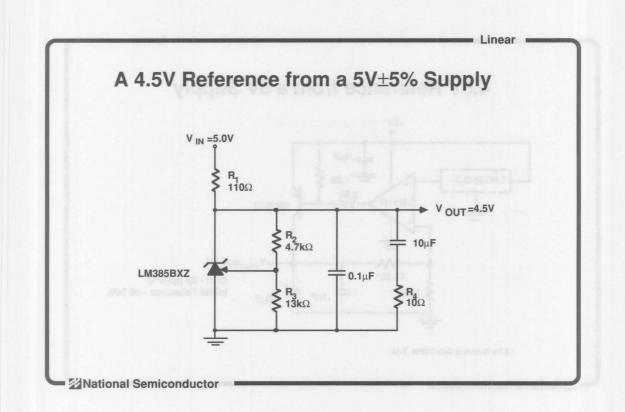

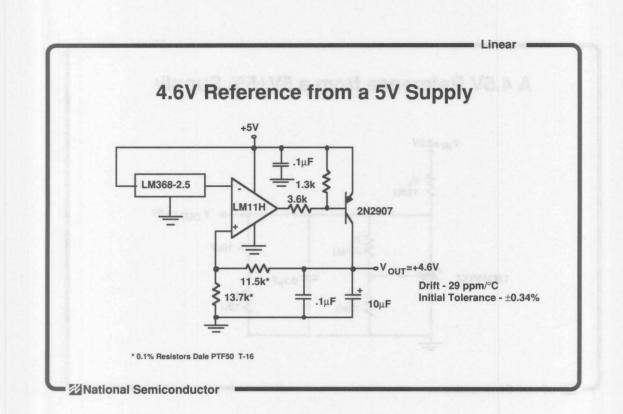

| 4.5V References on 5V Supplies                          | 6-15 |

| Reference Span Adjustment                               | 6-17 |

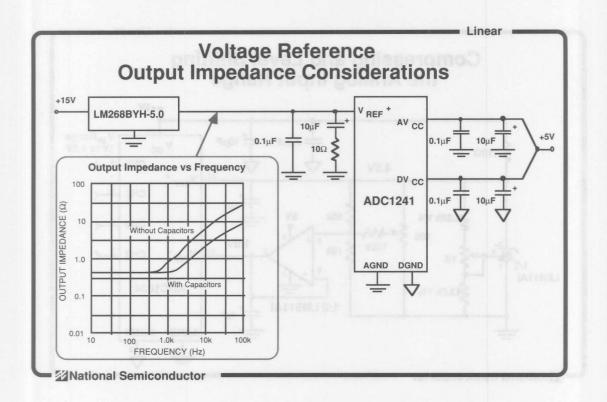

| Reference Output Impedance                              | 6-18 |

| Bits vs Reference Accuracy                              | 6-20 |

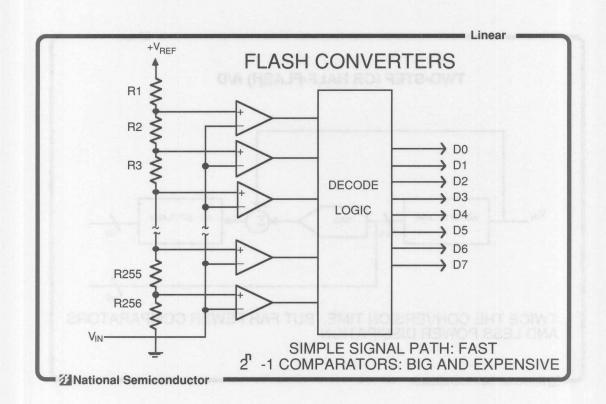

| Flash A/D Converters                                    | 6-21 |

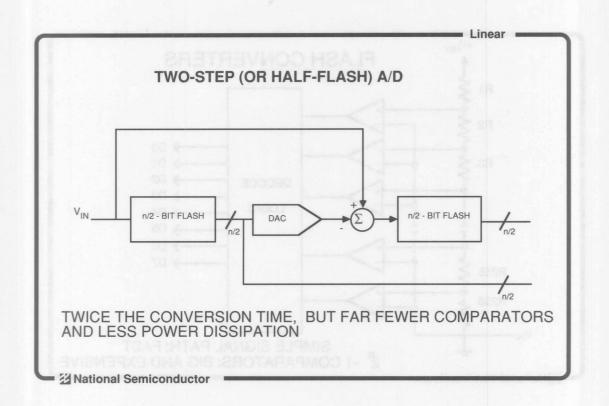

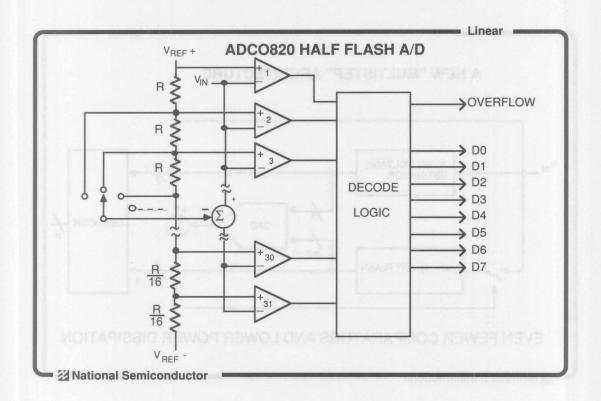

| Two-Step High-Speed A/D Converters: ADC0820             | 6-22 |

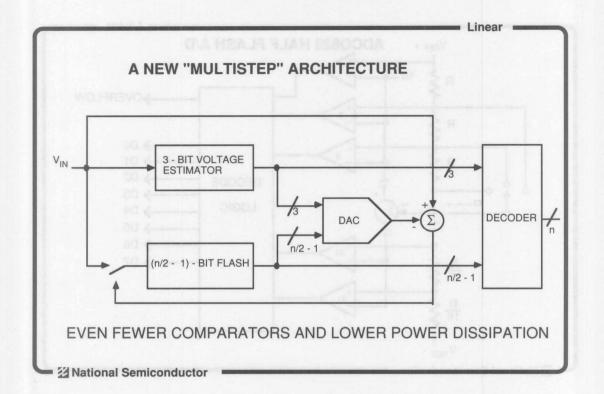

| Multistep A/D Converters                                | 6-24 |

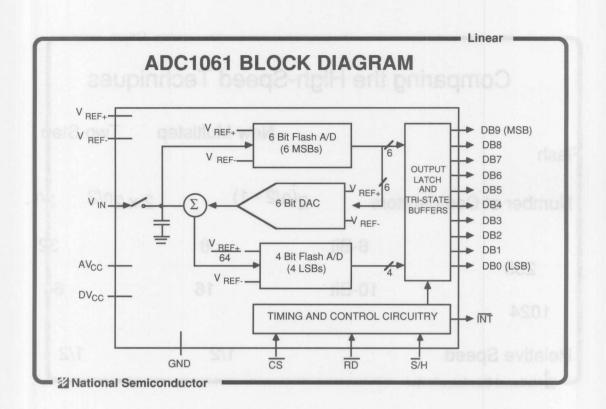

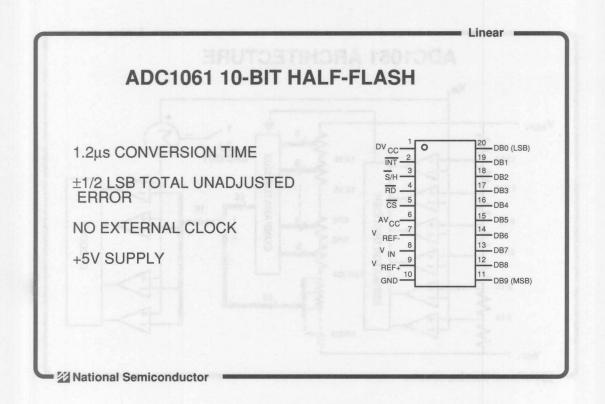

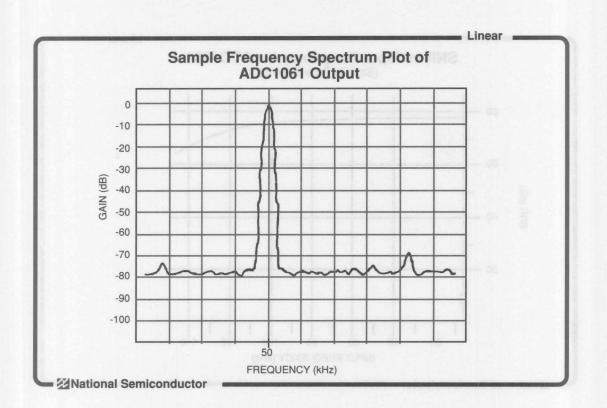

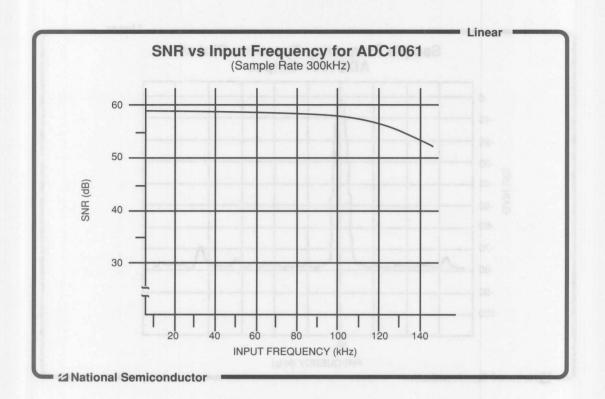

| ADC1061 Multistep High-Speed A/D Converter              | 6-26 |

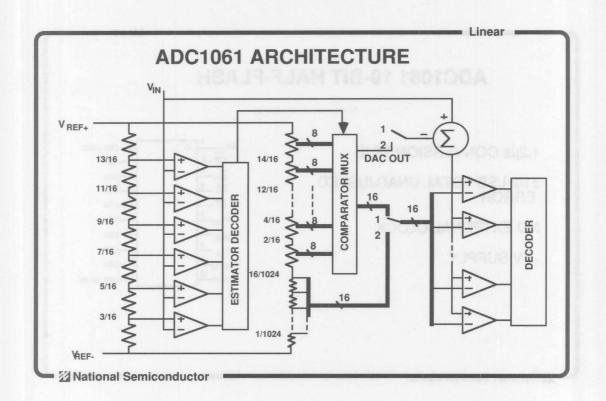

| ADC1061 Architecture                                    | 6-27 |

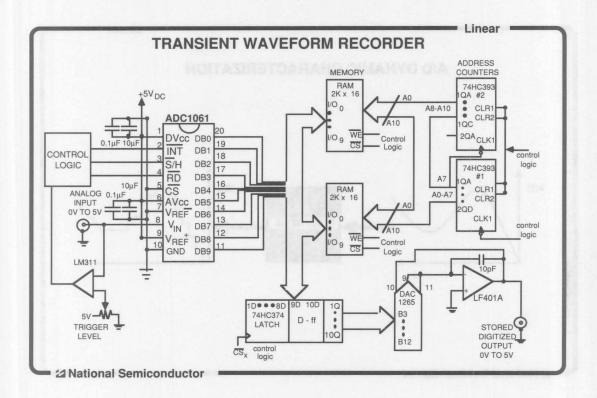

| ADC1061 Waveform Digitizer/Recorder                     | 6-29 |

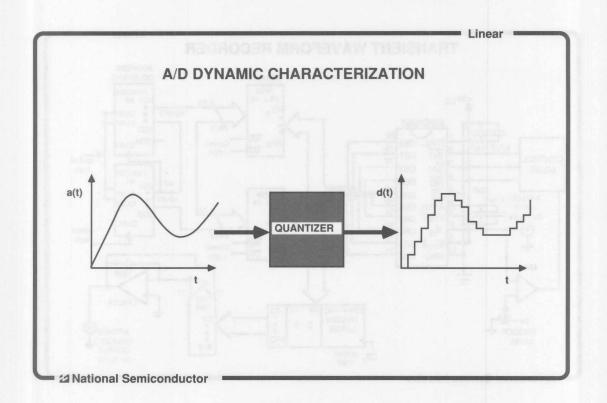

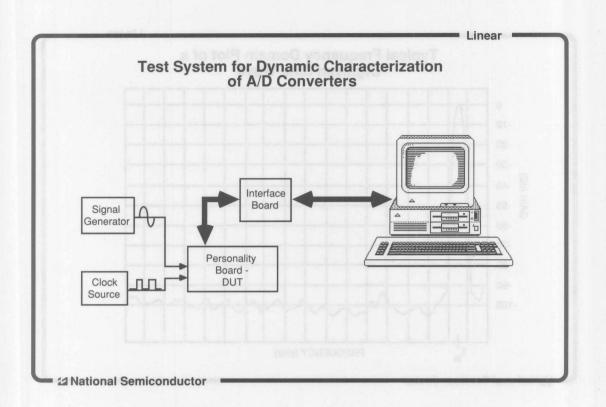

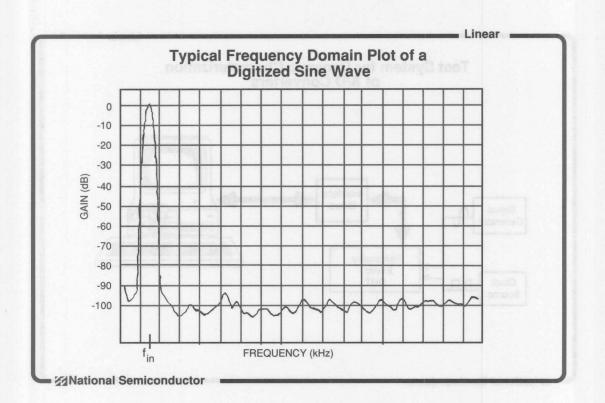

| Dynamic Testing of A/D Converters                       | 6-30 |

| and I nu Power Comparators                              |      |

| Section 7: AUDIO                            |     |

|---------------------------------------------|-----|

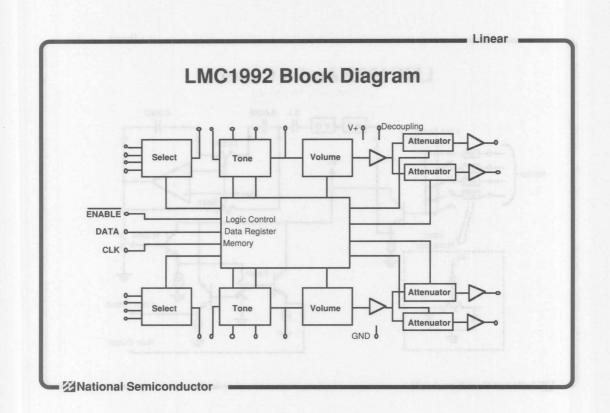

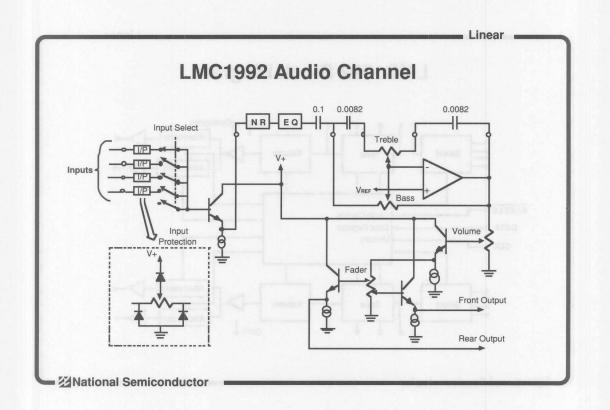

| LMC1992 Audio Processor                     |     |

| Digital Control of the LMC1992              | 7-5 |

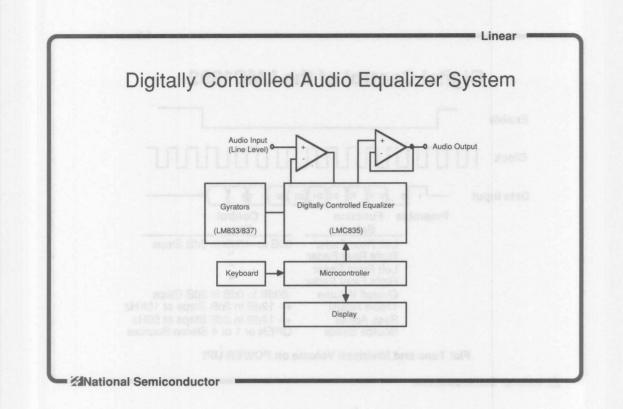

| LMC835 Digitally Controlled Audio Equalizer | 7-6 |

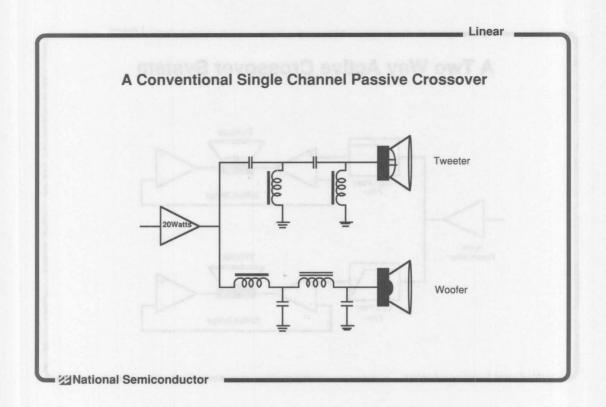

| Conventional Passive Crossover Network      | 7-7 |

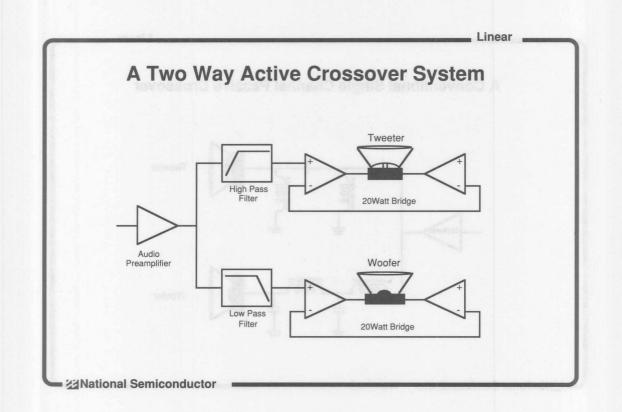

| Active Crossover Concept                    | 7-8 |

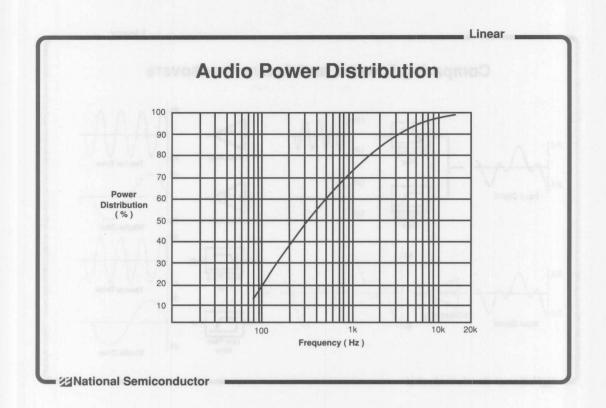

| Audio Power Distribution                    | 7-9 |

| Section 7: AUDIO (continued)                         |      |

|------------------------------------------------------|------|

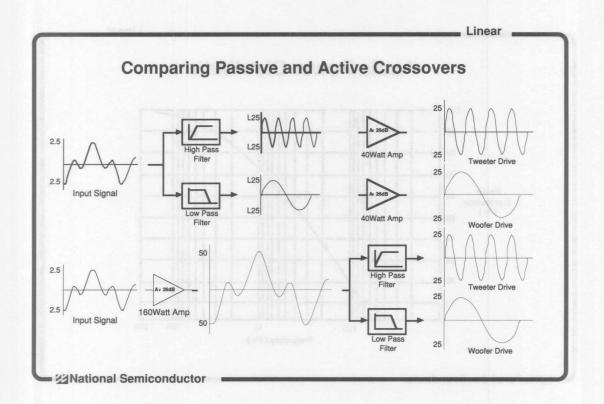

| Passive vs. Active Crossover Requirements            | 7-10 |

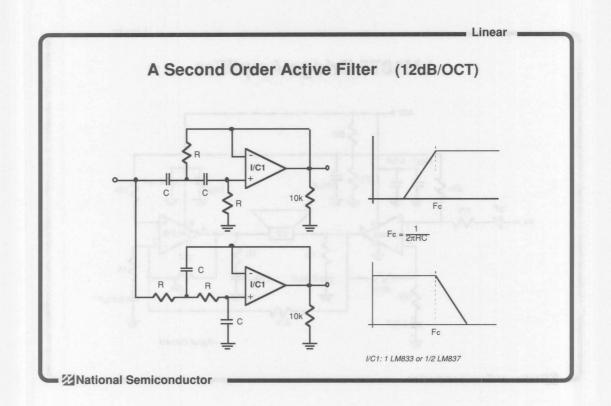

| 2nd Order Active Crossover Filters                   |      |

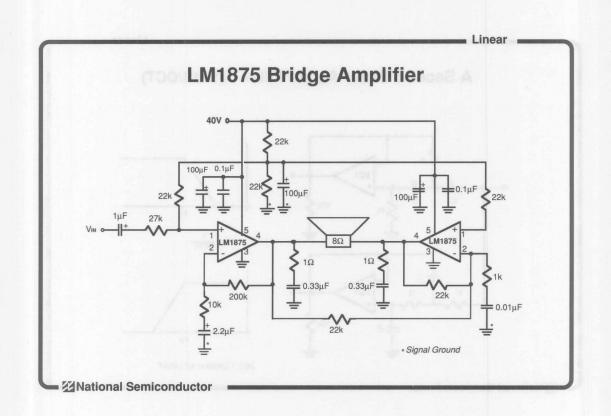

| LM1875 40W Bridge Amplifier                          |      |

|                                                      |      |

| Section 8: VIDEO                                     | 0.4  |

|                                                      |      |

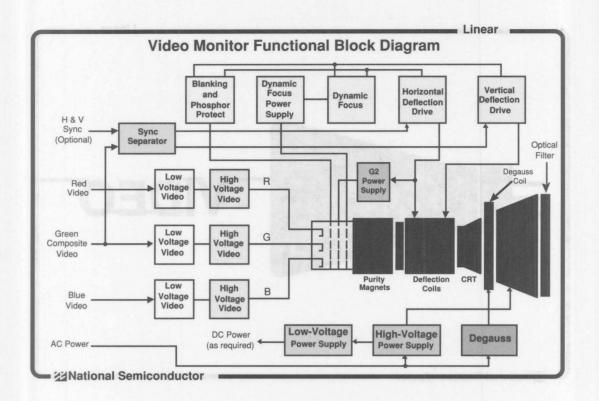

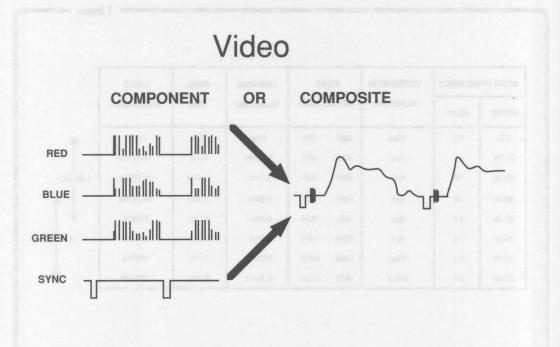

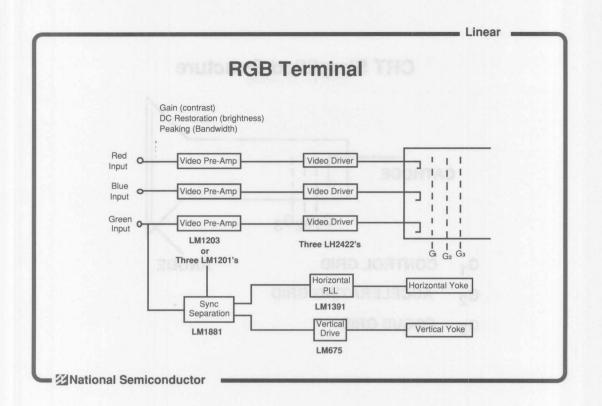

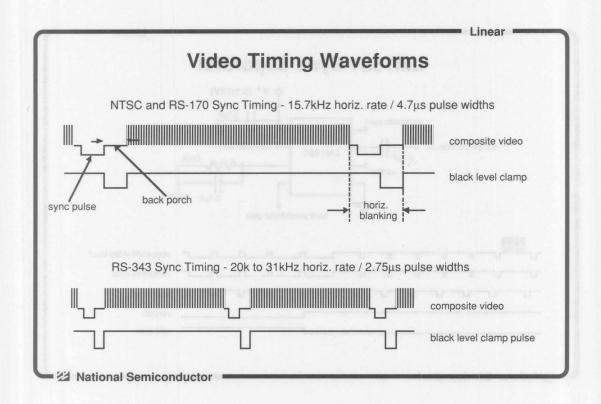

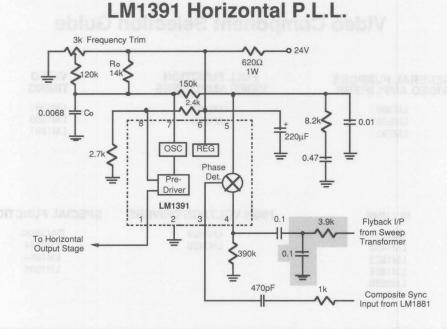

| Video Monitor Block Diagram                          | .8-2 |

| Video Scan Frequencies, Resolution, and Bandwidth    |      |

| RGB Terminal Block Diagram                           |      |

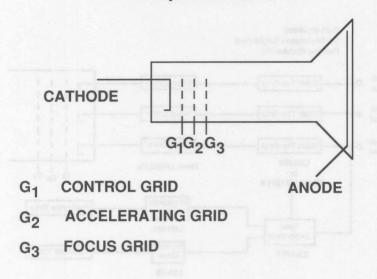

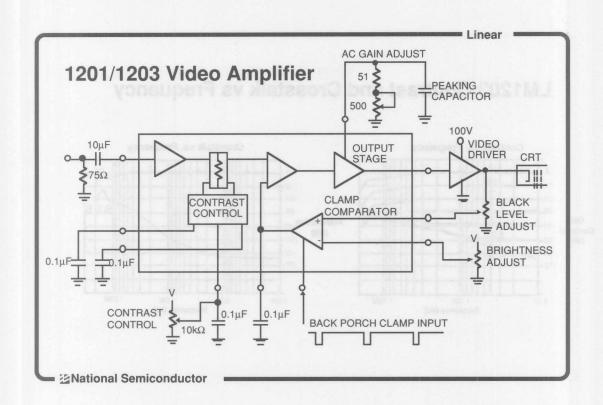

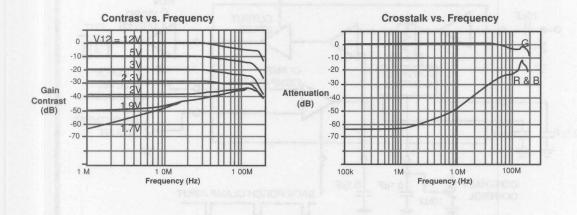

| CRT Basics<br>LM1201/1203 Video Amplifier            | 0-0  |

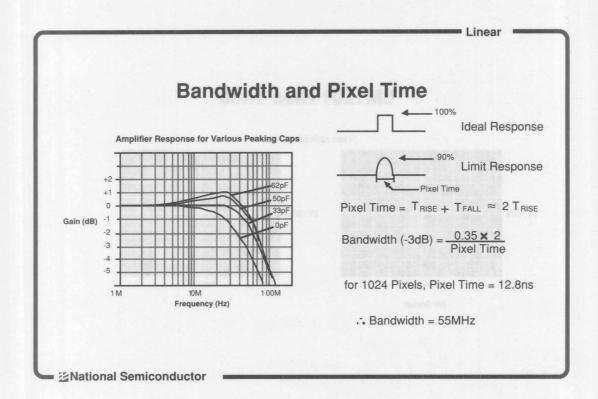

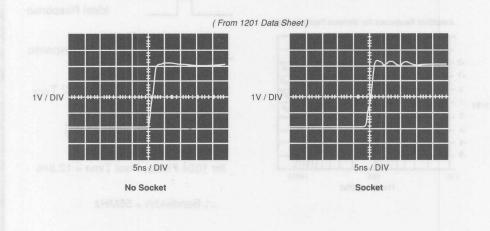

| Pixel Time and Required Bandwidth                    |      |

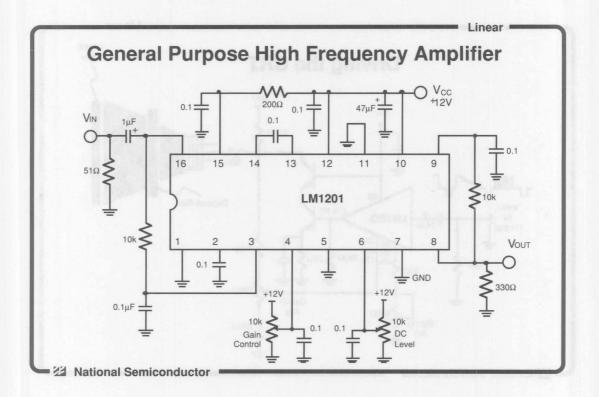

| General Purpose High Frequency Amplifier             | 0 10 |

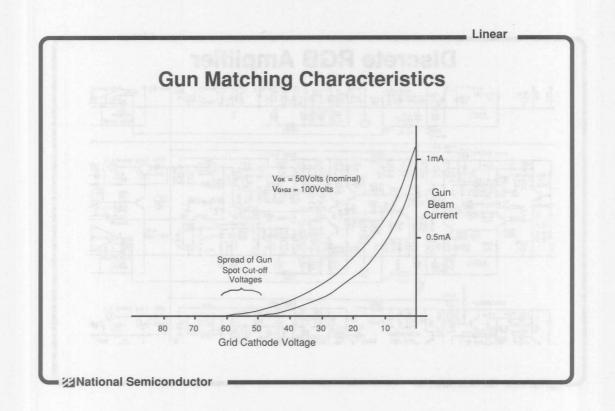

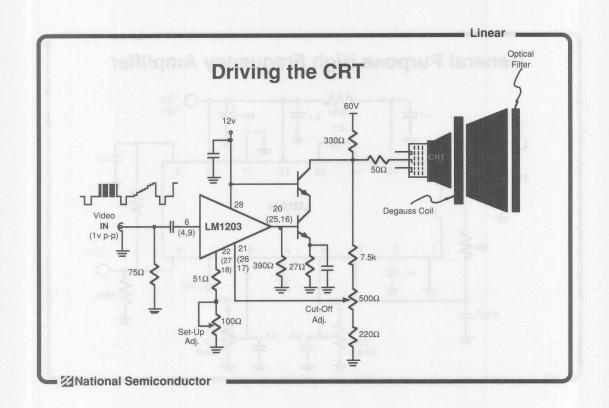

| Driving CRTs                                         | 8-11 |

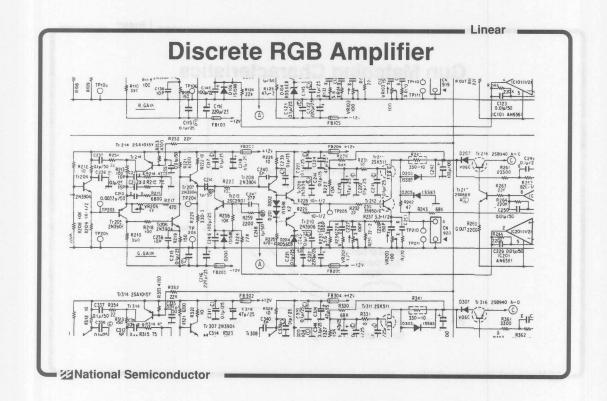

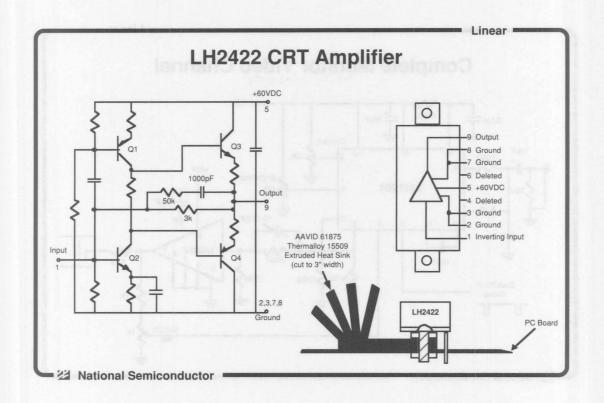

| LH2422 CRT Amplifier                                 | 8-15 |

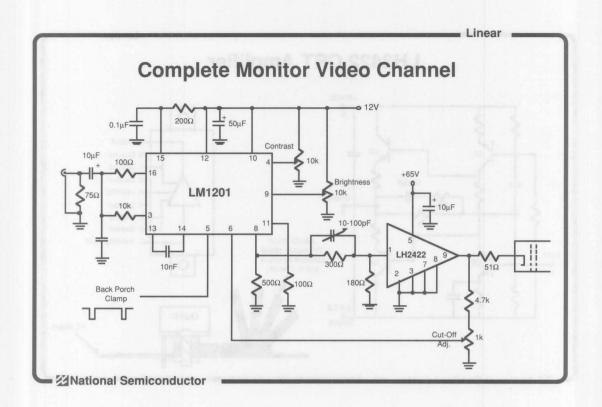

| Complete Monitor Video Channel                       | 8-16 |

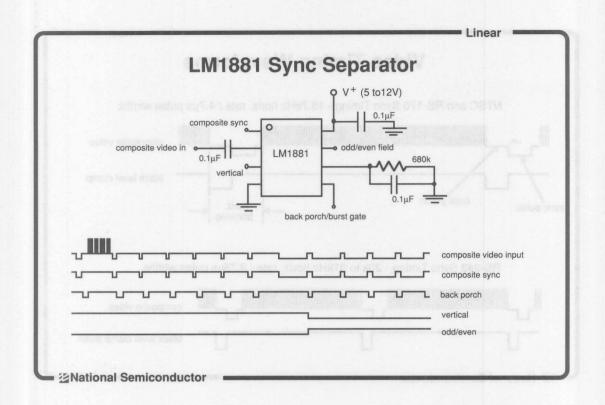

| LM1881 Sync Separator                                | 8-18 |

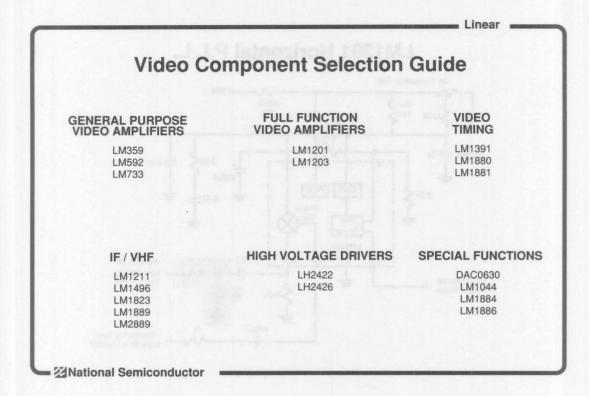

| Video Component Selection Guide                      | 8-19 |

|                                                      | 5 10 |

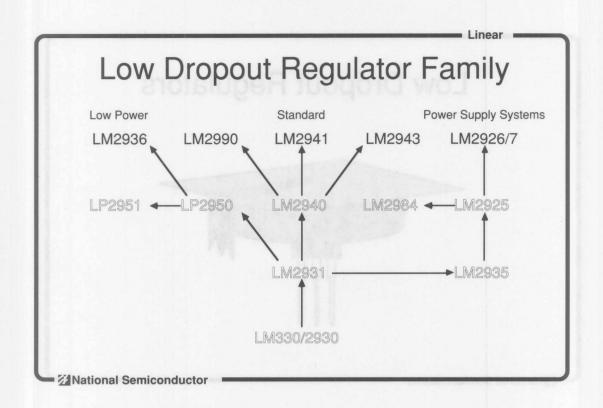

| Section 9: VOLTAGE REGULATORS                        | 9-1  |

| Low Dropout Regulator Family                         |      |

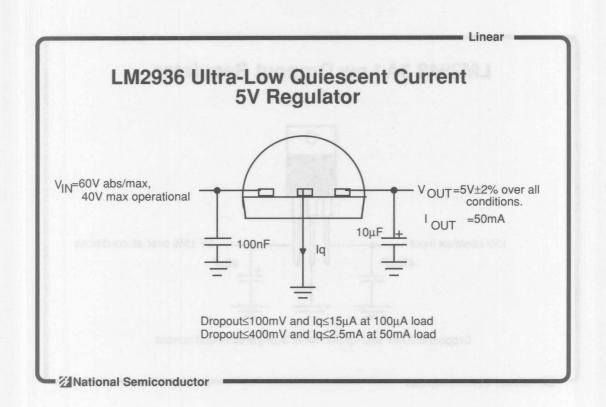

| LM2936 5V, 50mA Regulator                            |      |

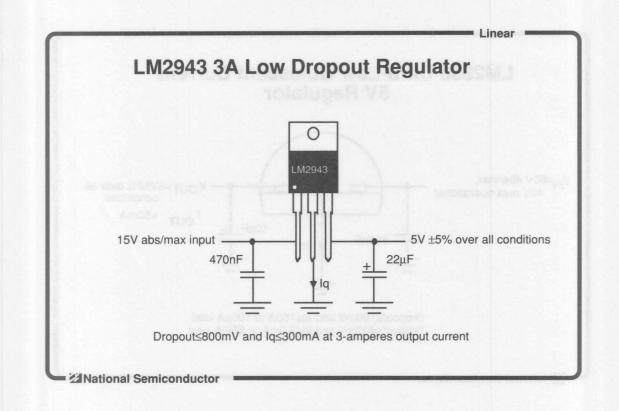

| LM2943 5V, 1A Regulator                              |      |

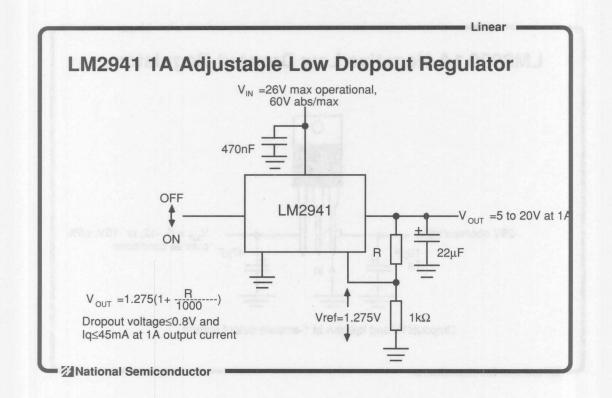

| LM2941 Adjustable 1A Regulator                       |      |

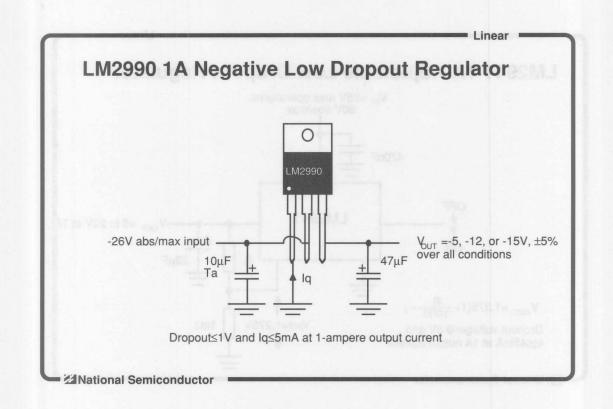

| LM2990 -5V, 1A Regulator.                            |      |

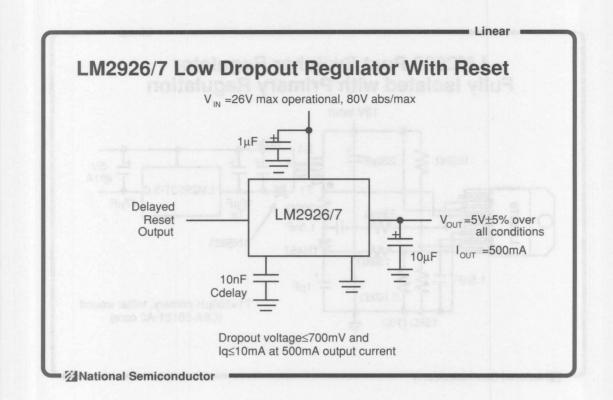

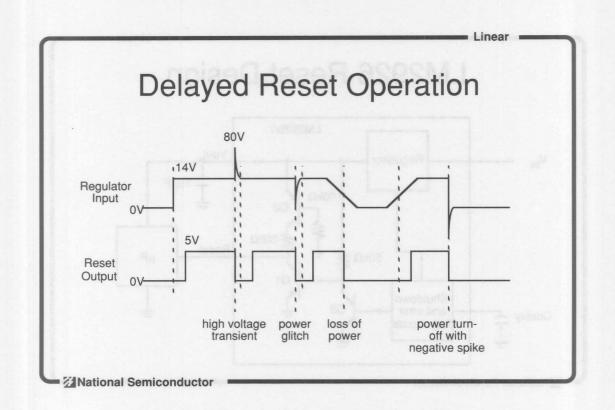

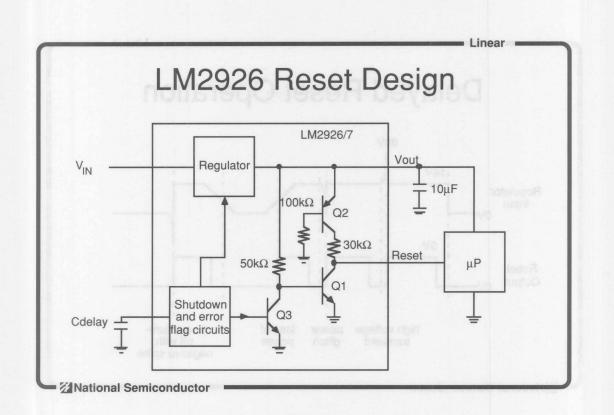

| LM2926/7 5V, 500mA Regulator with Reset              |      |

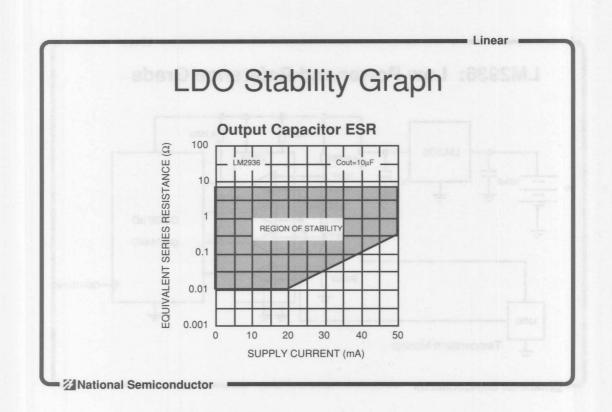

| Stability Graph                                      |      |

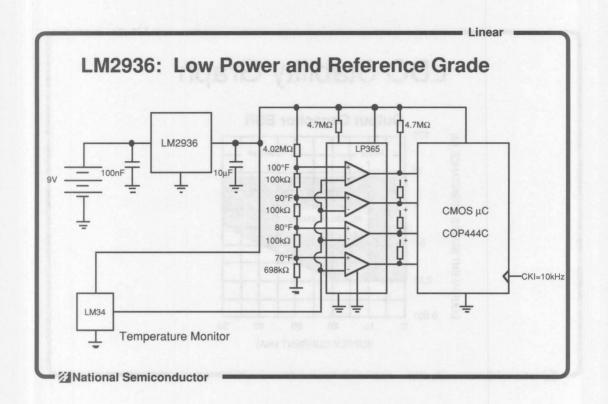

| Reference Grade Regulators                           | 9-12 |

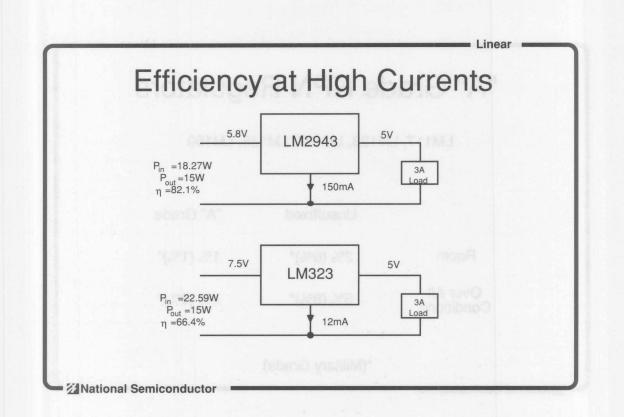

| NPN/PNP Efficiency Comparison                        | 9-14 |

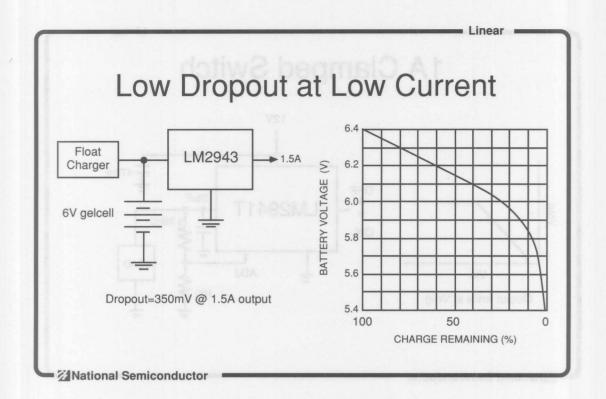

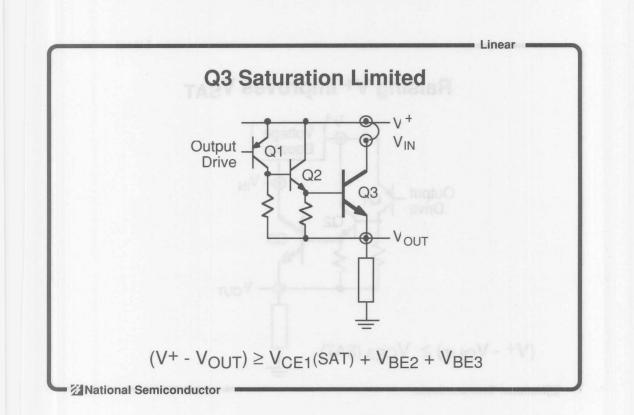

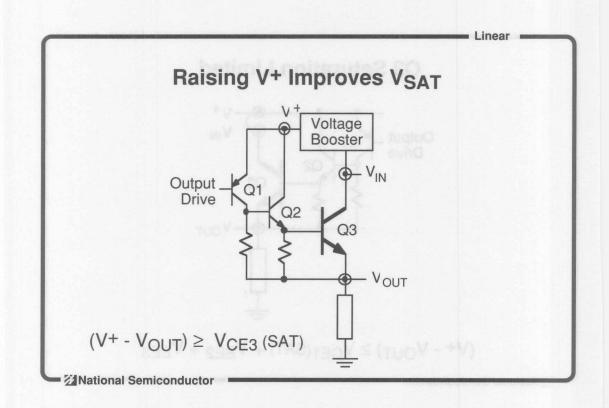

| Achieving Extra-low Dropout                          | 9-15 |

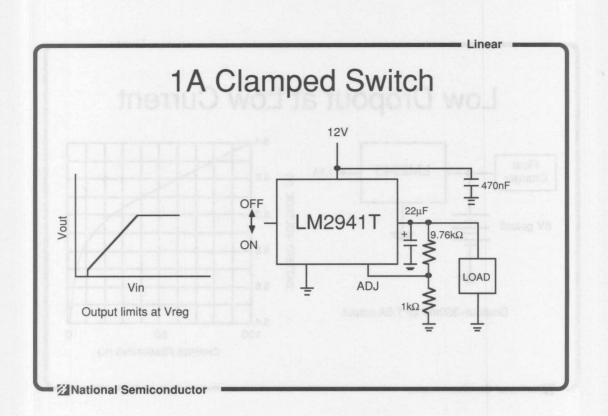

| Clamped Switch                                       | 9-16 |

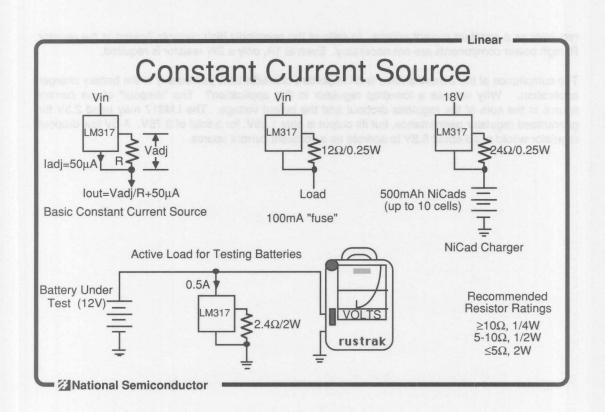

| Constant Current Source                              |      |

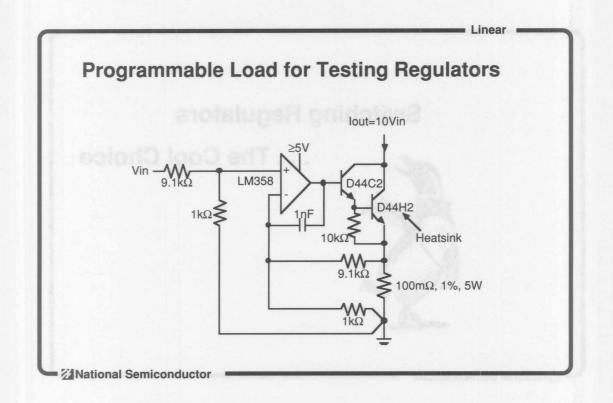

| Programmable Load                                    | 9-19 |

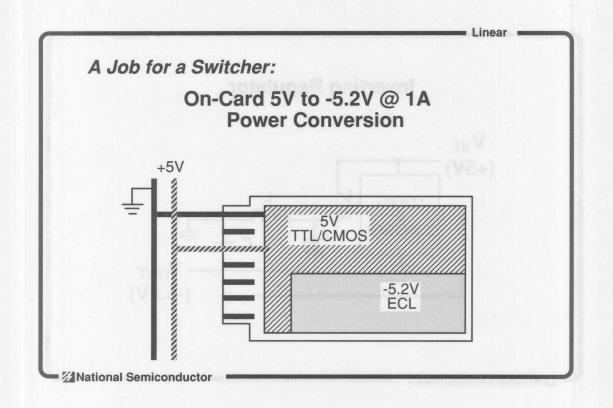

| SWITCHING REGULATORS                                 |      |

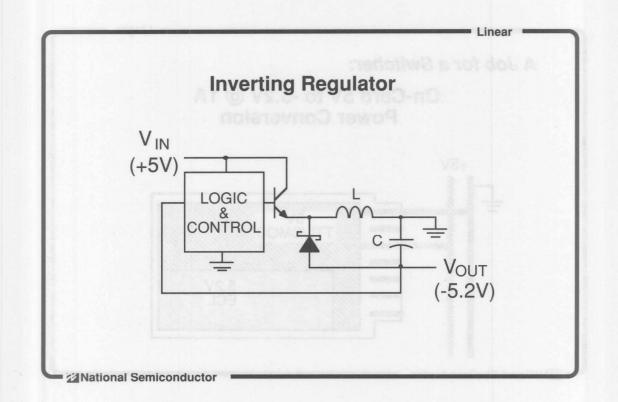

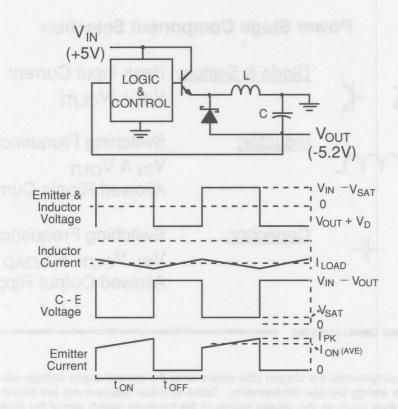

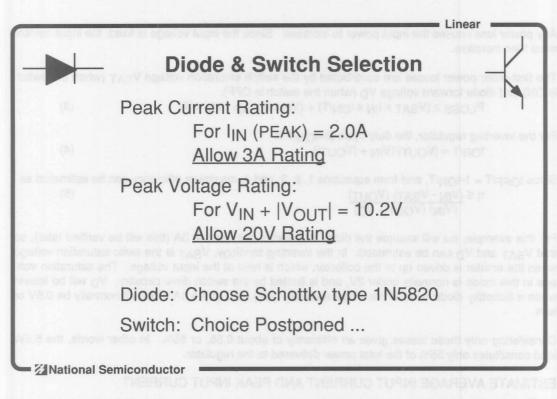

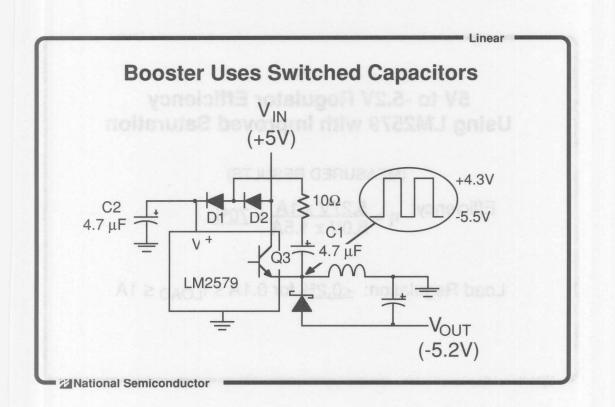

| 5V to -5.2V @ 1A Inverting Regulator                 | 9-21 |

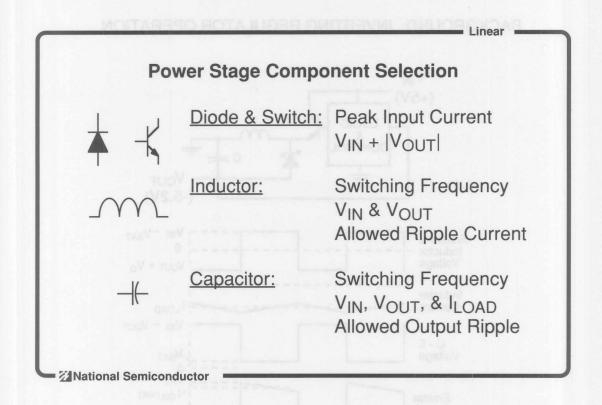

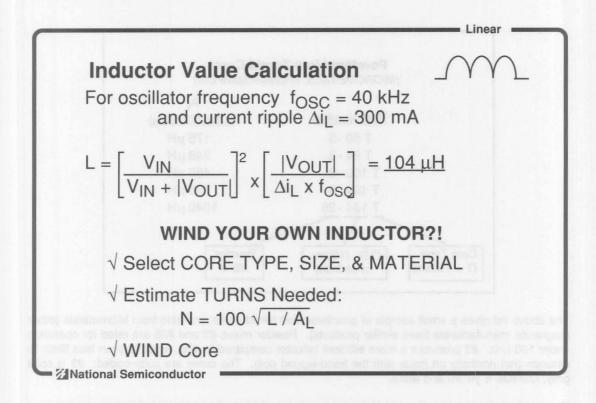

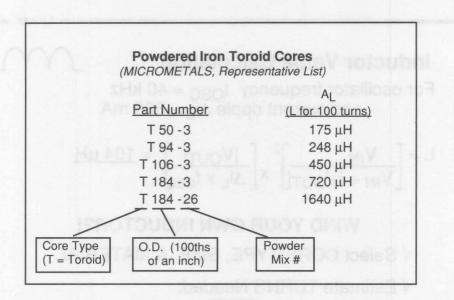

| Inverter Power Stage Selection (Diode, Switch, L, C) | 9-23 |

| Inverting Regulator Operation                        |      |

| Controller Selection                                 | 9-30 |

|                                                      |      |

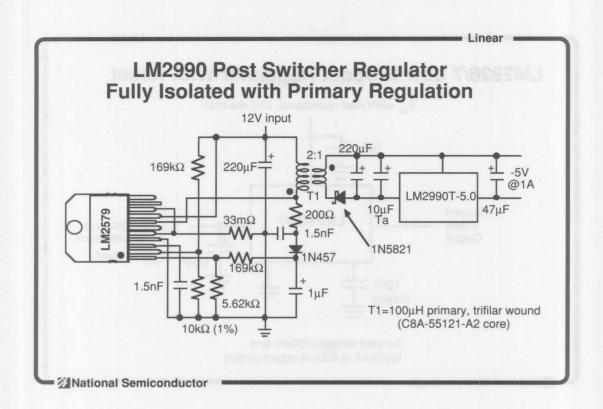

| LM2579 Inverting Regulator                           | 2-32 |

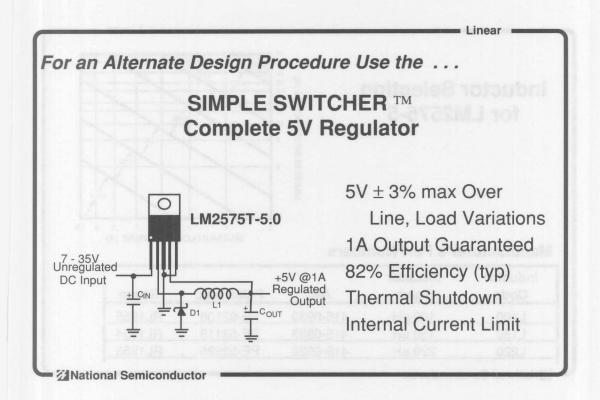

| SIMPLE SWITCHER REGULATORS                           | 2-34 |

| LM2575-5 Buck Regulator                              |      |

| More Simple Switchers                                |      |

| Buck Regulator Design Program                        | 2-42 |

|                                                      |      |

| Section 10: POWER + CONTROL <sup>TM</sup>            | 0-1  |

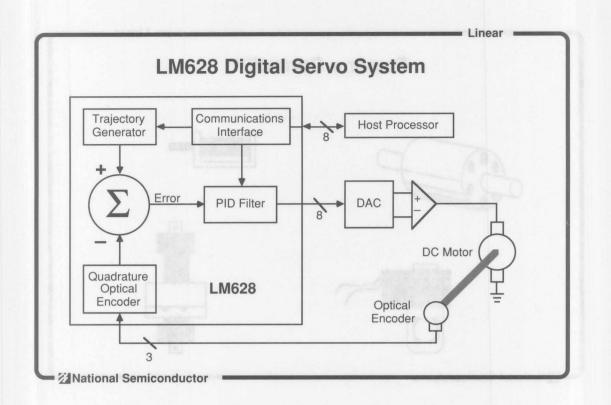

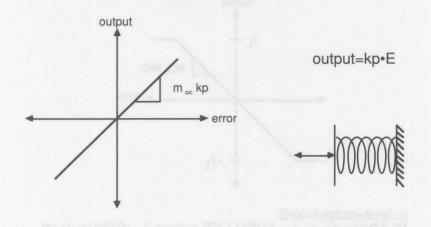

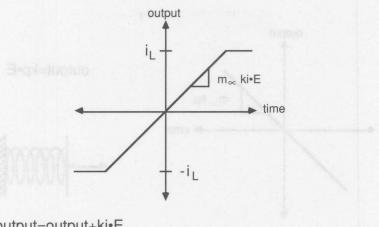

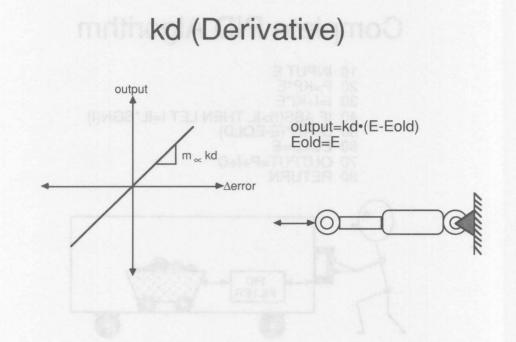

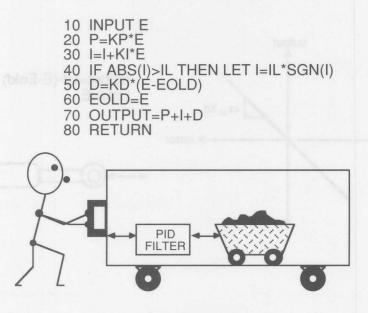

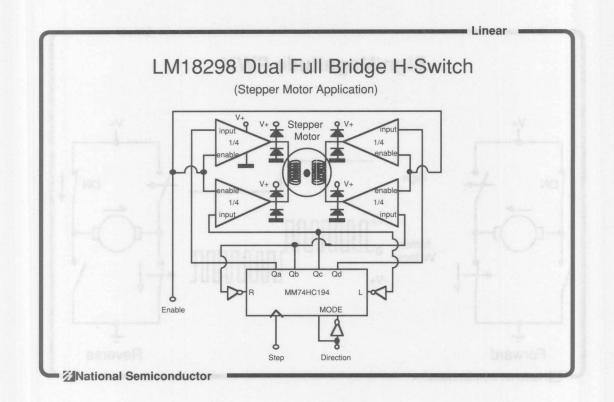

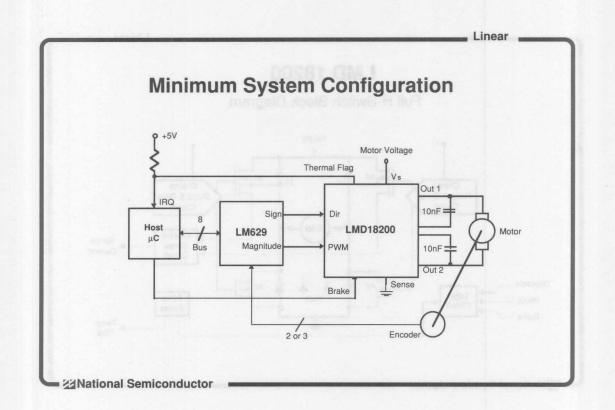

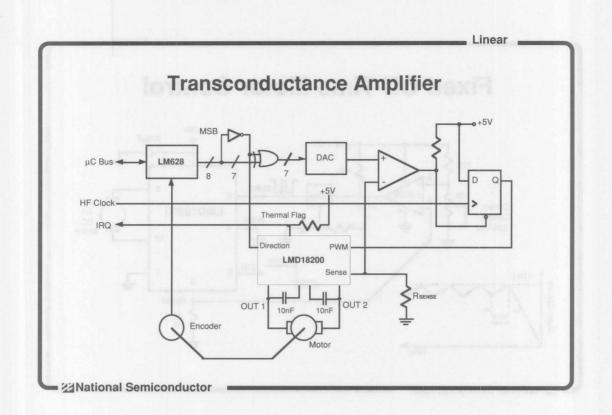

| LM628 PID Filter                                     |      |

| Power Drivers                                        |      |

|                                                      | 01   |

| Section 10: POWER + CONTROL <sup>TM</sup> (continued) | 10-1  |

|-------------------------------------------------------|-------|

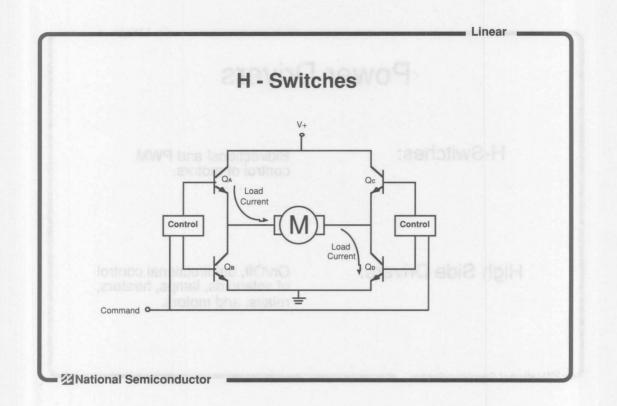

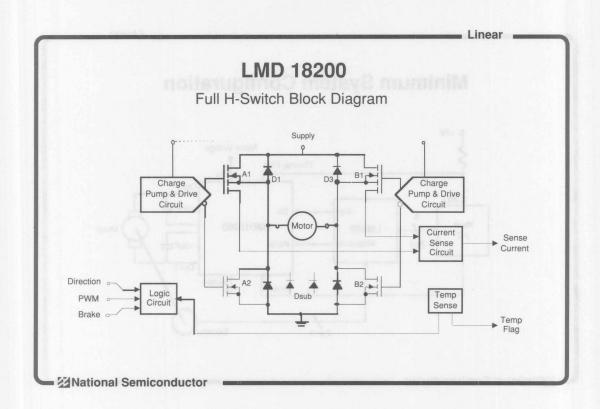

| H-Switches                                            |       |

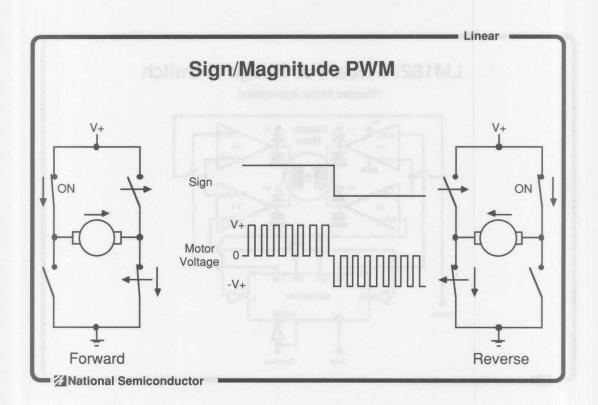

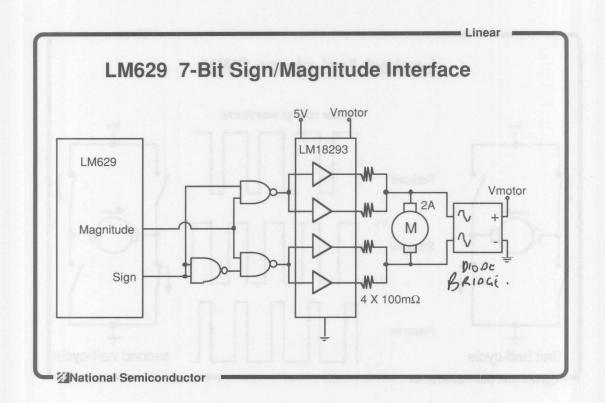

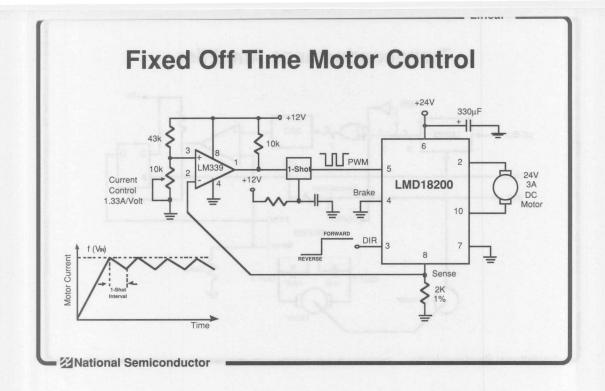

| Sign/Magnitude PWM                                    | 10-10 |

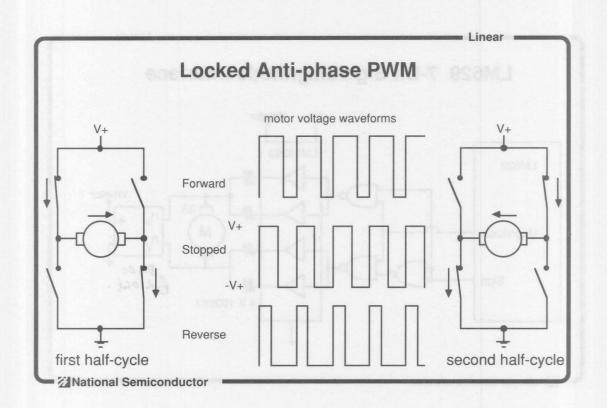

| Locked Anti-phase PWM                                 | 10-12 |

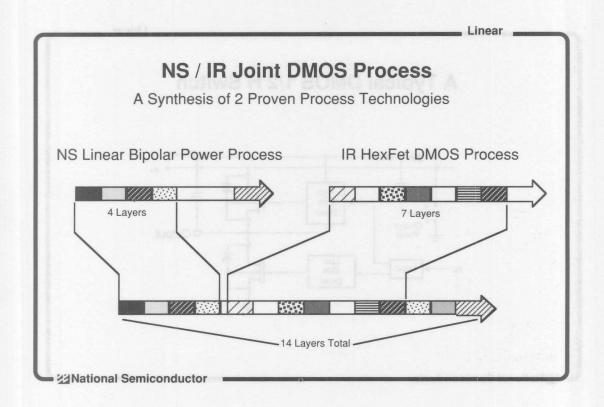

| DMOS Process                                          | 10-13 |

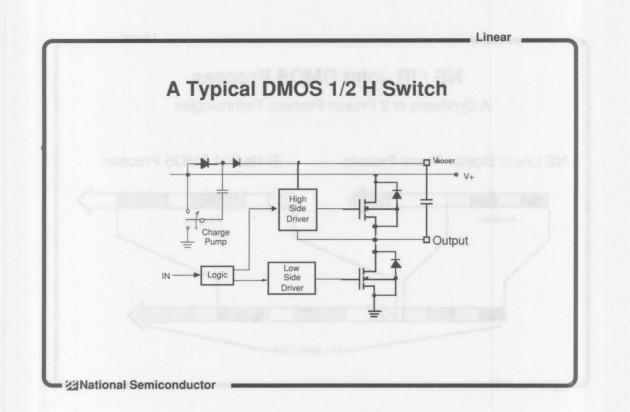

| LMD18200 DMOS H-Switch                                | 10-14 |

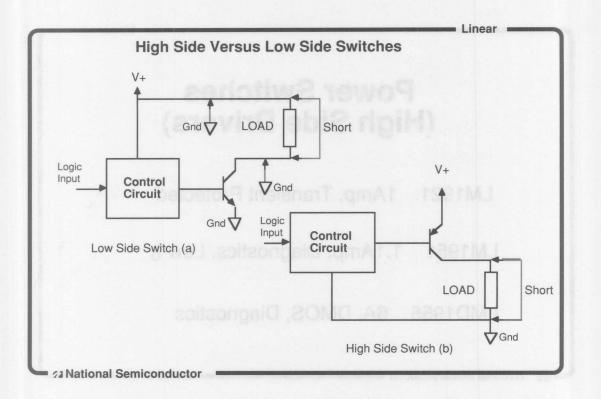

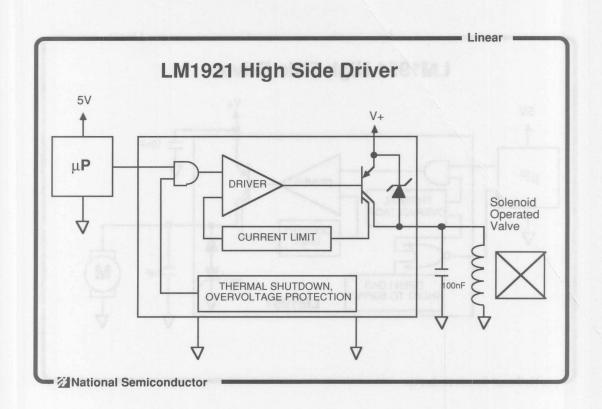

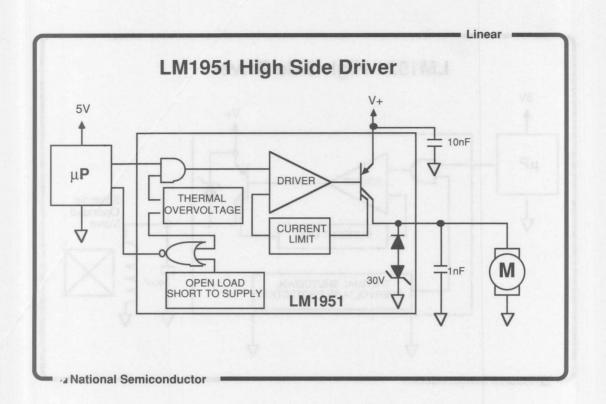

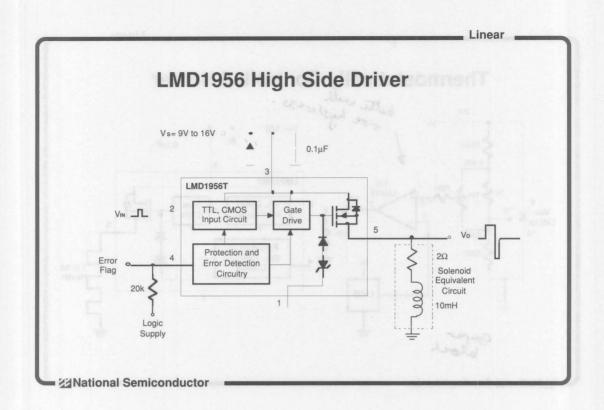

| High Side Drivers<br>LM1921 1A HSD                    | 10-19 |

| LM1921 1A HSD                                         |       |

| LM1951 1A HSD with Diagnostics                        |       |

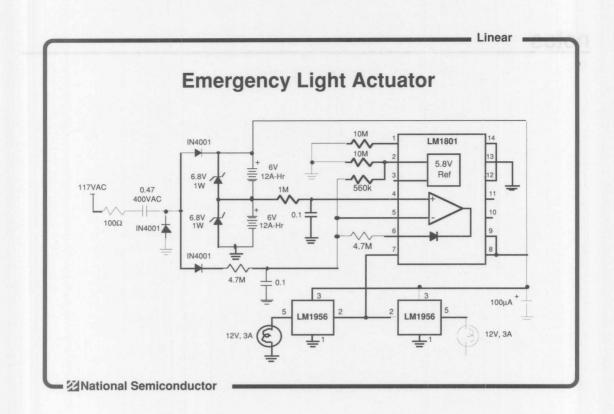

| LMD1956 6A HSD with Diagnostics                       | 10-23 |

Operational Amplifiers.

This section will cover a range of circuits where the selection of the best op amp for different applications is made.

The reasoning used in making the selection is shown so that a similar approach can be used with other applications.

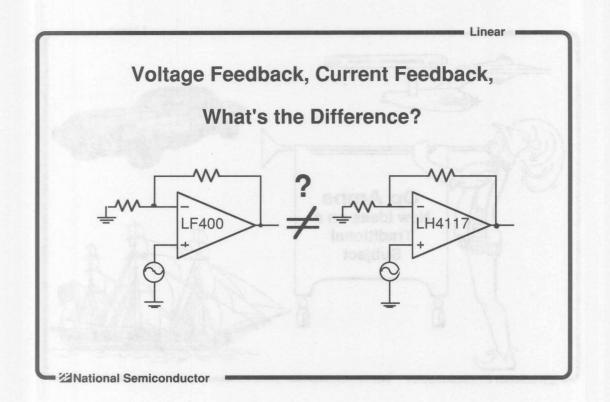

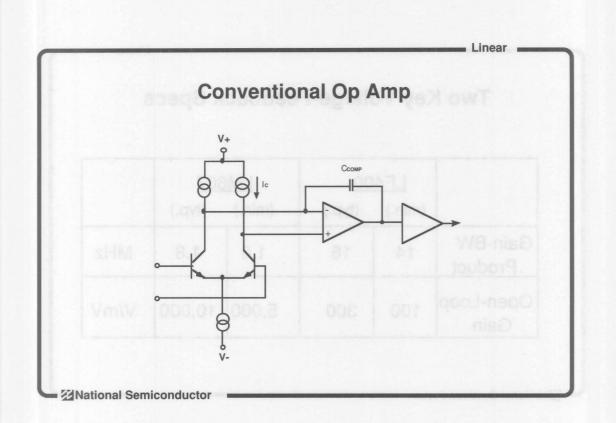

In some applications, current feedback amplifiers offer advantages over conventional or voltage feedback op amps. To better understand where one should select current feedback or conventional op amps, the major differences will be compared.

| 11101              | toy ve | nuger  | eedbac | n opeo. | ,    |

|--------------------|--------|--------|--------|---------|------|

|                    | LF4    | 00     | LM     | 607     |      |

|                    | (min.) | (typ.) | (min.) | (typ.)  |      |

| Gain-BW<br>Product | 14     | 16     | 1.0    | 1.8     | MHz  |

| Open-Loop<br>Gain  | 100    | 300    | 5,000  | 10,000  | V/m\ |

A specification that is regularly listed as one of the features on a conventional op amp data sheet is the gain-bandwidth (GBW). This number is one of the key specifications required when designing a circuit that will operate at other than DC. GBW is the number obtained when the open loop gain of a conventional op amp is measured at a relatively low frequency. The measured gain, in volts per volt, is multiplied by the frequency of measurement. The resulting number is used to determine if an amplifier is able to meet the needs of the application.

The simplified diagram above shows the major features of a conventional op amp design. The input stage is a differential, common emitter stage with high voltage gain. The signal is converted from from differential to single ended and drives the output stage. The output stage is usually unity gain. To maintain stability when the output is connected directly to the input (unity gain stability) a capacitor is connected to the input stage to control the phase shift and bandwidth of the whole amplifier.

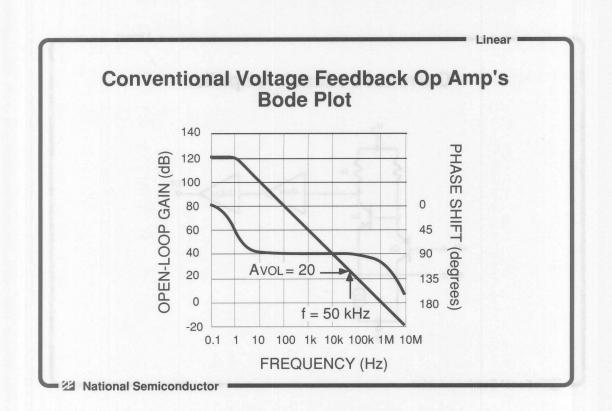

The result is that the whole amplifier has the familiar gain vs frequency response curve as shown above. Here, the gain is totally set by the input stage response. The gain times the operating frequency always equals 1 million or a GBW of 1 MHz. This single pole response is typical of op amps designed for unity gain use. The limitation is that this op amp will only provide a bandwidth of less than 50 kHz when used at a gain of 20.

The advantages of this design are:

A symmetrical input stage with excellent common mode rejection, low offset voltage and current.

Very low offset drifts over temperature.

Very high open loop gains that provide high accuracy at high gains.

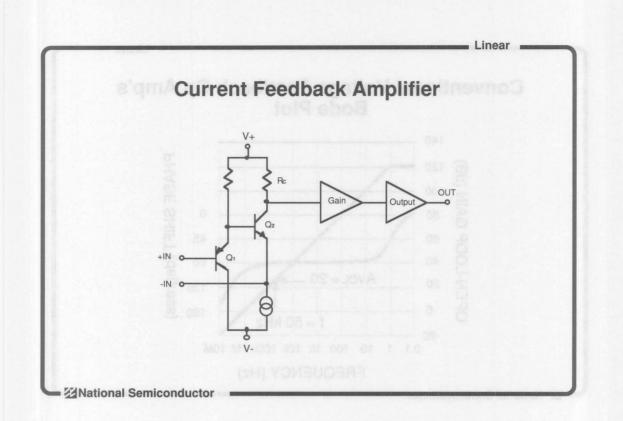

The current feedback amplifier has a greatly different topology. The noninverting input is connected as an emitter follower, or as a source follower in the case of the LH4117.

As such it has no voltage gain. This eliminates the Miller effect. An input to the noninverting input, Q1, is directly coupled to to the inverting input through Q2. This direct feedback in the input circuit greatly reduces the phase shifts that are present in the much longer feedback loop in a conventional op amp.

The change in current in Q2 also drives the gain and output stage. As the inverting input is at the same voltage as the noninverting input, current will flow in or out of the inverting input until the output voltage, divided by the feedback network, is equal to the input voltage. This current flow drives the output until a balance is achieved.

Because the inputs of a current feedback amplifier are not symmetrical, the input drifts with temperature are not likely to be matched. This means that matching the resistances seen by the inputs may not help to cancel them out. This also means that common mode rejection is much lower than in a well designed conventional op amp.

| cha            | Voltage<br>Feedback | <b>VS</b> .   | rent<br>Iback |      |    |

|----------------|---------------------|---------------|---------------|------|----|

|                | <u>LF400/401</u>    | <u>LH4117</u> | <u>LH4118</u> |      |    |

| Slew Rate      | 70                  | 2500          | 2500          | V/µs |    |

| Settling Time  | 200 (0.1%)          | 9 (0.2%)      | 15 (0.1%)     | ns   |    |

| to 0.01%       | 365                 | n/a           | n/a           | ns   |    |

| DC Gain        | 1 to 1000           | 1 to 100      | 1 to 5        | V/V  | 34 |

| Bias Current   | 0.09                | 0.2           | 5000          | nA   | )0 |

| Offset Voltage | 0.1                 | 15            | 2             | mV   |    |

| Power Diss.    | 9                   | 1200          | 600           | mW   |    |

The choice between the two topologies will depend upon the specific parameters needed. If high slew rate and fast settling are key parameters, the LH4117 delivers  $2500V/\mu s$  slew rate and settling to 0.2% in 9ns. The LH4117 has a feature not available in any other current feedback amplifier, a FET input. This provides a noninverting input bias current of 2nA max.

Where high precision, 0.01% or better is desired, the conventional voltage feedback LF400 and LF401 will settle in less than 400ns. Slewing at  $70V/\mu s$  and settling to 0.1% in 200ns, the LF400 and LF401 offer high performance at low cost.

### HIGH-SPEED VIPTM AMPLIFIERS

Linear

#### **APPLICATIONS**

**VIDEO GAIN AND BUFFERING**

FAST VOLTAGE TO FREQUENCY CONVERTERS

**HIGH FREQUENCY ACTIVE FILTERS**

**FLASH A/D INPUT BUFFERS**

National Semiconductor

Many applications require amplifiers that are much faster than typical monolithic op amps. Processing advances are resulting in monolithic amplifiers that have very high bandwidths and slew rates, but without excessive costs. At the same time, hybrid designers can take advantage of the best mix of high-performance technologies to produce amplifiers that are faster than even the fastest monolithics.

Automatic Test Equipment (ATE) is used in the testing of everything from full systems to single devices. When testing many things such as digital ICs, the time to test and the cost is dependent on how fast the test can be performed. This may be determined by how long it takes to set up the power supplies and take a measurement.

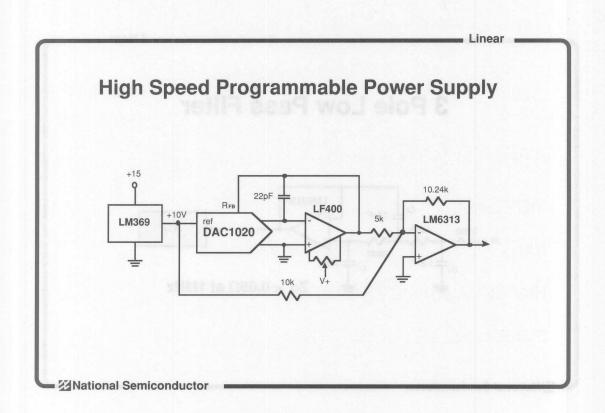

Test cost is also effected by the price of the test equipment. The high speed, high power op amp, LM6313 provides an opportunity to save on both areas.

The circuit shown above is a complete, low cost, high speed, programmable power supply. This supply will provide +/-10V at 200mA and slew at over  $250V/\mu s$ . This combination means that a value can be programmed into the DAC and the output will be within 0.1% in less than 1 $\mu s$ . The speed and power output make this useable as a waveform generator that drive  $50\Omega$  loads.

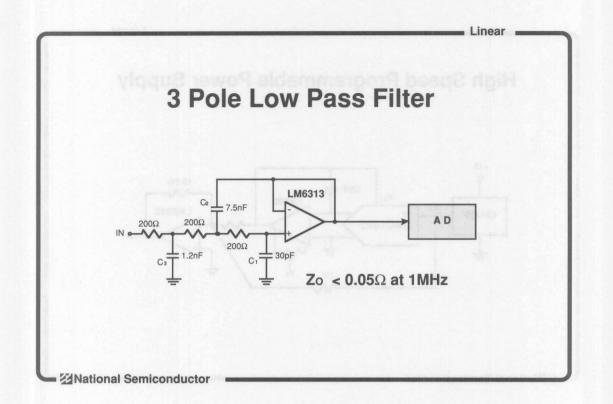

Driving high speed analog to digital converters often requires that the source impedance be very low to prevent the rapid changes in input impedance of the A-D from causing errors. Additional errors can be caused by the input signal changing too rapidly during the measurement.

The LM6313 in this low pass circuit filters the signal and provides an output impedance of less than  $1\Omega$  from DC to above 10MHz

ha diridud enowin above is a complete, faw cost, high speed, jang anniholos power supply. This sup www. provide et 10V at 200mA and site site a over 2509 na. The occesination means that a value op to programmed into the DAC and the output will be within 0.1% in test dram tus. The speed on ower output marke this veedble as a waveform generator that drive 500 loads.

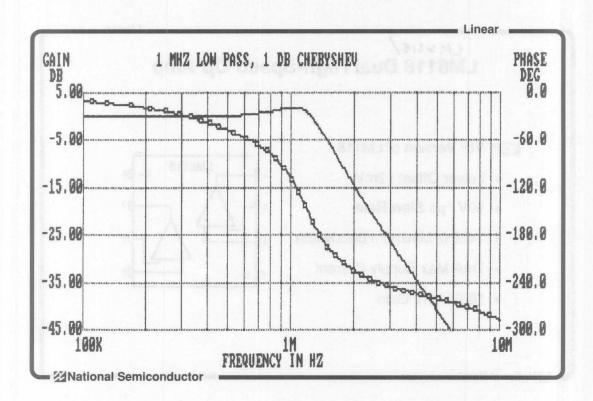

This plot of the filter response shows how with one low cost op amp and 3 standard resistors and capacitors, two important functions can be accomplished. First, the impedance driving the A to D has been reduced to less than  $0.05\Omega$  at 1MHz. This is possible because the LM6313 has a bandwidth of 35MHz and a very low open-loop output impedance. Second, undesirable signal components above 1MHz have been reduced at the rate of over 60dB per decade of frequency.

If the about 1dB peaking at 1MHz is undesirable, a change in the capacitor values to make the filter a butterworth will eliminate this peaking with a slight reduction in the attenuation rate.

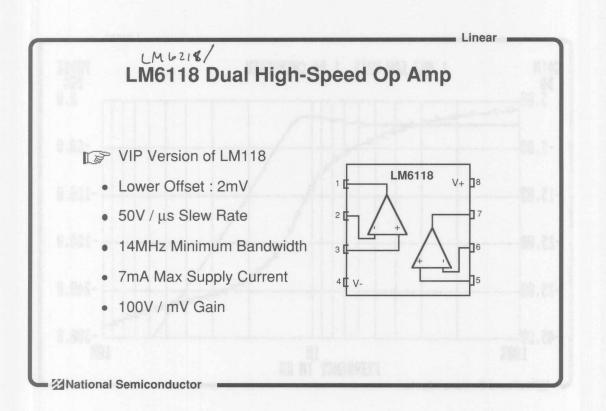

The LM118, introduced in 1971, achieved high speed with feedforward around the PNP transistors. External compensation allowed the user to optimize the device for high slew rate or for better stability. The fast PNP transistors that are available on the VIP process now make possible the LM6118, a dual operational amplifier with performance superior to that of the single LM118. The LM6118's non-inverting slew rate is guaranteed to be over 50 V/µs (as is that of the LM118); additionally, the LM6118's inverting slew rate is guaranteed to be over 100 V/µs. The LM6118's GBW is typically 17 MHz (compared with the LM118's typical 15 MHz GBW), and has a guaranteed minimum of 14 MHz. The maximum offset voltage is half that of the LM118, and the maximum supply current for the dual op amp is less than that of the single LM118. In addition, the LM6118 needs no external compensation.

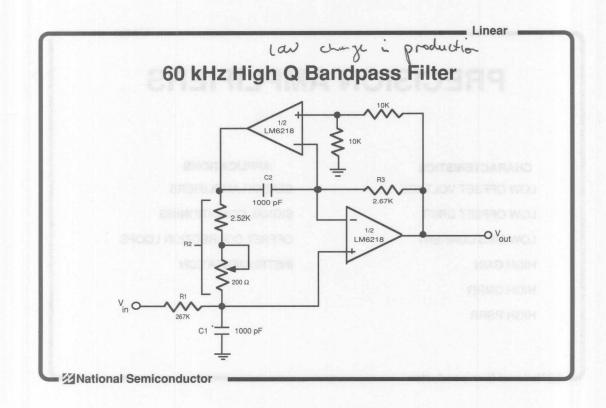

In order to tune in WWVB, the National of Bureau of Standard's radio station which transmits at 60 kHz, a high Q bandpass filter such as the Q of 100 filter shown here could be used. The major problem encountered when building a high Q, high frequency filter is locating an op amp of sufficient bandwidth. The LM6218 was chosen for that reason.

This filter topology is useful because its Q and center frequency ( $f_0$ ) are relatively insensitive to variations in component values. Sensitivity studies show that if the bandwidths of both amplifiers are nearly equivalent, extremely small deviations of Q from the design values will occur, and thus it is advantageous to use a dual op amp. Also, the component values are easy to compute, as demonstrated by the following formulas.

> C1 = C2 = C (arbitrarily chosen) R2 = R3 = R =  $1 / 2\pi f_0 C$ R1 = QR

The filter's center frequency will be slightly below that determined by the circuit resistor and capacitor values because of the finite value of the LM6218's bandwidth. For this reason, a small value potentiometer has been included in the circuit, and may be used to tune the filter's center frequency.

Precision applications that involve very small signal voltages or that require very high accuracy demand very low offset voltages as well as very low offset drift with temperature. The low drift requirement calls for NPN input devices, since these devices drift less than PNPs or FETs. Low input bias current is also very important in precision applications, because input bias current induces offset voltage in source and feedback resistors. Low input bias current can be attained by reducing the collector current in the input transistors, but this approach will also reduce the amplifier's speed. Another way to reduce input bias current is to use input devices with very high beta. This allows higher collector currents, and consequently higher speed, but with low bias current. This approach is used in the LM607 precision operational amplifier. The input transistors in the LM607 are "super beta" transistors, giving the LM607 greatly improved performance over the industry standard precision op amp.

In addition to good input specifications, precision op amps should have very high open loop gain to ensure closed loop gain accuracy. CMRR should be excellent to assure good linearity, and PSRR should be high to avoid errors caused by power supply perturbations.

he titler's center frequency, will be slightly below that determined by the drout resistor and capto or values because of the finite value of the LM0216's bondwidth. For this reacting a small value p

| LM607 PRECIS           | Bitten than     |

|------------------------|-----------------|

|                        | ma ser          |

| LOW OFFSET VOLTAGE     | 25µV max        |

| LOW OFFSET DRIFT       | 0.3µV/°C max    |

| LOW INPUT BIAS CURRENT | 2nA max         |

| MODERATE SPEED         | 1.8MHz, 0.7V/μs |

| LOW SUPPLY CURRENT     | 2mA max         |

The LM607 precision op amp uses super-beta input transistors to achieve higher performance than the industry standard precision operational amplifiers. The highest-grade version of the LM607 has less than  $25\mu$ V offset with less than  $0.3\mu$ V/°C drift. Input bias current is less than 2nA, but the super-beta input devices allow sufficient input stage collector current for 1.8MHz bandwidth and 0.7V/µs slew rate - far better than most other precision amplifiers of this type. The LM607's higher bandwidth gives it better gain accuracy for ac signals (even low-frequency ones) than other precision op amps. Although the bandwidth is relatively high, the LM607's supply current is only 2mA.

Open-loop voltage is greater than 2,000,000, ensuring excellent closed-loop gain accuracy. CMRR is extremely good: >124dB.

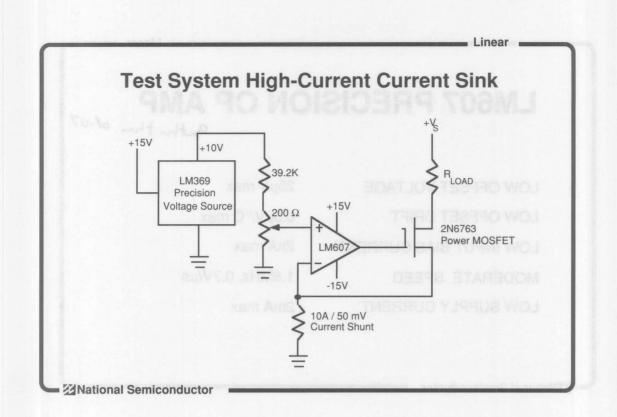

A 10A constant-current sink such as the one shown here uses an op amp to control the voltage across a 5 m $\Omega$  current shunt so that this voltage matches that at the op amp's non-inverting input. With the shunt voltage set to 50 mV, a constant current of 10A is drawn through the load. The advantage of using an LM607 in this application is that shunt voltages significantly lower than 50 mV can be accurately monitored over temperature by the LM607. These lower voltages occur when the 200 $\Omega$  pot is set within its lower range so as to cause the circuit to sink lower values of current.

The precision of this current sink thus lies in the inverting and non-inverting terminals not drifting apart over temperature. Over temperature, the input bias and offset currents of the LM607AC are 4 nA MAX and the voltage gain is 2 Million MIN. These specifications are quite good, and their effects over temperature are minimal in comparison to the LM607's  $0.3 \,\mu\text{V}$  / °C MAX Input Offset Voltage drift (which is also quite good). The worst-case drift of V<sub>OS</sub> from room temperature (where presumably the circuit's pot is adjusted) to 70 °C is 14  $\mu$ V. This 14  $\mu$ V drift over temperature translates to a total current error over temperature of 2.8 mA. Thus, by adjusting the circuit's pot, one can sink a wide range of currents with good accuracy, including those significantly lower than 10A.

# LM627 & LM637 FAST, PRECISION OP AMPS

Linear

|                        | LM627        | LM637         |

|------------------------|--------------|---------------|

| LOW OFFSET VOLTAGE     | 25μV         | 25μV          |

| LOW OFFSET DRIFT       | 0.3µV/°C     | 0.3µV/°C      |

| LOW INPUT BIAS CURRENT | 10nA         | 10nA          |

| HIGH SPEED             | 10MHz, 3V/μs | 45MHz, 10V/μs |

|                        |              |               |

|                        |              |               |

| National Semiconductor |              |               |

The LM627 and LM637 combine most of the high-precision characteristics of the LM607 with a significant increase in speed. The LM627 is unity-gain stable and has a 10MHz gain-bandwidth product, while the LM637 has a gain-bandwidth product of 40MHz and is stable for gains greater than or equal to 5. The substantial increase in speed enables these amplifiers to provide excellent gain accuracy at higher frequency-gain products than would be possible with the LM607. The dc gain is as high as that of the LM607, so dc gain accuracy will be similarly excellent.

In addition to higher speed, the LM627 and LM637 are very low noise amplifiers (3.8nV/ $\sqrt{Hz}$ ). This further enhances their ability to perform well in high-precision applications.

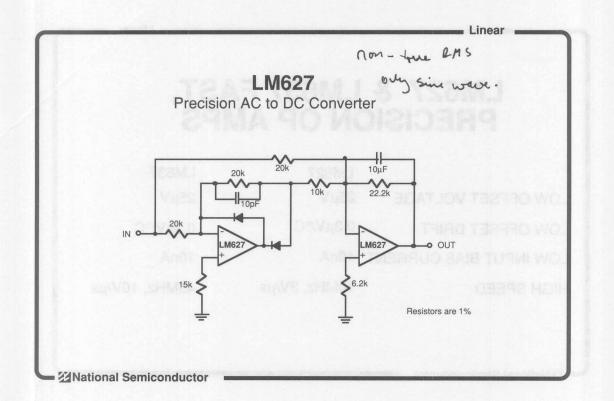

This precision ac-dc converter takes advantage of the LM627's improved ac performance as well as its high degree of dc precision. The design is conventional, with the first amplifier serving as a half-wave rectifier. By summing the half-wave rectified signal with half of the input waveform, a full-wave rectified signal current appears at the summing node of the second amplifier. This signal is averaged by the  $10\mu$ F feedback capacitor to provide a dc output signal. With a sine wave input, the output voltage will be the rms value of the input signal.

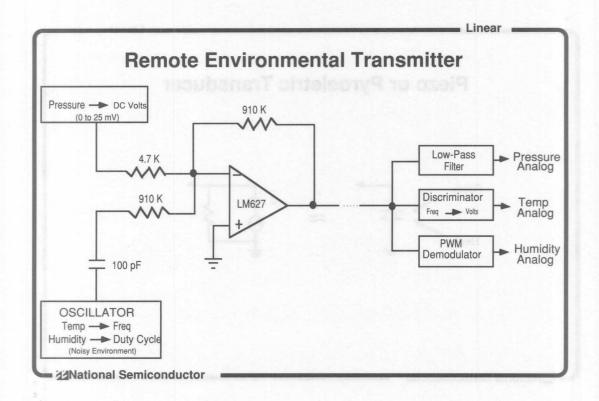

This circuit shows a means for encoding and transmitting pressure, temperature, and humidity information from a remote location. Since the pressure sensor is located in a benign environment, the measured pressure can be encoded as a DC signal. The humidity and temperature sensors, however, are located in a noisy environment and thus require an alternative encoding scheme. In this case, modulation of the frequency and duty cycle of an oscillator accomplishes just that.

The requirements of this circuit are that the DC voltage representing the pressure be amplified to near 5 VDC ( for a full-scale reading) while being within 1/2 LSB of an eight-bit system (which equates to 9.8 mV), and must pass up to 5 MHz from the oscillator. An op-amp with particularly good DC specifications over temperature as well as fairly wide bandwidth is needed. The LM627, having a maximum of 50  $\mu$ V of offset voltage over temperature, an input bias current that is insignificant in this case, and a 14 MHz gain-bandwidth product, meets the necessary requirements. The worst-case offset at the output of the LM627 (over temperature) will be 9.73 mV, which is just within the 1/2 LSB requirement.

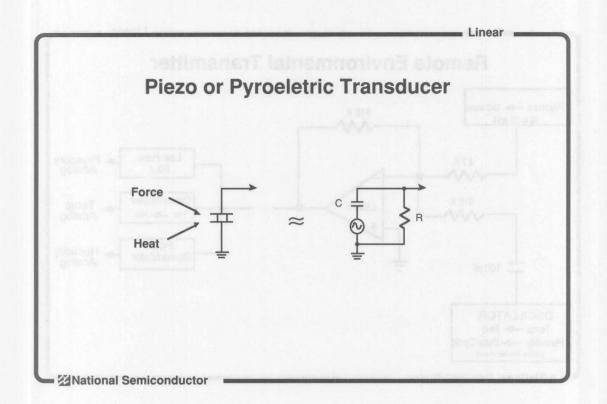

Whenever a piezoelectric transducer such as a microphone, accelerometer, dynamic pressure gage or a pyroelectric detector is such as a flame or intrusion monitor is used, an amplifier must be designed to condition these signals. These transducers appear as a voltage source in series with a capacitor. The capacitor value will typically range between 10 and 50pF for pyroelectric detectors and 100pF to 100nF for the piezoelectric transducers. There is a shunt resistor, but it is usually very high in value and not important to the design. Typical values for the leakage resistance is between  $10^{10}\Omega$  and  $10^{14}\Omega$ .

The signal voltages will range from microvolts to hundreds of millivolts. The low level of the signals and the very high impedance of the capacitance will require an amplifier that can respond to the low voltages at very low currents.

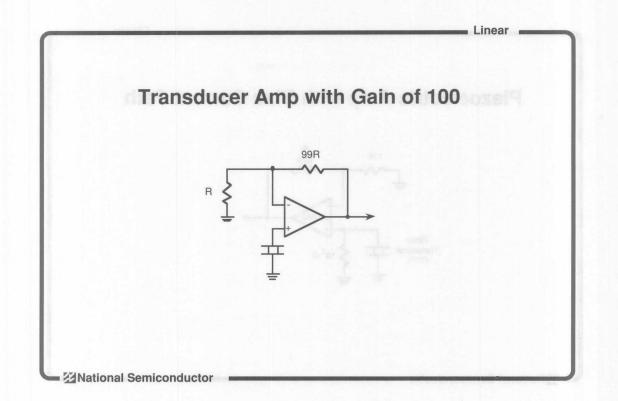

A simple approach is to connect the transducer to the noninverting input of an opamp. Adding gain setting resistors will raise the output voltage to reasonable levels. The basic problem with this circuit is that because the transducer is an open circuit to the bias current, this current will continually charge the transducer. This will rapidly drive the output to its limit.

If the transducer has a lower shunt resistance such as the typical  $10^9\Omega$  found in most pH probes, this circuit might work if the bias current of the op amp is low enough.

The officed vortage is amplified by the CIG gain of 100 and can odd a maximum of an additioned 90 nV to the output. The uPCDC2 only dead about 40µA per amplifier and will provide a bendwich the shout 30kHz in the diracit. If wilder tomewidth is needed, the tuMC602 will provide over 100kHz but width and still provide the same outplanding law bias surrent.

his circuit is limited at the fow intervency end to about Titz, by the time constant of the transdoot epocitionou and the 1000 MCI resistor , 1000 Missiohn resistorn are expensive and moult board leak cas are likitly to be chector then the. The next circuit greatily reduces there problems.

Adding a resistor to ground provides a path for the bias current. Unfortunately this resistor loads the transducer signal. Assuming that the transducer is fairly large, 1nF, the source impedance at 1Hz is 159 Megohms. To get response down to 1Hz requires that the load impedance be larger than that.

If a JFET input op amp such as the LF355 is used, the bias current over temperature can cause as much as 800V of output. The power supply current will be about 2mA. Raising the feed-back resistor to 1000 M $\Omega$  to balance the inputs and cancel the effect of the bias current can still result in 200V out from offset current. It may also cause the amplifier to oscillate because of the added phase shift caused by the op amp input capacitance and Rf.

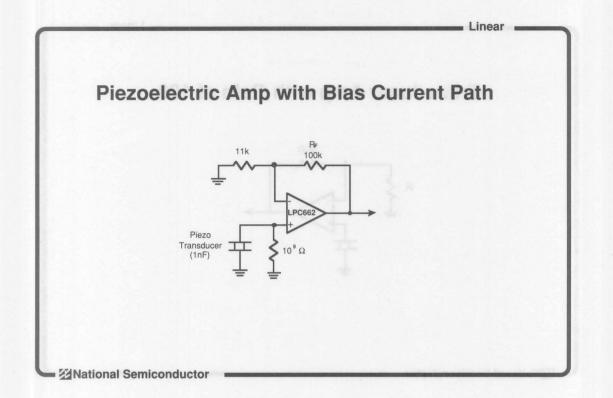

By selecting the LPC662 low power, dual, CMOS op amp, the bias current is reduced to the extent that over temperature the maximum output shift is 200 mV.

The offset voltage is amplified by the DC gain of 100 and can add a maximum of an additional 600 mV to the output. The LPC662 only uses about  $43\mu$ A per amplifier and will provide a bandwidth of about 30kHz in this circuit. If wider bandwidth is needed, the LMC662 will provide over 100kHz bandwidth and still provide the same outstanding low bias current.

This circuit is limited at the low frequency end to about 1Hz by the time constant of the transducer capacitance and the 1000 M $\Omega$  resistor . 1000 Megohm resistors are expensive and circuit board leakages are likely to be greater than this. The next circuit greatly reduces these problems.

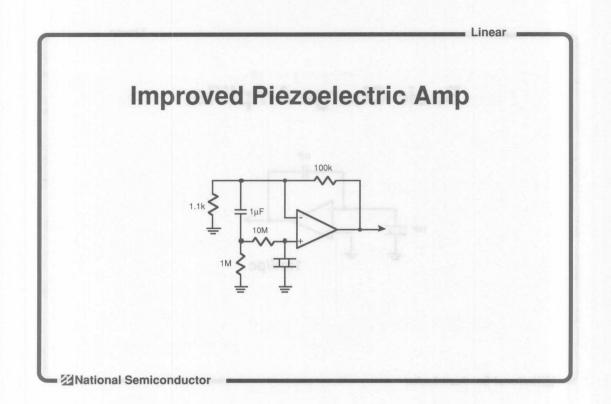

In this circuit, the AC input impedance has been raised by positive feedback to 11 M $\Omega$  times the open loop gain of the op amp divided by the closed loop gain. This will raise the effective input impedance to over 300 megohms. Because the capacitor blocks the DC feedback, the bias current voltage drop is only across 11 M $\Omega$ . This now only causes a maximum output error of 2.2 mV.

This circuit provides a gain of 40dB and a flat frequency response from below 1Hz to about 50kHz with a 1nF transducer. As the low frequency response is inversely related to the transducer capacitance, if a 30 pF pyroelectric detector is used, the low frequency cut-off will be 30 times higher.

One limitation of this circuit is the result of exactly what we set out to achieve. This amplifier responds to the voltage applied to the input. The transducer output appears as a voltage in series with its capacitance. Any capacity between the input and ground will absorb charge in proportion to the ratio of it's capacitance to the transducers capacitance. In this example, a rather high capacitance transducer (1nF) is used. Even so, this means that if 10 feet of RG 174 coax cable is used to connect the transducer to the amplifier, the signal will be reduced by 23%. The next circuit will eliminate this loss of accuracy or calibration.

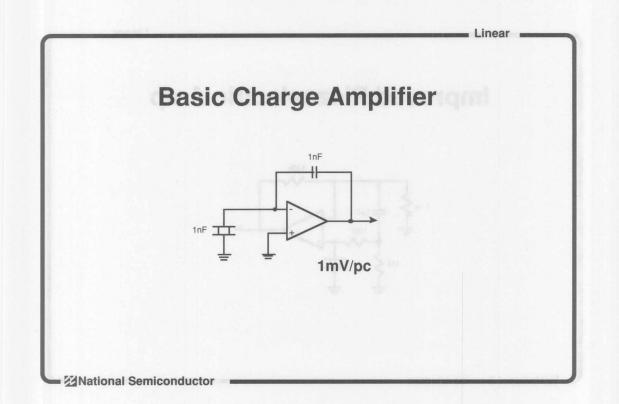

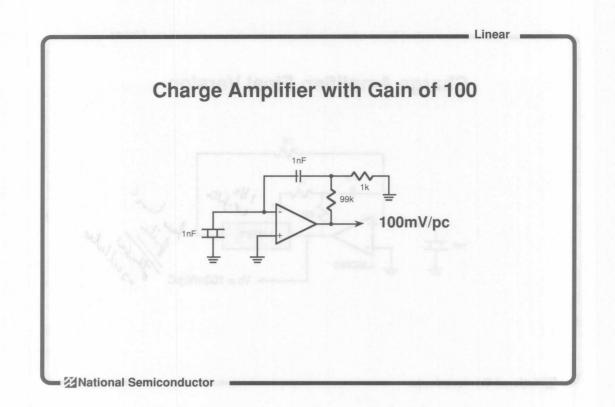

This circuit is just the opposite of the previous circuits in that it is very low input impedance. The charge amplifier is the capacitor equivalent of the standard inverting op amp with resistors in the input and feedback. The output is set the same way. It is the ratio of the transducer output in picocoulombs divided by the feedback capacitance in picofarads.

This works out well as most piezo and pyro transducers are specified to have an output of so many picocoulombs per unit of input.

The problems with this simplified circuit is that there is no path for the bias current and the output is only 1mV/picocoulomb. 1picocoulomb being the charge required to produce 1V across 1pF. The real advantage of this circuit is that the sum node is a virtual ground. This assures that all of the transducer output will go to the sum junction without being divided across any connecting cable capacitance. This allows different lengths of cable to be used without changes in calibration.

By dividing the feedback by 100 we have increased the sensitivity to 100 mV/pc. The price paid, because the gain-bandwidth is constant, is that the bandwidth has been reduced from over 100kHz to just over 1kHz. We have also not dealt with the bias current. As in the earlier example, the amplifier bias current will cause the output to drift to the limit.

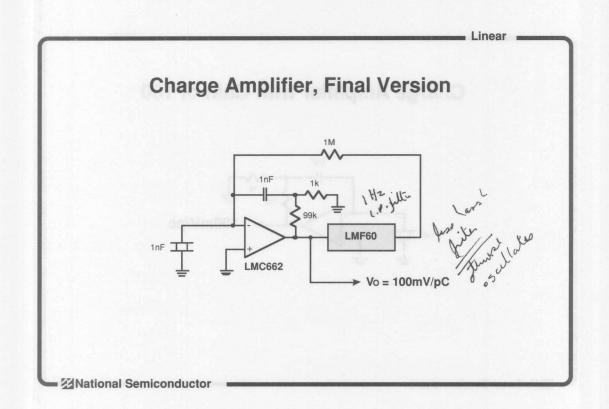

By the simple addition of an active low-pass filter, the DC gain has been reduced to 1 and a path for the bias current established. The AC gain has been set to 100mV/pc and with the LPC662 the frequency response is from below 1Hz to above 1kHz. With the LMC662 the response extends to 700 kHz. The LMF60 switched capacitor filter can easily be set to a wide range of frequencies just by adjusting a single resistor.

For higher gain, or bandwidth, the 2nd op amp in the package can be used without increasing board space or power consumption. This will provide a large signal output from low output devices such as pyroelectric detectors.

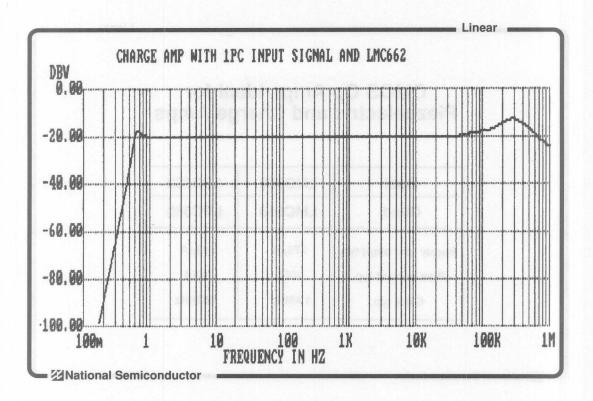

This graph shows the frequency response of the charge amp. The signal was 1pc and the scale is in dBV. Because the input impedance of this amplifier is less than  $1k\Omega$  over the frequency range, the response is almost unchanged if a transducers of different capacities are used.

If the LMC662 is used, the bandwidth will be extended to over 500kHz. This should only be done if this additional bandwidth is needed, because the noise in this circuit as in any other circuit is in proportion to the bandwidth. Limiting the bandwidth will also limit the noise.

| CMOS Op<br>Piezoelectric                    |               |              |

|---------------------------------------------|---------------|--------------|

| Dual                                        | LMC662        | LPC662       |

| Quad                                        | LMC660        | LPC660       |

| Isupply (per amp) typ.<br>Bias current typ. | 375μΑ<br>40fA | 43μA<br>40fA |

| GBW typ.                                    | 1.4MHz        | 350kHz       |

These op amps are ideal for use wherever ultra low bias and offset currents are desired. The ultra low power LPC660 and LPC662 are ideal for battery powered applications. Using a similar design, The LMC660 and LMC662 provide four times more gain-bandwidth for circuits operating at higher frequencies.

The LMC660 and LMC662 both are specified for driving 600 $\Omega$  loads, while the LPC versions are designed to drive 2k $\Omega$  loads. With an output that will swing to either supply and an input common-mode range that can go below the negative supply, these op amps are ideal for single supply operation.

The whole family will operate on a total supply voltage from 4.5 to 15.5V and are available in DIP and SO with standard dual and quad op amp pin-out.

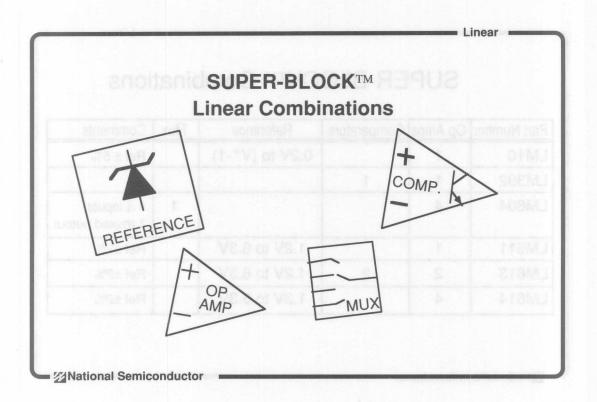

When circuits require several types of linear ICs, National Semiconductor's SUPER-BLOCK<sup>™</sup> devices can be used to reduce the total cost and board space required. With the variety of combinations of functions now available, the designer can choose ICs that give greatest convenience and improved performance over industry-standard devices, in addition to higher packing density at reasonable cost.

The references used in thread companiens have edjustuble output voltages, set with two resistons  $The LM10^4$  references can be programmed for an optical voltage of holwern 200 mW and  $(V^2 + T/T)$  is theread to  $V^2$ , which reserved in a series (voltage augulied) mode. In a struct mode, with the reference output test to set to set the optical voltage.

The shurt references in the LMB11, UMB13, and LMB14 are eitster to the adjustable LM305 ferm ence, and will operate from a couply surfact of 16 µ2 to 10 thA, and can be procrammed to delive 0.24V to 8 3V potput, independent of the audply voltage used by plane parts of the ICL. This LMB16 and LMB14 reference outputs are referred to the 10 a ground (or V<sup>-1</sup>) pint bath the ancos and controls of the LMB14 reference are institution to flave interactor to be used in a flaving mode.

The 1,5604 barrains tota op arrige along with a digitally-programmed inditipater which calects through a for the 4 op amps. Chip stated and analys functions can also be used to gut the output

| Part Number | Op Amps | Comparators | Reference      | Mux | Comments                      |

|-------------|---------|-------------|----------------|-----|-------------------------------|

| LM10        | 1       | -           | 0.2V to (V+-1) | 1   | Ref ± 5%                      |

| LM392       | 1.      | 1           |                | 1   | A. 1-                         |

| LM604       | 4       | T           |                | 1   | 4 ∆ inputs,<br>1 muxed output |

| LM611       | 1       |             | 1.2V to 6.3V   | A   | Ref ±2%                       |

| LM613       | 2       | 2           | 1.2V to 6.3V   | +   | Ref ±2%                       |

| LM614       | 4       | han         | 1.2V to 6.3V   |     | Ref ±2%                       |

Lincor

Each of the SUPER-BLOCK<sup>TM</sup> devices contains one or more op amps (similar to the LM324, except in the case of the LM10) in addition to at least one other function. All the op amps and comparators can operate from a single supply, as their input ranges include ground. The output ranges of the op amps extend within 1V of ground when sinking a few mA, and within 0.2V (typ.) when sinking less than 1  $\mu$ A (except the LM604 mux-amp, which is guaranteed to swing within 0.7V of ground in this light-load condition). Similar to the LM339, the comparator's outputs are open-collector, to be pulled up to a convenient logic-high level.

The references used in these components have adjustable output voltages, set with two resistors. The LM10's reference can be programmed for an output voltage of between 200 mV and (V<sup>+</sup> - 1V), referred to V<sup>-</sup>, when operated in a series (voltage-supplied) mode. In a shunt mode, with the reference output tied to V<sup>+</sup>, the reference output can be used to set the op amp's supply voltage.

The shunt references in the LM611, LM613, and LM614 are similar to the adjustable LM385 reference, and will operate from a supply current of 16  $\mu$ A to 10 mA, and can be programmed to deliver a 1.24V to 6.3V output, independent of the supply voltage used by other parts of the IC. The LM613 and LM614 reference outputs are referred to the IC's ground (or V<sup>-</sup>) pin; both the anode and cathode of the LM611 reference are available to allow the reference to be used in a floating mode.

The LM604 contains four op amps along with a digitally-programmed multiplexer which selects the output of 1 of the 4 op amps. Chip-select and enable functions can also be used to put the output into a high-impedance state.

### SUPER-BLOCK GENERAL DESCRIPTIONS

#### LM10

The LM10 is a monolithic linear IC consisting of a precision reference, an adjustable reference buffer and an independent, high quality op amp. The unit can operate from a total supply voltage as low as 1.1V or as high as 40V, drawing only 270  $\mu$ A (typ.). A complementary output stage swings within 15 mV of the supply terminals or will deliver ±20 mA output current with ±0.4V saturation. Reference output can be as low as 200 mV. This IC is recommended for portable equipment and is completely specified for operation from a single power cell. In contrast, high output-drive capability, both voltage and current, along with thermal overload protection, suggest it in demanding general-putpose applications.

<u>Op Amp:</u> Offset Voltage  $\leq$  4 mV Bias Current  $\leq$  2 nA Supply Current  $\leq$  500  $\mu$ A Gain-Bandwidth Product 100 kHz  $\label{eq:response} \begin{array}{l} \hline Reference: \\ \hline Initial Value 200 mV \pm <5\% \\ \hline Line Regulation \leq 80 ppm/V \\ \hline Suitable for Loads \leq 10 mA \\ \end{array}$

#### LM392

The LM392 consists of 2 independent building block circuits. One is a high gain, internally compensated operational amplifier, and the other is a precision voltage comparator. Both have been specifically designed to operate from a single supply of 2 to 32V. Both circuits have input stages with common-mode range extending down to ground when operating from a single supply voltage. Operation from split supplies is also possible. The device has a standard dual pinout, the same as the LM358 dual op amp and the LM393 dual comparator.

$\frac{Comparator}{Offset Voltage \le 5 mV}$ Bias Current  $\le 250 nA$ Response Time 1.5 µs

#### LM604

The LM604 Mux-Amp is an op amp with four selectable differential inputs, combining the functions of a multiplexer with an op amp. The LM604 can select, buffer, and amplify one of four different input signals, providing a complete system for multiplexing analog signals. It also has the unique Bi-State output which allows two or more Mux-Amps to be connected together at their outputs to increase the number of multiplexed channels. Channel selection and the Bi-State (Active and Disabled) output are controlled by internal logic that interfaces directly to a microprocessor. In addition, the LM604 has excellent AC and DC op-amp specifications and is internally compensated. Applications include signal multiplexing and linear circuits that are controlled by digital signals (e.g. programmable gain blocks and filters).

$\begin{array}{l} \underline{Op\ Amp:}\\ Offset\ Voltage \leq 3\ mV\\ Bias\ Current \leq 80\ nA\\ Supply\ Current \leq 9\ mA\\ Gain-Bandwidth\ Product \geq 6\ MHz\\ Slew\ Rate \geq 2\ V/\mu s\\ Output\ Can\ Drive\ 600\Omega \end{array}$

$\begin{array}{l} \underline{Multiplexer:}\\ Enable Time \leq 4\ \mu s\\ Disable Time \leq 2\ \mu s\\ Channel-Switching Time \leq 5.5\ \mu s\\ Channel-to-Channel Isolation 100\ dB\\ TTL Inputs for Mux Control \end{array}$

#### LM611, LM614

The LM611 contains an adjustable voltage reference and a single-supply operational amplifier; the LM614 contains the same reference but with four single-supply op amps. The voltage reference is a three-terminal shunt-type bandgap similar to the adjustable LM185, but with improved voltage accuracy of better than 2% for the commercial grade, trimmed to better than 0.4% for the prime-grade device. The reference features operation over a current range of 16  $\mu$ A to 20 mA, low dynamic impedance, and broad capacitive load tolerance range. The op amp is similar to the LM324, but with improved slew rate and power bandwidth. Its input voltage range extends to ground when operated from a single supply.

#### Op Amp:

Offset Voltage  $\leq 5 \text{ mV}$ Bias Current  $\leq 35 \text{ nA}$ Supply Current  $\leq 300 \mu\text{A} \text{ (LM611)}$ Supply Current  $\leq 1 \text{ mA} \text{ (LM614)}$ Gain-Bandwidth Product 0.8 MHz Slew Rate  $\geq 0.5 \text{ V/}\mu\text{s}$

#### Reference:

Initial Voltage  $1.244V \pm <2\%$ Ave. Drift  $\le 20$  ppm/°C (Prime grades) Adjust Range 1.2V to 6.3V

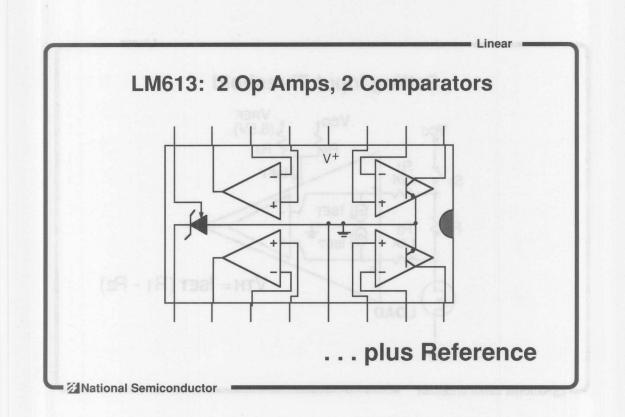

#### LM613

The LM613 contains an adjustable voltage reference, two single-supply operational amplifiers, and two single-supply comparators. The reference and op amps are as described above for the LM611 and LM614. The comparators are similar to those in the LM339 and, like the op amps, have an input range that extends to ground when operated from a single supply.

Op Amps and Reference: (see LM611 & LM614 description)  $\label{eq:comparators:} \begin{array}{l} \underline{Comparators:} \\ Offset \ Voltage \leq 5 \ mV \\ Bias \ Current \leq 35 \ nA \\ Response \ Time \ 1.5 \ \mu s \end{array}$

he LMGAK Mox Armp is an op-amp with four selectable officiential inputs, combining the functions of multiplexer with an op amp. The LMBOA can select buffer, and amplity one of four different input graph, providing a complete system for multiplexing analog signals. If also has the unique to State arout which allotts two or more Mux Armps to be connected together at their outputs to increase at a mount of multiplexed dramets. Channel sate close and the Bi-State (Active and Directed) output or connected by internal logic that interferes directly to a microprocessor. In addition, the LARCH as excellent AG and DC op amp spot frating and its internally connected. Applications include one analogicating and threat dramets that are controlled by digital agress (e.g. programmable guita and multiplexed.

> Nor 8 An 9 Am 9 1999 S 4 Bouldon P 20

SUPER-BLOCKs<sup>™</sup> are being used in many environmental and industrial control systems, as well as product test systems.

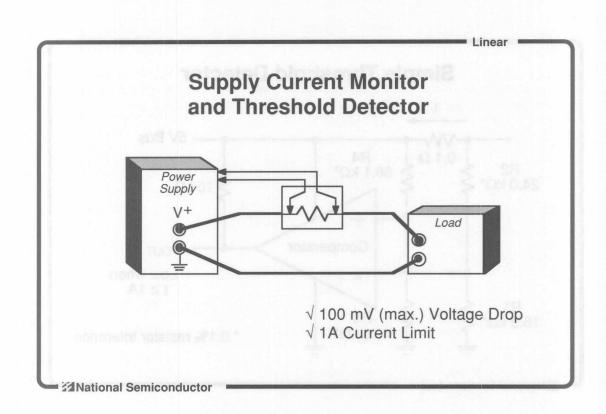

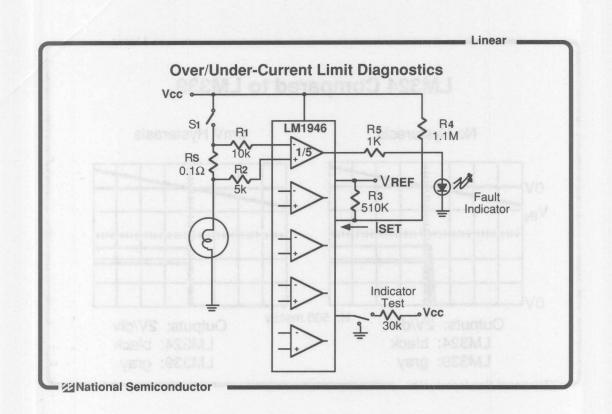

In many of these systems, a load's supply current indicates whether or not it is operating properly, and how it is operating. The monitoring of the supply current and detection of excessive supply current can improve the system's safety and control. However, the monitoring element (usually a resistor) must not cause the load's supply voltage to drop substantially and must not consume too much power. In the following example, a circuit is needed to produce a logic "flag" when the current exceeds 1A, and a voltage proportional to the current which can be monitored on a meter. The current will exceed 1A only in a fault condition, and the maximum allowed voltage drop in the 5V supply is 100 mV at 1A.

This circuit must be delicately situated, as the ourient treations relative directly depends on the circuit must be delicately depends on the circuit of the 30 true and the value of the target relation. The relative directly add only 6.4% to a relation of 0.1% registers and used.

This sitcent has several problems. Although the communicer's 10 trA outplit sink current adds 1 m v systemates. It is not enough to prevent occuration first as the times vehicle randoms the lineshold. To breaking the pink domaid to raids then 10 mA is not practical for todat comparative, and relating hys terrain with positive tocober's would moreaser the comparator's oftent vollage, reducing the acturator of the dirocut to ecober's would moreaser the comparator's oftent vollage, reducing the acturator of the dirocut to ecober's would moreaser the comparator's oftent vollage, reducing the acturator of the dirocut to economic that are processed at the when the current proceeds the 14 find's often

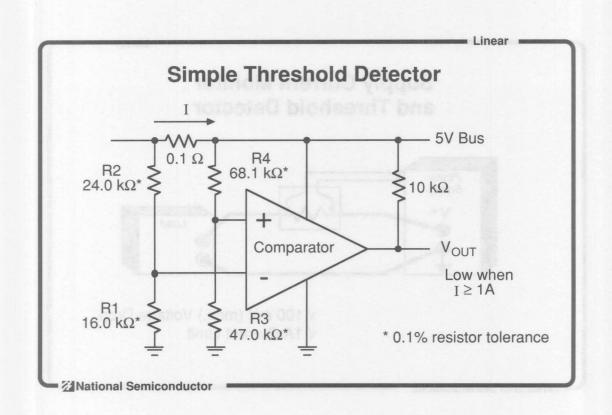

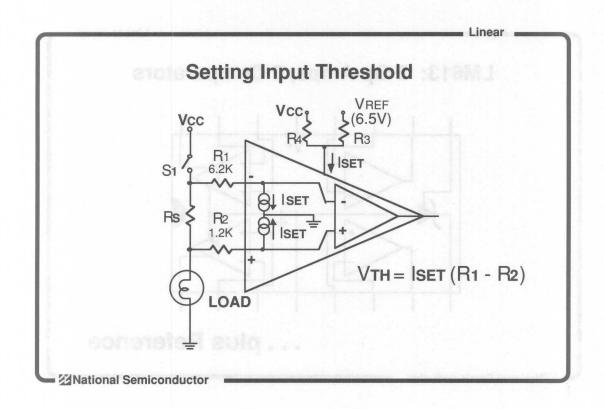

The simplest monitor uses a 0.1 $\Omega$  sense resistor to develop 100 mV with 1A supply current. Comparing the sense voltage to a 100 mV reference would provide a simple threshold detection. However, standard comparators cannot detect input signals at the level of their positive supply because their input range is normally limited to 0V  $\leq$  V<sub>IN</sub>  $\leq$  3.5V. Thus, the next best approach is to divide down the bus voltage (minus the sense voltage) to a level within the comparator's input range and compare it to a reference derived from the input supply.

The threshold to the inverting input of the comparator is set at 2.00V (using a voltage divider from the 5V bus). With no voltage drop across the sense resistor, the non-inverting input is at 2.04V. When the sense resistor's voltage becomes greater than 100 mV, the comparator's non-inverting falls below 2.00V, causing the output to switch low. In equation form, the output is low when  $I \ge 0.1\Omega > 5V \ge [R3/(R3 + R4) - R1/(R1 + R2)]$

This circuit must be delicately adjusted, as the current threshold tolerance directly depends on the tolerance of the 5V bus and the value of the sense resistor. The resistive dividers add only 0.4% tolerance if 0.1% resistors are used.

This circuit has several problems. Although the comparator's 10 mA output sink current adds 1 mV hysteresis, it is not enough to prevent oscillation just as the sense voltage reaches the threshold. Increasing the sink current to more than 10 mA is not practical for most comparators, and adding hysteresis with positive feedback would increase the comparator's offset voltage, reducing the accuracy of the circuit. In addition, this circuit only produces a flag when the current exceeds the 1A limit; a linear monitor voltage was also needed.

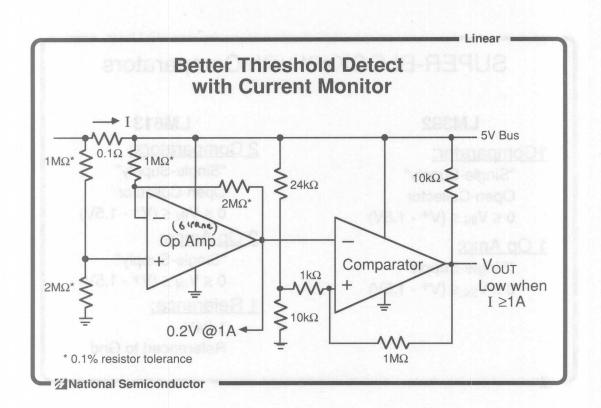

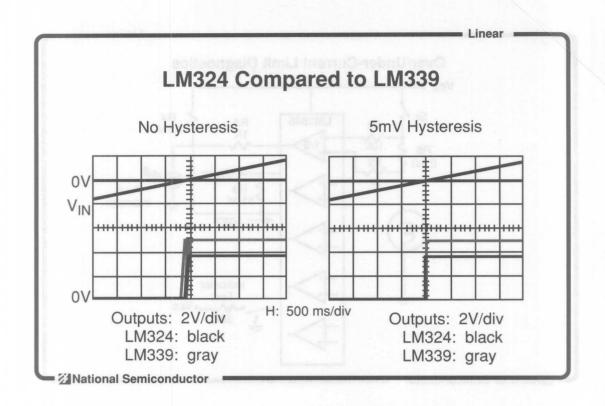

The simple detector can be improved by adding an op amp to separate the sensing function from the detecting function. This increases the gain of the circuit, and allows the addition of hysteresis to the comparator.

The op amp differentially amplifies the sense voltage by 2, providing a monitor output of 0.2V/A. This voltage is then compared to a threshold created by dividing down the 5V bus. 5 mV of hysteresis added to the comparator adds 2.5% error which can be eliminated by adjusting the threshold voltage.

The differential amplifier's resistors must still be precision, but they now have more convenient values and can be part of a precision resistor network. The resistor values are kept large to minimize the output sink current required of the op amp when its output voltage is expected to be near 0V. (Most single-supply op amps cannot produce an output of less than 0.4V when sinking more than a few  $\mu$ A.)

# SUPER-BLOCKs<sup>TM</sup> with Comparators

## LM392

$\frac{1Comparator:}{"Single-Supply"}$  Open-Collector  $0 \le V_{IN} \le (V^+ - 1.5V)$

<u>1 Op Amp:</u>

"Single-Supply"  $0 \le V_{IN} \le (V^+ - 1.5V)$

### LM613

Linear

2 Op Amps:

"Single-Supply"  $0 \le V_{IN} \le (V^+ - 1.5V)$

<u>1 Reference:</u> 1.24V Referenced to Gnd

National Semiconductor

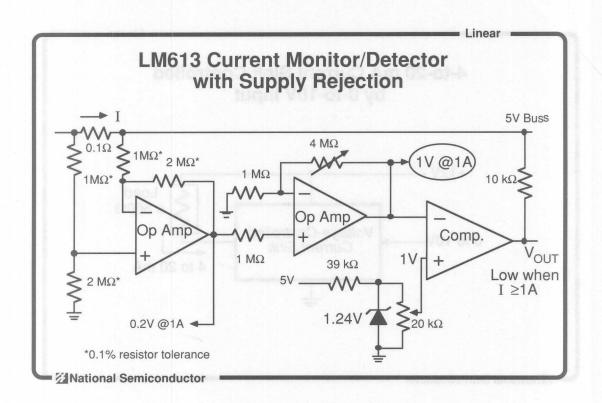

Since the monitor/detector circuit requires both an op amp and a comparator, either of the SUPER-BLOCKs<sup>TM</sup> shown above (having this combination of functions) can be used here.

The LM392 combines a single-supply op amp with a single-supply comparator, so would be an ideal choice. The LM613 would also be appropriate, especially if the extra op amp, comparator, and reference were needed elsewhere in the system. Alternately, the extra components in the LM613 could be used to further improve the convenience and accuracy of the circuit.

Using the second op amp in the LM613, the amplified sense voltage (0.2 A/V) from the first op amp can be further amplified to provide a convenient 1 V/A monitor output.

The LM613's reference, left at its minimum value of 1.24V, can be divided down to create a 1V threshold for the comparator. To prevent oscillation when the bus current is at the threshold, 5 mV of hysteresis could be added as shown previously. As in the previous circuit, the output is high until the buss current exceeds 1A.

Since all the active functions are contained within the LM613, only resistors are needed to construct the circuit.

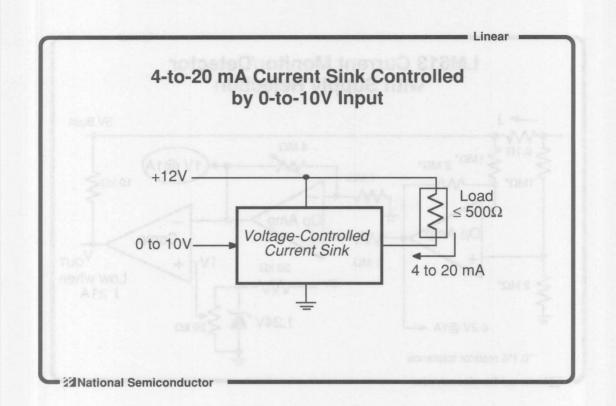

Another industrial control function which can be easily constructed with SUPER-BLOCK<sup>TM</sup> components is a voltage-controlled current sink. The one we will examine draws 4-to-20 mA through a load resistance as great as  $500\Omega$  based on a 0-to-10V input.

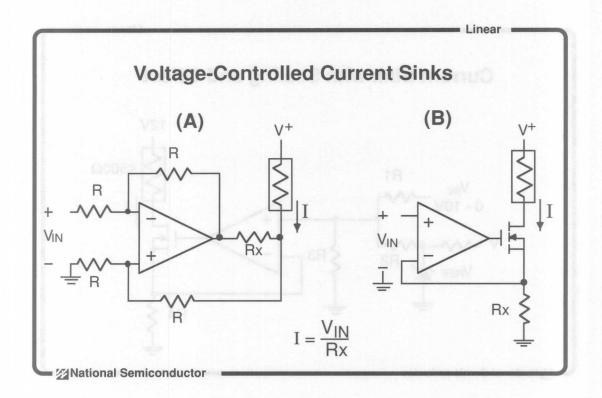

Both current sinks shown above can be voltage-controlled. The appropriateness of each circuit depends on its practical output current range and the compliance range (the allowed voltage swing of the sink's output node).

<u>Circuit A</u> is a current pump which applies the input voltage across the resistor Rx, controlling the load current. Since the load current is being sunk by the op amp via Rx, the op amp must be rated to sink the maximum load current required by the application. With the circuit configured as shown, the compliance range of the output node is (VO(SAT) + VIN) minimum to (V+ - I x RLOAD) maximum, where VO(SAT) is the op amp's lowest guaranteed output voltage.

By adjusting the drive to the MOSFET buffer, <u>circuit B</u> also controls the input voltage across the resistor Rx. The op amp is essentially unloaded, as all the load current is going through the MOSFET and Rx. The compliance range of this sink is ( $V_{IN}$ ) minimum to (V<sup>+</sup> - I x R<sub>LOAD</sub>) maximum.

Since the application being addressed draws up to 20 mA and single-supply operation for the op amp, circuit B is more favorable because it can use a low-power single-supply op amp while the MOSFET carries the load.

An additional reason for using the buffered current sink of circuit B is that it offers a greater compliance range. When  $V_{IN}$  is at its maximum level the 500 $\Omega$  load is conducting 20 mA; on a 12V supply, this leaves only 2V for the current sink driver.

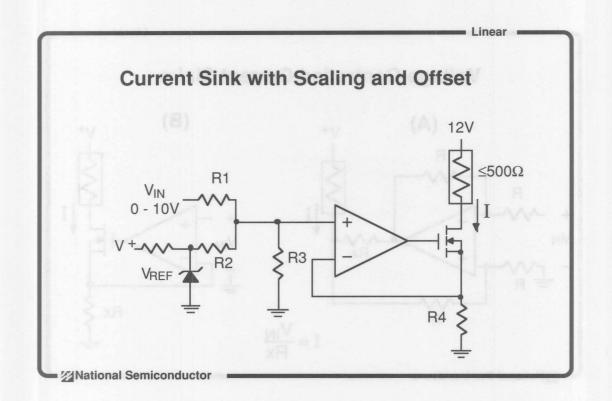

Since the circuit's input voltage is 0 to 10V, and the maximum voltage allowed across the current sense resistor is 2V, the input voltage must be prescaled before being applied to the op amp input. In addition, the minimum load current is to be 4 mA when  $V_{IN} = 0V$ ; this requires that an offset be added to the input voltage.

The circuit shown above uses R4 as the current sense resistor. The prescaling with offset is done with R1, R2, and R3:

$$I = \frac{V_{IN} \times X + V_{REF} \times Y}{B4}$$

where

$$X = \frac{1/R1}{1/R1 + 1/R2 + 1/R3}$$

and

Y

$$=$$

$\frac{1/R2}{1/R1 + 1/R2 + 1/R3}$

|                                     | SUPER-BI<br>Op Amp a            |                              |                              |                              |

|-------------------------------------|---------------------------------|------------------------------|------------------------------|------------------------------|

| Op Amp(s)                           | LM10                            | LM611                        | LM613                        | LM614                        |

| Per Pkg.<br>Input Range* (V)        | 1<br>0 to 4.15                  | 1<br>0 to 3.6                | 2<br>0 to 3.6                | 4<br>0 to 3.6                |

| Offset Voltage<br>Bias Current      | ≤4 mV<br>≤30 nA                 | ≤5 mV<br>≤35 nA              | ≤5 mV<br>≤35 nA              | ≤5 mV<br>≤35 nA              |

| Reference                           |                                 |                              |                              |                              |

| Type<br>Adj. Range (V)<br>Tolerance | shunt<br>0.2 to (V+ -1)<br>≤±5% | series<br>1.2 to 6.3<br>≤±2% | series<br>1.2 to 6.3<br>≤+2% | series<br>1.2 to 6.3<br>≤±2% |

| Addtl. Features                     |                                 | Floating<br>Reference        | Incl. Two<br>Comparators     |                              |

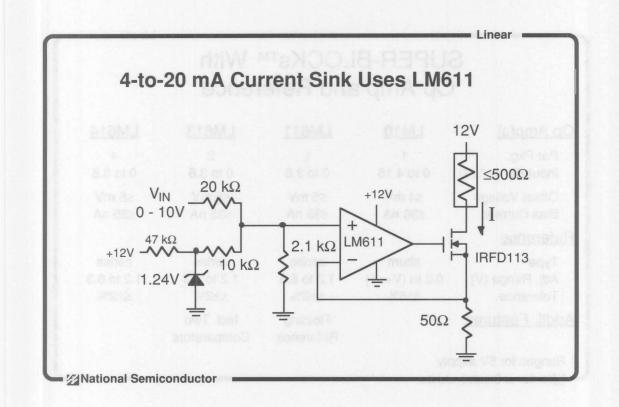

The current sink could be based on any of the SUPER-BLOCKs<sup>™</sup> shown above, which include both an op amp and reference. However, since the minimum voltage across R4 (0.2V) is controlled by the reference, the LM10 reference's 5% tolerance, which cannot be trimmed by the user, will directly affect this offset. It is better to use the higher reference voltage found in the LM611/613/614 (which also has a tighter tolerance than the LM10) and divide it down to the correct level, trimming as necessary. Since only one op amp is needed, the LM611 will be the best choice.

To allow plenty of output compliance, R4 is chosen to be  $50\Omega$  for a maximum voltage drop of 1V at 20 mA. Using the 1.24V reference, X becomes 0.08 and Y becomes 0.16, so that

$R1 = 20 k\Omega$  $R2 = 10 k\Omega$  $R3 = 2.1 k\Omega$

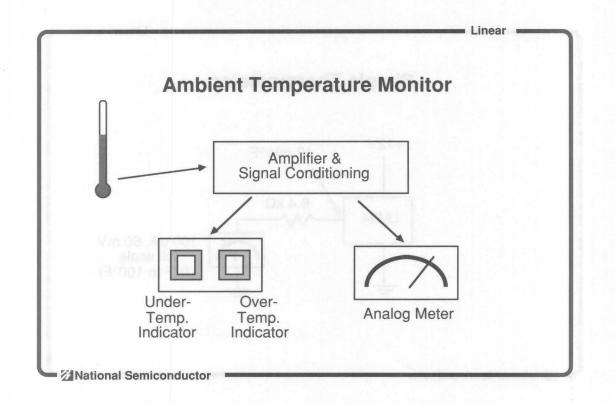

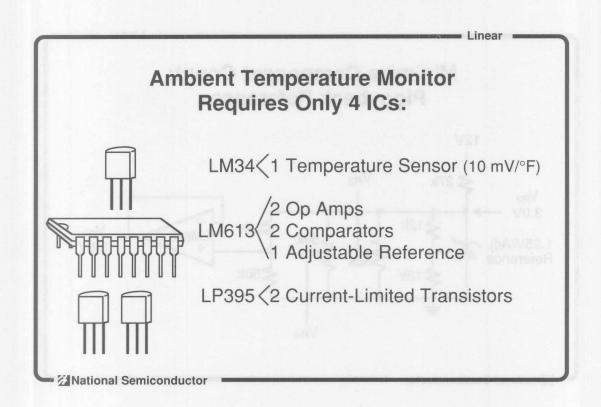

Even simple data-acquisition systems require a variety of linear components, and so can take advantage of the SUPER-BLOCK<sup>TM</sup> combinations. For example, an ambient temperature monitor could be used with an environmental control system. Whether used in a factory assembly plant, office, or greenhouse, this monitor can verify the operation of the heating and cooling, announcing thermal extremes before they become too serious.

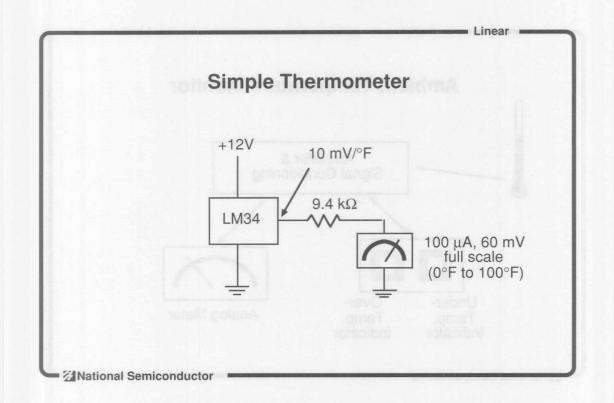

The LM34 only requires a supply voltage between 5 and 30V to deliver its output of 10 mV/°F, which can be used to directly drive the  $600\Omega$  meter to full scale at  $100^{\circ}F$ .

There are two problems with this circuit. First, when powered from a single supply, the LM34's minimum output voltage is 50 mV, representing 5°F, so that the meter cannot show a "zero" reading. The second problem is the wide temperature range covered. To monitor ambient temperature, a more useful full-scale range would be 50°F to 80°F. However, this requires the addition of offset and scaling.

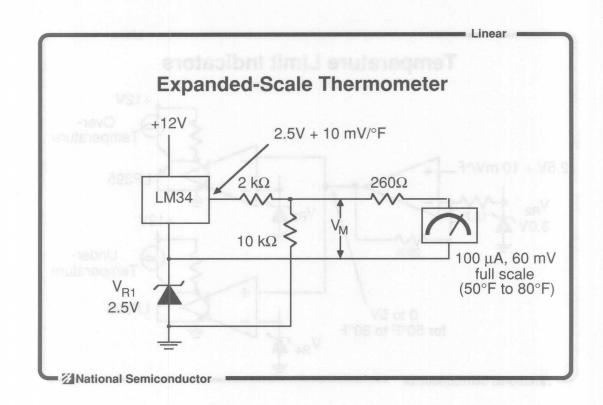

The LM34 temperature sensor is at the heart of this expanded-scale thermometer. Using the reference to provide offset and the three resistors for scaling, the LM34's calibrated 10 mV/°F output translates to 20 mV/°F, with 0V corresponding to 50°F.

The circuit works as follows: The meter current is determined by the voltage,  $V_M$ , across the sum of the 260 $\Omega$  and the meter resistance of 600 $\Omega$  (designated  $R_M$ ).

$$V_{M} = \frac{V_{34} (R_{M} || 10k)}{(2k + R_{M} || 10k)} - \frac{V_{R} (R_{M} || 2k)}{(10k + R_{M} || 10k)}$$

where  $V_{34}$  is the output voltage of the LM34,  $V_R$  is the reference voltage, and "||" indicates "the parallel combination of." The meter current is then  $V_M/R_M$ .

#### BACKGROUND: TEMPERATURE SENSORS

The LM34 is one of a group of temperature sensors. While the LM34 produces 10 mV/°F, the LM35 has an output of 10 mV/°C, and has the same supply voltage range of 5V to 30V. The current-fed LM135 rounds out the trio of voltage-output sensors with its 10 mV/°K output. A related device, the LM134, is a programmable current source proportional to Kelvin temperature. Also available is the LM3911 temperature controller, containing sensor, reference, and comparator - rather like a SUPER-BLOCK<sup>™</sup> itself. These products are described more fully in the Data Acquisition Linear Devices Databook, Chapter 6.

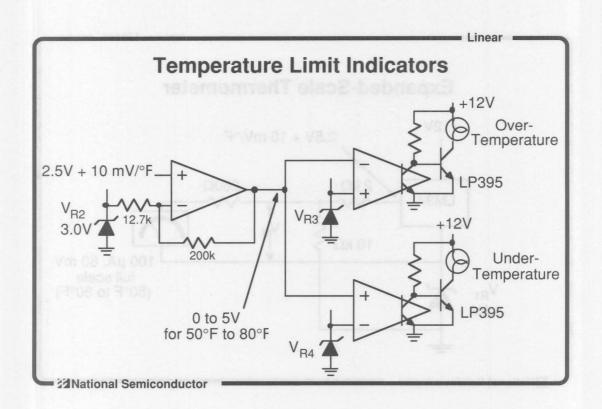

The LM34's output voltage, referred to ground, is its own 10 mV/°Fplus 2.5V from the reference. For the temperature range 50 °F to 80°F this voltage is 3.0V to 3.3V. Using an op amp to subtract 3V, then amplify the remainder by 5/0.3, a monitor voltage is produced that varies from 0 to 5V for a temperature change of 50°F to 80°F. This voltage is then compared against two references, one for an under-temperature indication and one for over-temperature. Each comparator then drives an LP395 current-limited power transistor which turns on a clearly-visible incandescent lamp.

If appropriate, LEDs could be used as the limit indicators. Since many types of LEDs can be directly driven by the comparators, they would replace the pullup resistor, LP395 and incandescent lamp.

The 0-to-5V monitor voltage can also be sent to the environmental controller, to serve as part of its feedback.

Trai 1.1034 is one of a group of thrigenstare versors. While the 1.134 produces 10 mV/F, the UM1 has an output of 10 mV/C, and the the same staply voltage range of 6V to 30V. The committee UA136 reands out the the of voltage ormot samese with its 10 mV/FK output. A related device, the UA136 is a programmable current source proportional to follow temperature. Also available is the UA136 is a programmable current source ensor reference, and comparators. Also available is the UA136 is a programmable current source ensor reference, and comparators. Also available is the UA136 is a programmable current source ensor reference, and comparators reduct like r GUFER UA3611 torrestruce controlling containing ensor reference, and comparators reduct like r GUFER BLOCK\*\*\* start. These removes are described many tilt for the Date Augustion torows Devices Ot

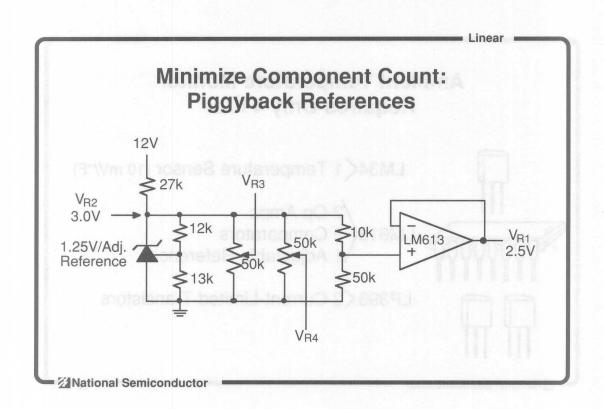

A key to minimizing the cost of a system is to keep the total component count low. "Piggybacking" the references used in this circuit will save the cost of three voltage reference ICs, and can be implemented with two potentiometers and an otherwise surplus op amp.

By using the SUPER-BLOCK<sup>™</sup> LM613 the IC package count can be kept very low. The temperature sensor and the two lamp-driving LP395s are the only additional ICs used, and they are all available in the small TO-92-style plastic transistor package.

Additionally, the LM613, like all the other SUPER-BLOCK<sup>™</sup> components, is available in a surfacemount package.

The growing SUPER-BLOCK<sup>™</sup> family is a valuable tool, especially in industrial controls and test equipment, for providing more efficient use of board space and improved performance over systems using industry-standard equivalent groups of components.

Modeling is a subject that is becoming much more important with each passing month. Using a computer to simulate the function of the electronics circuits has been used for many years because of the inherent simplicity of the digital circuits, analyzing the performance of digital systems by modeling has become an accepted method of design. The results obtained can be used with a high degree of assurance that the circuit will perform as predicted.

Modeling of linear circuits has proven to be much more difficult because the possible number of states that can exist in a linear circuit is an endless job.

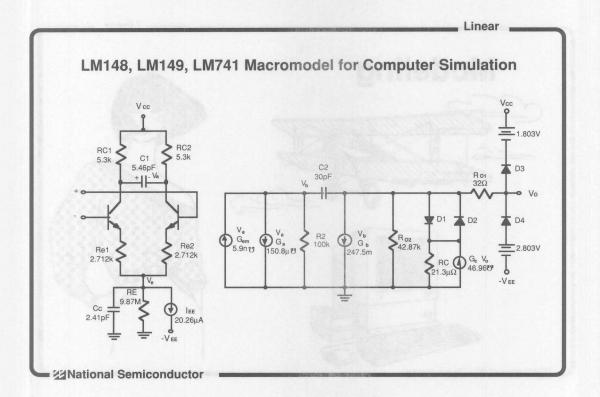

For about the last 15 years, most opamp modeling has been run on SPICE based systems using the basic Boyle macro model illustrated above. This model provides the basic functions of a LM741 type op amp and will run much faster than a more complete component level model.

The disadvantages of this model are several. The model of the transistors used is an approximation of the function of the devices used in the actual IC. Each manufacturer of ICs will use different processes and geometries. This will result in changes in all parameters that will require development of separate models for each different device.

The inclusion of this detailed design information in a model results in the disclosure of information that most manufacturers would consider proprietary.

Other limitations include the reference to ground that is not present in a real op amp and the assumption that the input stage transistors are bipolar NPNs.

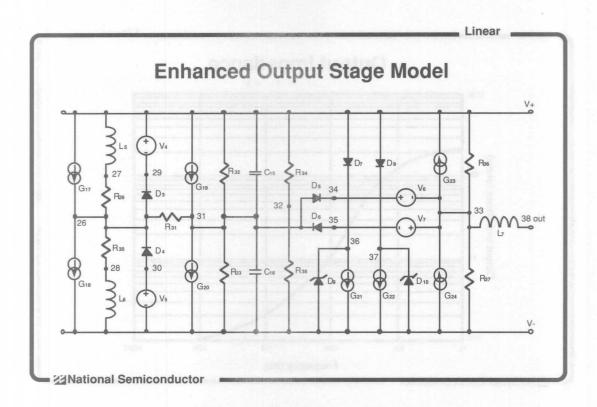

Improvements in the accuracy of the Spice based models are continually being made. The addition of PNP and FET models have allowed more accurate modeling of input stages. Models have also been enhanced by just the addition of many more components. The previous model represents a complete op amp. The example above just models an output stage.

This sort of expansion provides a better representation of the actual circuit performance but because of the greater complexity, will run much slower.

This model, although much more complex than the earlier version, still has several limitations. For example, the output is symmetrical. Most op amp output circuits are not actually symmetrical in output impedance, phase shift or gain. Whenever a PNP transistor is in the signal path to one output device the phase shift will be different than the side with just NPNs.

When using NPN devices in the output stage, one side may be operating common emitter and the other side, common collector. This can cause major differences in the output impedances, depending upon whether the op amp is sourcing or sinking current.

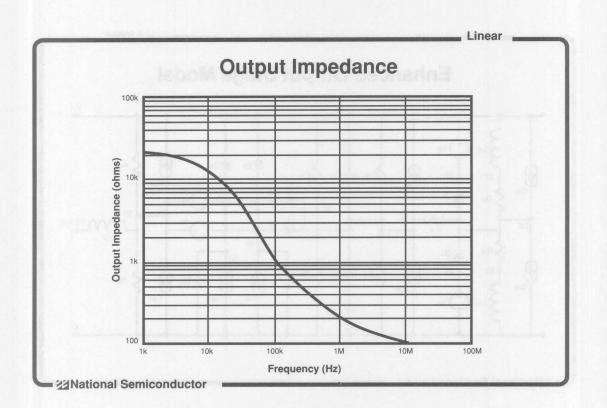

Depending upon the amount and type of AC coupling in the output circuitry, a single inductor-resistor network can be a major over-simplification of the output stage. This graph of an actual op amp illustrates one type of change in output impedance(Ro) with frequency. These changes are usually not apparent in the standard closed loop Ro vs frequency graphs. Under these conditions, the measured Ro is the real Ro divided by the open loop gain. This makes the changes in Ro much less visible.

In the case shown above, the low output impedance at high frequencies enables this op amp to drive capacitive loads that would cause most other op amps to oscillate.

It is true that if enough of the right components are added to the Spice model it should be possible to eventually come up with an accurate model of an op amp. Another approach could be a complete, component level model.

Unfortunately a model using either of these two approaches becomes so complex and runs so slow that even if it will converge, modeling a whole system takes forever.

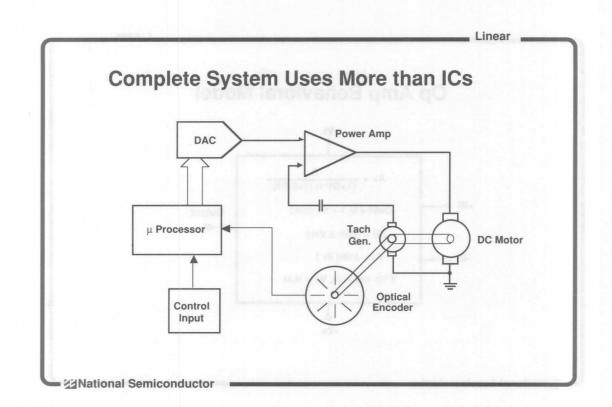

Another basic problem that occurs is that Spice (Simulation Program with Integrated Circuit Emphasis) as its name implies was designed for modeling ICs. Modeling a system as diagrammed above requires changes that involve many components other than the electronic components available in the standard Spice library. Much work has gone into enhancing the original Spice type of modeling systems.

In the sounds too simple and costy, B is. To make the joint frimin legal to output without doing all the increamental calculations requires that the mappines of the system as a whole be known. Unlike the tracky this is much more doint. State if inget apprent. Unlike the tracky this is much more doint. State if inget apprent. Unlike the tracky this is much more doint. State if inget is apprent. Unlike the instance within a conditional that inget apprent. Unlike the tracky the is the track of the system as a whole be known. Unlike the tracky this is much more doint. State if inget is apprent. Unlike the tracky this is much more doint that it is the tracky the tracky the is the tracky tr

its means that a model can not be created that will provide the answer to what will happen unce this remer of beneficient that the option may be upper

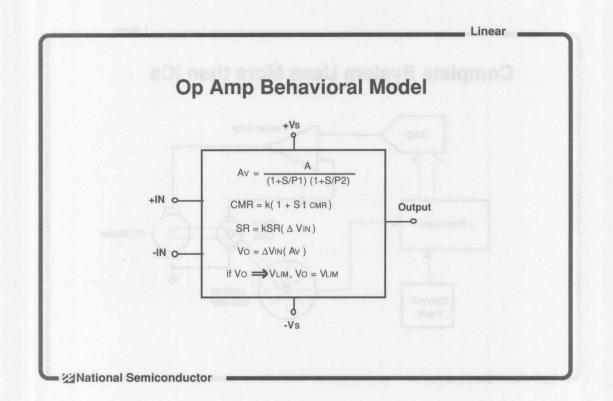

Another method of modeling circuits and systems on computers is described as behavioral modeling. This is where a model is created by representing what it does without necessarily defining what components make up the contents of the device being modeled. By describing the way a system, be it op amp, motor or chemical reaction, reacts to an input, a model can be created. This model can consist of a series of statements in a program, mathematical formulas, Spice type of components or any combination of the above.

The only requirement is that the results of the input be predictable. This means that the possibility exists to predict the outcome of an input without incrementally solving large numbers of matrix equations along the way.

If this sounds too simple and easy, it is. To make the jump from input to output without doing all of the incremental calculations requires that the response of the system as a whole be known. Unfortunately this is much more difficult than it might first appear. During initial characterization, an op amp is tested under a range of conditions that represent the most likely to be encountered. These will be centered around the conditions that will be specified on the data sheet. These tests give an indication of what performance will be like but can not define the full range of possibilities. The production tests will remove units that do not meet the specified requirements under the specific test conditions. There is no practical way to determine accurately what the part is doing outside of these particular conditions.

This means that a model can not be created that will provide the answer to what will happen under the full range of conditions that the op amp may be used.

So far, all we have done is to identify the limitations of modeling systems or the problems in developing good models. What is the best way to create a good, useful model?

The answer is that many different methods may be used to model a system. None of them will give a complete answer. All the methods described require knowledge of characteristics that are subject to random variations.

Behavorial modeling has the inherent ability to model any sort of system that can be described. This flexibility can provide results faster than a mathematically calculated process.

For these reasons and others, we have directed our modeling efforts toward a behavioral system. We are working with Analogy at this time to develop models of our op amps and other components for use on their Saber<sup>TM</sup> modeling system.

Analogy, Inc. P.O. Box 1669 Beaverton, OR 97075-1669 503-626-9700

At present, no one modeling method is best for all applications. In many cases, a bread-board with the actual device in it is an excellent method of verification. The primary limitation is that special sets of devices with a full range of values are not available. This same limitation applies to modeling, as no models exist that exhibit all possible variations and characteristics.

The best method for now and the forseeable future is a combination of modeling, bench testing and most important, working experence with linear systems. Knowledge of the likely problem areas and where to look can add more to the reliability and manufacturability of a design than the best available modeling system. Modeling is a tool that is extremely useful when correctly used. Unfortunately it can not provide useful answers unless the right questions are asked.

Behavorial models for many of National Semiconductors op amps are being developed at the present time. Work is also in progress to develop models of our new Simple Switcher family of switching supply ICs for use on Spice based systems.

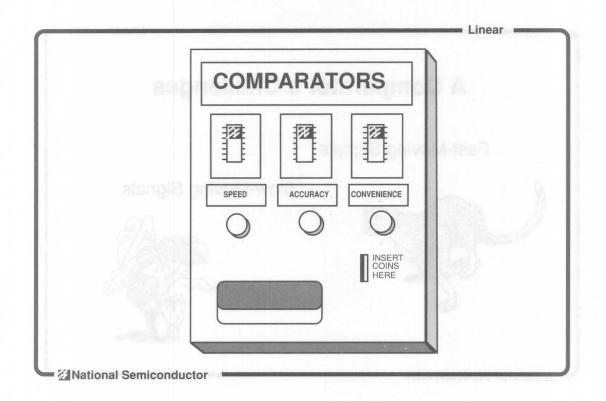

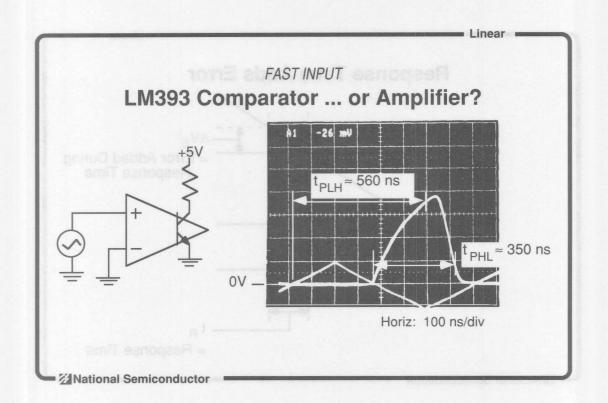

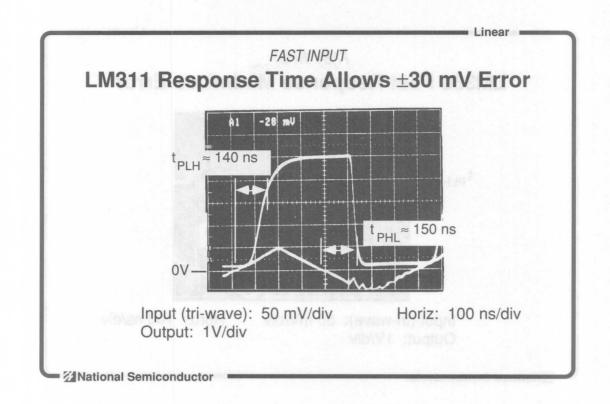

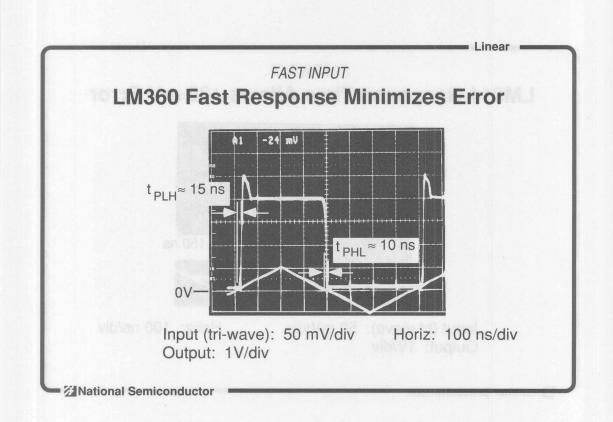

National Semiconductor offers more than 20 types of comparators (not counting variations in grade, temperature range, and package). When choosing one of these comparators for a specific application, the three most important factors to be considered are the comparator's speed, its accuracy, and its convenience.

"Speed" relates to the comparator's response time, not only as specified for a low input overdrive (as is done in most comparator datasheets), but also for the overdrive that will be used in the application. The response times with different overdrives may be drastically different.

"Accuracy" includes the offset voltage and bias and offset currents of the comparator. The offset voltage is the differential input voltage required to make the output voltage move from one specified logic level to the other. The offset voltage, then, relates to the comparator's gain (which is not always specified). The bias current is the average of the two input currents, and will be balanced (within the offset current) only when the input voltages are balanced (the comparator's input stage is in its linear range, and the output is in the middle of switching from one level to the other). When the input stage is unbalanced (the output is at a legitimate logic level), one input current will be zero and the other input current will be 2 x IBIAS.

"Convenience" encompasses the comparator's power supply requirements, its output interface, and other details of operation: Supply current, required supply voltages, whether the output is opencollector, totem-pole or ECL, the number of comparators per package, how well the input is protected against large differential input voltages, and the input voltage range of the comparator.

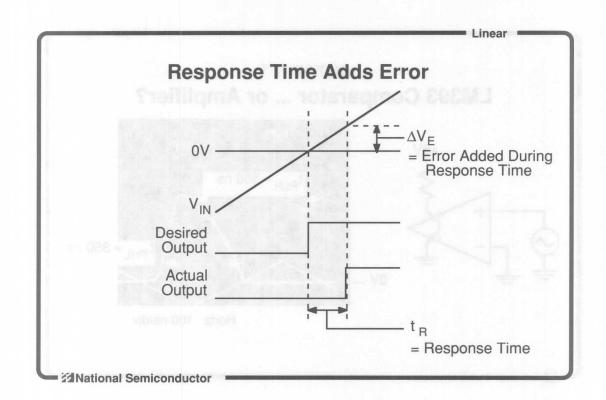

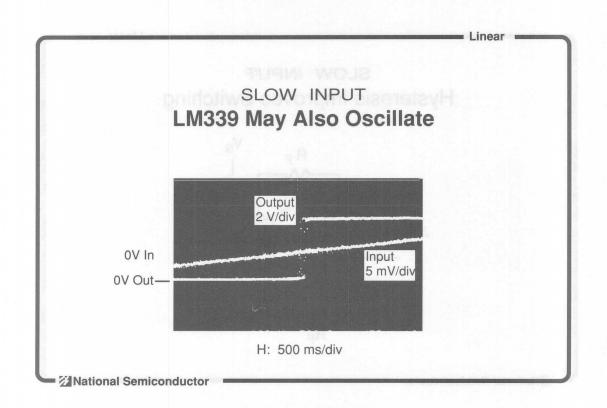

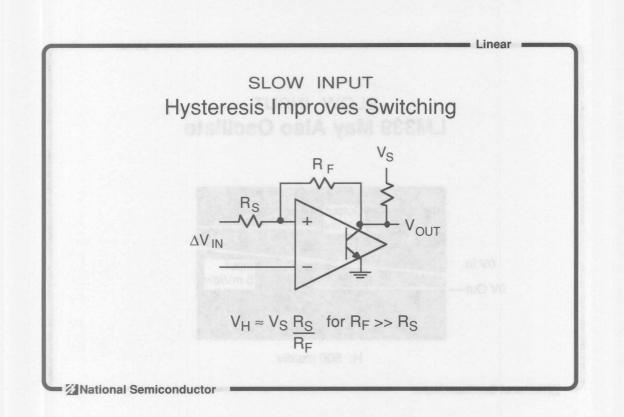

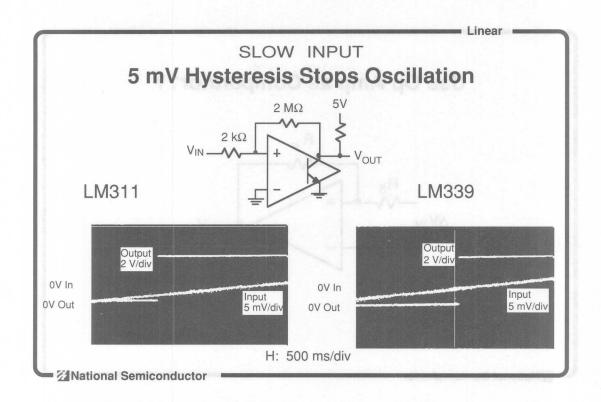

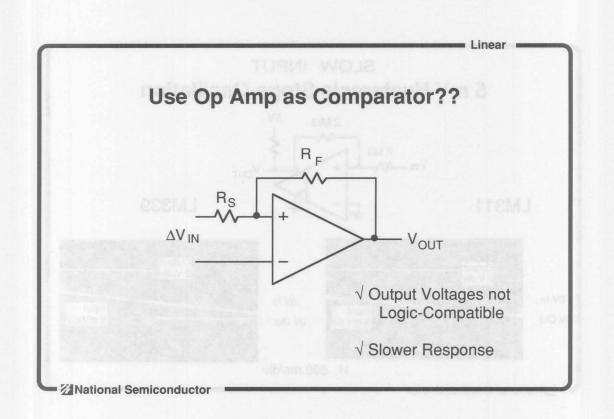

A comparator's greatest challenges are the accurate detection of very fast-moving (high slew-rate) signals and of very slow-moving signals. The terms "fast" and "slow" are relative, and depend on the comparator's own response time for meaning. A comparator detecting a fast signal will produce an output change at the wrong time (after the detection should have occurred) if its response is not quick enough. A comparator attempting to detect a slow signal may oscillate as the input moves through its linear range.

The challenge is increased in both cases if the signal is under 100 mV peak-to threshold. At this level the comparator's offset voltage also adds significant error.

chage is in differential input voltage inquired to mate the output witage move from one tradition by tevel to the other. The other voltage, then, relates to the comparator's gavi (which is not alman bediled). The bass summal is the average of the two argut concerts, and will be batenood (which is not al ourset) only when the input voltages are belonded (the comparator's upput stude in its fires eight and the output is in the most voltages are belonded (the comparator's toput stude in its fires or balanced (the output is at a logitimate logit revel), one input control of be zero and the other in orbalanced without x late is belowing logit revel), one input control of be zero and the other in output without x lates.

Convenience" endempressa the comparator is power supply requirements, its output mischare con other datate of bostnings. Supply smeet, required supply voltages, whether the output is opport collector, rotes date an EGL, the number of comparation principalizing, how well the input is protecting organist range differential input voltages, and the input voltage angle of the comparator.

|                 | Contract of the second s | tor Selectio |           | e                           |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|-----------------------------|