# Use comparator ICs in new and useful ways

You can use the unique differential-input/digital-output characteristics of comparators to implement a wide range of circuit functions.

Jim Williams, National Semiconductor Corp

Perhaps the most underrated and underutilized of monolithic ICs, comparators are among the most flexible and universally applicable components in your design arsenal. With their differential linear inputs and very-fast-switching digital outputs, these devices can help you implement unusual circuit functions at favorable cost and low component count compared with other approaches. Examples ranging from a shaft-angle encoder to a V/F converter show how you can exploit comparators' unique abilities.

#### Variable capacitor makes shaft-angle encoder

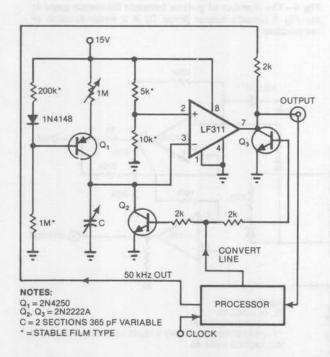

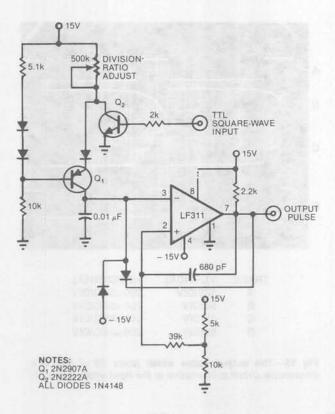

If, for example, you need to convert a shaft angle to a digital bit stream, you can employ Fig 1's comparator-

Fig 1—Employing a variable capacitor and a comparator, a single-supply circuit yields a pulse burst—triggered by a Convert-line HIGH-to-LOW transition—whose duration is a  $\pm 0.1\%$  linear function of the capacitor's shaft angle.

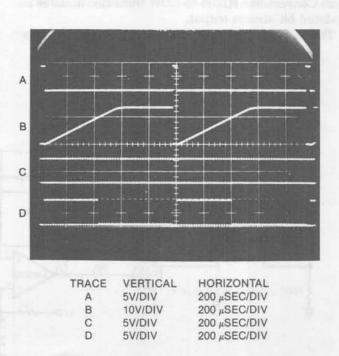

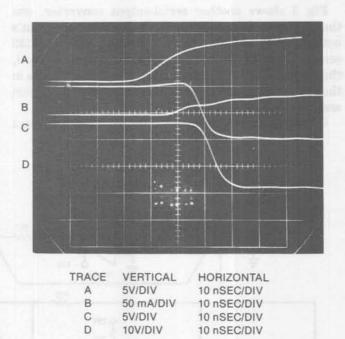

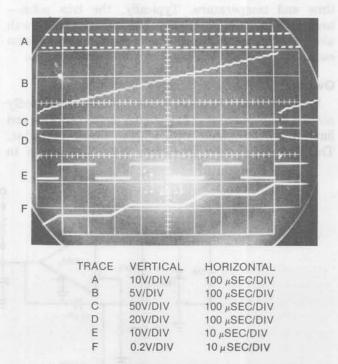

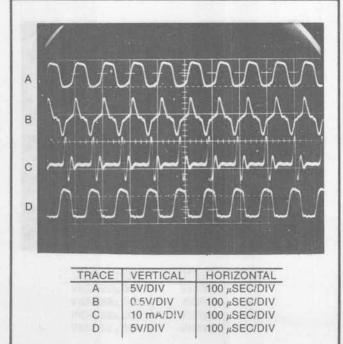

Fig 2—When the linear charging ramp (trace B) of Fig 1's variable capacitor reaches 10V, it signals a comparator to shut off the trace D output pulse burst.

### Obtain shaft-angle readings with a comparator-based circuit

based circuit. It uses a standard AM-radio dual 365-pF variable air capacitor to generate a controllingprocessor-triggered constant-frequency pulse burst. The burst's duration—or the number of pulses it contains—indicates shaft position to within a  $\pm 0.1\%$  typ accuracy. Moreover, the capacitor has essentially infinite life—unlike potentiometers, which can wear quickly and require frequent replacement in high-usage applications such as video arcade games.

In operation, transistor  $Q_1$  and associated components form a ground-referred current source that linearly charges the variable capacitor. When the controlling processor needs a shaft-angle conversion, it drives the Convert line HIGH (**Fig 2**, trace A), turning  $Q_2$  on and discharging the capacitor. Concurrently,  $Q_3$ turns on, forcing the circuit output to zero.

To continue the conversion, the processor pulls the Convert line LOW, and the constant-current-sourcedriven capacitor voltage begins to ramp linearly toward the 15V supply (Fig 2, trace B). This Convert-line HIGH-to-LOW transition simultaneously unclamps the LF311's output, thus triggering a pulse burst by causing the processor's clock (Fig 2, trace C) to appear as a serial bit stream at the output (Fig 2, trace D).

The circuit continues to transmit this bit stream until the capacitor's voltage crosses the level established by the 5-k $\Omega$ /10-k $\Omega$  resistor divider; at that point the comparator output clamps, inhibiting pulses. Note that each Convert-line HIGH-to-LOW transition initiates an updated bit-stream output.

The circuit is insensitive to supply shifts because the

resistor-divider trip point and the current-source reference are ratiometrically related. The FET-input comparator does not appreciably load other circuit components, so linearity is excellent. With a standard variable air capacitor (General Radio Type 722) substi-

tuted for the dual 365-pF unit, linearity is well within  $\pm 0.1\%$ . Use the 1-M $\Omega$  potentiometer to set the desired scale factor.

#### Convert temperatures to bit streams

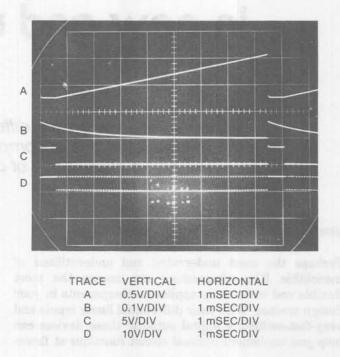

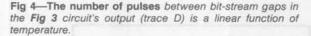

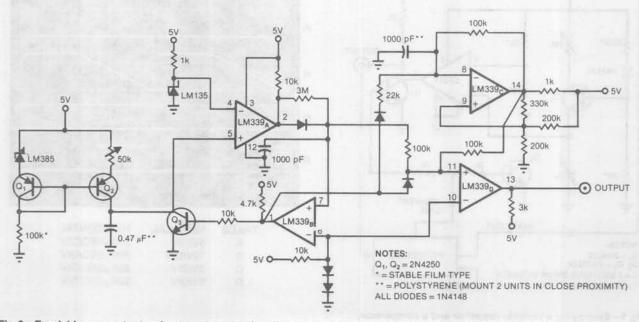

Fig 3 shows another serial-output converter, one that requires only a 5V supply. Generating this circuit's output, which indicates the temperature at the LM135 sensor, doesn't require an external command—instead, the circuit clocks itself continuously and inserts gaps in the output stream to indicate the end of one conversion and the beginning of a new one.

$Q_1$  and  $Q_2$  form a temperature-compensated current

source whose output is referenced to the LM385.  $Q_2$ 's collector current linearly charges the 0.47- $\mu$ F capacitor (Fig 4, trace A) until the ramp voltage exceeds the LM135's voltage. Then, LM339<sub>A</sub>'s output goes HIGH, dumping charge into the 1000-pF capacitor and forcing LM339<sub>B</sub>'s positive input (Fig 4, trace B) and output (Fig 4, trace C) HIGH. This action turns on  $Q_3$ , resetting the ramp capacitor.

The 1000-pF capacitor can discharge only through the 3-M $\Omega$  resistor paralleling the diode at LM339<sub>A</sub>'s pin 2. Therefore, the waveform at LM339<sub>B</sub>'s positive input decays slowly, and the ramp capacitor stays off for an extended period of time. When the 1000-pF capacitor's

## Temperature-sensing scheme uses a 4-comparator IC

voltage finally decays below the 2-diode-drop value at  $LM339_B$ 's negative input,  $Q_3$  turns off, ramping begins and the cycle repeats.

The oscillation frequency varies inversely with the LM135's output voltage. The ramping time, however, is directly—and linearly—proportional to the LM135's output. While the ramp is running, LM339<sub>B</sub>'s output is LOW, and LM339<sub>c</sub>, which functions as a 10-kHz clock, biases LM339<sub>D</sub>, providing the circuit's output. When LM339<sub>A</sub>'s output goes HIGH, the 100-k $\Omega$  resistor path from LM339<sub>A</sub> to LM339<sub>D</sub>'s positive input in turn forces LM339<sub>D</sub>'s output HIGH (Fig 4, trace D).

Reinforcing feedback results when LM339<sub>B</sub>'s output goes HIGH and applies bias through the diode path to LM339<sub>D</sub>'s positive input. This condition lasts until the 1000-pF-capacitor voltage decays to a value sufficiently low for the cycle to repeat. The 22-k $\Omega$  resistor/diode path from LM339<sub>B</sub>'s output to LM339<sub>C</sub>'s negative input synchronizes the 10-kHz clock to the circuit's rampreset sequence, thereby averting a ±1-count uncertainty in the output data.

A monitoring processor can use the gap in the circuit's output bit stream to synchronize itself to the temperature data. To calibrate the circuit, measure the voltage at the LM135 and adjust the 50-k $\Omega$  potentiometer so that the number of bits in each burst relates numerically to this voltage (eg, 2.98V=298 bits).

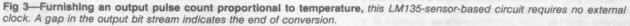

#### Linearize a platinum RTD with comparators

If, instead of an LM135 sensor, you're using platinum

RTDs (resistance temperature detectors) to take advantage of their extremely wide operating-temperature ranges and their long-term stability under adverse environmental conditions, consider the **Fig 5** linearizing

circuit. It overcomes an RTD's inherent nonlinearity  $(>6^{\circ} \text{ error from 0 to 400°C})$  by using an LM339 quad comparator to apply a 4-section breakpoint correction. In contrast to other RTD-linearizing circuits, Fig 5's design needs no calibration.

Because of the RTD sensor's positive temperature coefficient, op amp LF353<sub>A</sub>'s output rises with increasing temperature. Summing the output with a constant current at LF353<sub>B</sub>'s negative input results in a 0V LF353<sub>B</sub> output at 0°C; this output increases as a direct but nonlinear function of the RTD's temperature.

$LF353_B$ 's temperature-dependent output drives the positive inputs of the LM339 comparators and provides the input to the output gain stage,  $LF351_C$ . The threshold voltages at the LM339 negative inputs cause the respective comparators to switch at the LM353<sub>B</sub> voltages corresponding to 100, 200, 300 and 350°C.

When a comparator output switches HIGH, it switches in gain- and offset-changing resistors via the LF13331 JFET switches. The four slight gain adjustments compensate for the RTD's nonlinearity, and the introduced offsets ensure a monotonic increase in output as temperature rises. The 0.05- $\mu$ F capacitors at the LM339 outputs prevent chattering at the trip points; the 1- $\mu$ F capacitor in the LF351's feedback loop eliminates transient switching signals from the output.

If you use the Fig 5 circuit values and RTD sensor, you can obtain  $\pm 0.15$ °C accuracy over 0 to 400°C with no trimming of any kind.

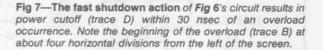

Do you have need to protect expensive components in

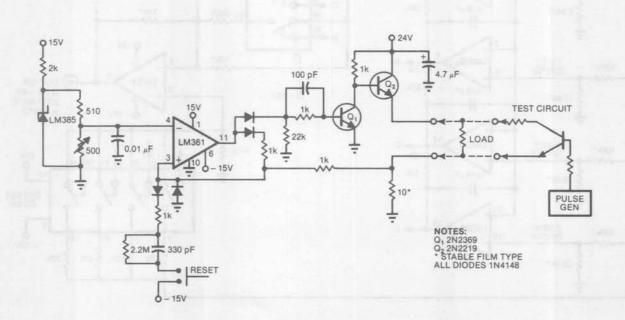

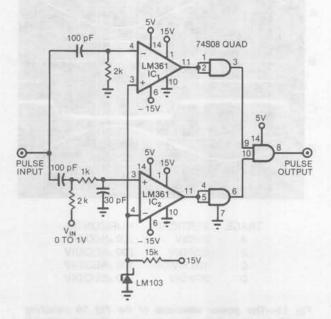

Fig 8—A circuit based on two comparators and an AND gate can generate 6-nsec-wide pulses with 2-nsec rise and fall times. The  $V_{IN}$  level determines pulse width.

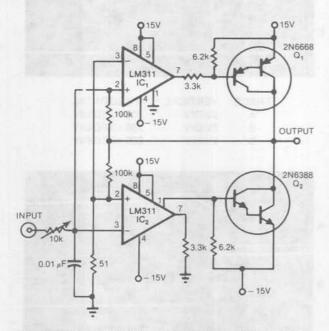

a system—perhaps, for example, during the final phases of trimming and calibration? If so, consider the **Fig 6** circuit—it shuts down power within 30 nsec of an overload occurrence (in this case, for load currents greater than 100 mA).

When the current is less than or equal to 100 mA, the LM361's output is LOW,  $Q_1$  is OFF and emitter follower

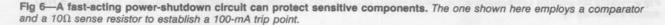

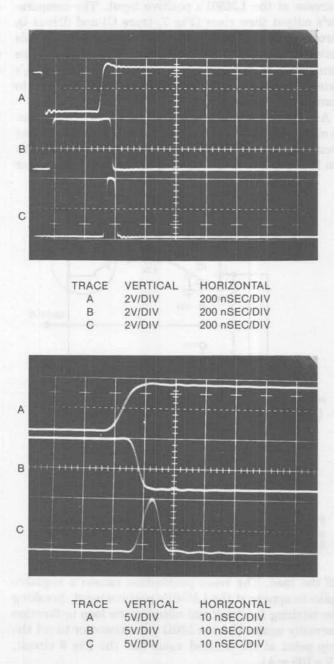

Fig 9—The ANDing action of Fig 8's 74S08 gate yields a narrow pulse ((a), trace C) because of time displacement between comparator outputs (traces A and B). The traces in (b) show the signals at these same circuit nodes for a 100-mV V<sub>IN</sub>.

### Comparator high-speed switching eases pulse-generation tasks

$Q_2$  sources power to the load and the  $10\Omega$  sense resistor. When an overload occurs (in this case via the test circuit, whose output appears in Fig 7, trace A), the current through the  $10\Omega$  sense resistor begins to increase. (Note the slight load-current rise in Fig 7, trace B.)

This rise in current produces a corresponding voltage increase at the LM361's positive input. The comparator's output then rises (Fig 7, trace C) and drives  $Q_1$ through a heavy feedforward network. Although this network degrades the LM361's output rise time somewhat,  $Q_1$  responds very quickly and clamps  $Q_2$ 's base to ground, causing load voltage (Fig 7, trace D) to immediately decay to zero.

As noted, the total elapsed time from overload onset to circuit shutdown is 30 nsec. Once the shutdown has occurred, the resistor-diode network from the LM361's pin 11 to pin 3 provides latching feedback to keep power

Fig 10—A comparator-based 400-Hz switching amplifier is inexpensive, requires few components and can provide a 6A output.

off the load. The reset pushbutton causes a negative spike to appear at the LM361's positive input, breaking the latching feedback and allowing the loop to function normally again. Use the 500 $\Omega$  potentiometer to set the trip point at the desired value (for the Fig 6 circuit, 1V=100 mA).

#### Comparators make 2-nsec pulse generator

Similarly benefiting from the LM361's high-speed performance, the Fig 8 ultra-high-speed pulse generator furnishes voltage-controllable pulse widths. Its differentiator networks generate a pair of pulses with slightly different durations; the comparators and a Schottky TTL gate extract the difference between two widths and present it as a single fast-rise-time pulse at the circuit output.

When you apply a positive input pulse, the two  $100-pF/2-k\Omega$  differentiator networks yield positive outputs. When the positive-going steps exceed the 2V threshold established by the LM103, both LM361s switch output states. For a 0V control input, the differentiator networks and the LM361s respond simultaneously, and both output transitions line up.

As you increase the control voltage, however, the spike produced by  $IC_2$ 's differentiator arrives at the 2V threshold earlier than does that of  $IC_1$ .  $IC_2$  also normally takes longer to decay through the 2V threshold, appearing to lead to a situation in which  $IC_2$ 's output would remain HIGH longer and switch earlier than would  $IC_1$ 's.

$IC_2$ 's 30-pF/1-k $\Omega$  network, however, provides a delay that shifts the  $IC_2$  output so that  $IC_1$ 's leading and trailing edges occur first (**Fig 9a**, traces A and B). The length of time between the comparator outputs' edges depends on the input control voltage.

For the Fig 8 circuit, a 0 to 1V control range produces a trailing-edge timing difference of 0 to 100 nsec. The

Fig 11—The power envelope of the Fig 10 switching amplifier's output (trace D) is sinusoidal when the circuit is driven by a sine-wave input (trace A). Note the high-frequency charging and discharging of the circuit's 0.01- $\mu$ F capacitor (trace C).

### Comparator circuit handles frequency-division chores

DM74S08 ANDs the two comparators' outputs to obtain the single-pulse circuit output (Fig 9a, trace C).

The gate and comparator switching speeds limit the minimum pulse width to 6 nsec; rise and fall times are approximately 2 nsec. Fig 9b shows an example of the high-speed operation that the Fig 8 circuit can achieve (control input=100 mV). Traces A and B represent  $IC_1$  and  $IC_2$  outputs, respectively; trace C is the circuit's output pulse.

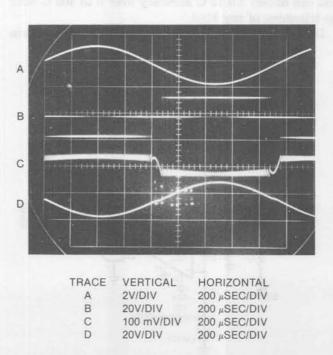

If you need a simple, inexpensive 400-Hz amplifier, consider the Fig 10 circuit. It uses  $\pm 15V$  supplies,

Fig 12—Divide and conquer your frequency-reduction problems with this synchronous circuit. You can vary the division ratio over a 1:1,000,000 range.

provides full bipolar swing and has a 1.5-kHz full-power bandwidth with a 6A pk output capability.

If the input voltage is negative,  $IC_2$ 's output is LOW (note that  $IC_2$  operates in an emitter-follower mode, so its output is in phase with its negative input), cutting  $Q_2$ off. Concurrently,  $IC_1$ 's output goes LOW, turning  $Q_1$ on and thereby driving the load and the 100-k $\Omega$ resistors connected to the comparators' positive inputs. This feedback produces a small voltage at  $IC_1$ 's negative input.

When the 0.01- $\mu$ F capacitor charges to a level high

enough to offset the negative input,  $IC_1$ 's output changes state, turning  $Q_1$  off. At this point, the input draws current from the capacitor, forcing  $IC_1$ 's positive input to a lower state and consequently driving  $IC_1$ 's output LOW again, turning  $Q_1$  on.

The switching action occurs continuously; repetition rate depends on the input voltage. For positive inputs,  $IC_2$  and  $Q_2$  perform similar action. To avoid crosscurrent conduction in the output transistors, tie the comparators' offset-adjust terminals to the 15V supply.

Fig 11 trace B shows the circuit output resulting from the trace A input; the trace C waveform represents current flow in and out of the capacitor. (Think of the IC<sub>2</sub> pin 3 point as a digitally driven summing junction.) Trace D is a lightly filtered version of trace B; it clearly shows that the circuit output has a sinusoidal power envelope. You can vary the amplifier gain with the 10-k $\Omega$  input potentiometer.

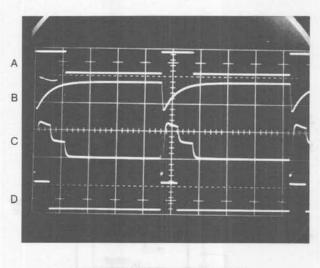

#### Divide frequencies over a 1:1,000,000 range

Using the Fig 12 circuit, you can divide a frequency over a 1:10<sup>6</sup> range, adjustable via a single potentiometer. Moreover, the output frequency you obtain is synchronously related to the input frequency. You can use this circuit to obtain simultaneous oscilloscope observations of low-frequency signals and the fast clock

Fig 13—Using a step-charging technique that results in the trace B capacitor voltage, Fig 12's circuit yields an output frequency proportional to and synchronized with an input signal's frequency (trace A). In the example shown here, the output (trace C) contains a pulse after 32 input pulses.

## Manipulate pulses with comparator-based circuits

from which they're derived or to synchronously trigger an A/D converter at a variable rate.

The circuit functions by step-charging a capacitor with a switched current source and using a comparator to determine when to reset the capacitor. Fig 13, trace B, shows the step-charging waveform; each time the pulse input (Fig 13, trace A) goes LOW, a currentsource pulse causes a capacitor-voltage positive step. You can control the step height—and therefore the division ratio—with the 50-k $\Omega$  potentiometer.

When the staircase waveform reaches the voltage at the LF311's positive input, the comparator output goes LOW (Fig 13, trace C) and stays LOW until the positive feedback through the 680-pF capacitor ceases. The delay produced by this feedback ensures a complete reset for the 0.01- $\mu$ F capacitor, which discharges through the steering diode into the comparator output.

The diode connected from LF311 pin 3 to -15V provides first-order compensation for the steering diode's leakage effects during the charge cycle. Fig 13, trace D, shows the waveform at the LF311's positive input. Traces E and F show in an expanded time scale the relationship between the input waveforms and the step-charged ramp.

When using this circuit, remember that although the output frequency is always synchronously related to the input frequency, its absolute value can vary with time and temperature. Typically, the trip point hence, the output frequency—moves back and forth along the horizontal portion of a step at low division ratios and changes from step to step at high ratios.

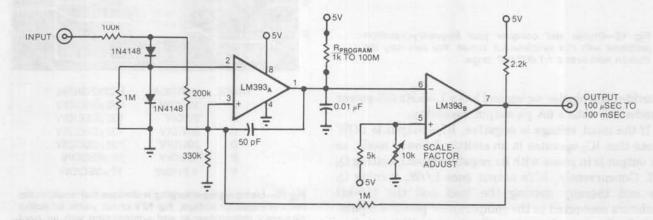

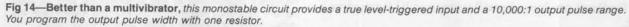

#### Overcome TTL multivibrators' shortcomings

If you've used TTL monostables, you've undoubtedly noticed their poor input triggering characteristics and limited dynamic range with a given timing capacitor. The **Fig 14** circuit surmounts these limitations to provide a true level-triggered input and a singleresistor-programmable 10,000:1 output-pulse range. It delivers a preprogrammed output pulse width regardless of the input pulse duration. (The minimum input trigger-pulse width is, however, 3  $\mu$ sec.)

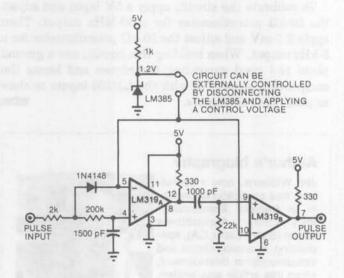

When you apply an input pulse (Fig 15, trace A) to the circuit, LM393<sub>A</sub>'s output goes LOW (Fig 15, trace B), producing reinforcing feedback for its own positive input (Fig 15, trace C). This causes LM393<sub>B</sub>'s output to go HIGH, providing additional feedback to LM393<sub>A</sub>'s positive input via the 1-M $\Omega$  resistor.

When the 50-pF capacitor ceases to provide feedback

| TRACE | VERTICAL | HORIZONTAL   |

|-------|----------|--------------|

| A     | 10V/DIV  | 200 µSEC/DIV |

| В     | 5V/DIV   | 200 µSEC/DIV |

| С     | 1V/DIV   | 200 µSEC/DIV |

| D     | 5V/DIV   | 200 µSEC/DIV |

Fig 15—The output pulse width (trace D) of Fig 14's monostable circuit is insensitive to the input width (trace A).

## Make a better monostable with a 2-comparator IC

to LM393<sub>A</sub>'s positive input, this comparator's output goes HIGH, allowing the 0.01- $\mu$ F timing capacitor to charge (Fig 15, trace B). When the capacitor voltage exceeds LM393<sub>B</sub>'s positive input voltage, LM393<sub>B</sub>'s output (Fig 15, trace D) goes LOW, terminating the output pulse.

With the 0.01- $\mu$ F timing capacitor, you can obtain output pulse widths of 10  $\mu$ sec to 100 msec, with a scale factor (trimmable with the 10-k $\Omega$  potentiometer) of 100 $\Omega/\mu$ sec.

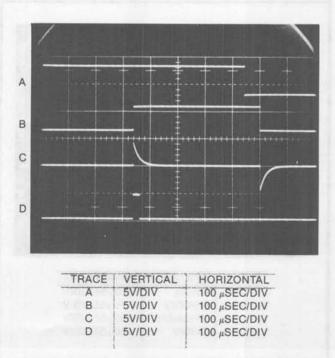

#### Get variable width and delay with one IC

If you need a known-width pulse that's delayed with respect to another pulse, consider the **Fig 16** circuit. It works from one 5V supply and requires only one dual-comparator IC.

When you apply a TTL input (Fig 17, trace A), LM319<sub>A</sub>'s output stays LOW until the 1500-pF capacitor at its positive input charges beyond the negative input's 1.2V level. The resistor-diode clamp from the circuit input to LM319<sub>A</sub>'s pin 5 provides immunity to input-amplitude variations.

Fig 16—Form a pulse having the parameters you need from this simple 1-IC circuit. The 1500-pF/200-k $\Omega$  network determines delay relative to a triggering pulse; the 1000-pF/22-k $\Omega$ differentiator sets the width.

When LM319<sub>A</sub>'s output goes HIGH (Fig 17, trace B), the transition is coupled via the 1000-pF/22-k $\Omega$  differentiator to LM319<sub>B</sub>'s positive input (Fig 17, trace C), causing LM319<sub>B</sub>'s output to rise and stay HIGH (Fig 17, trace D) until the differentiator output drops below the 1.2V level at LM319<sub>B</sub>'s negative input.

You can tailor both the delay time and the output

pulse width to your requirements by altering the values of the RC networks. Alternatively, you can control these parameters externally by applying variable voltages to the comparators' negative inputs.

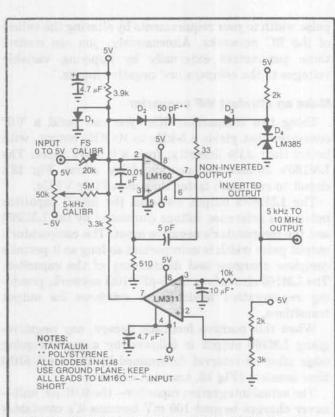

#### Make an ultrafast V/F converter

Using two comparator ICs, you can build a V/F converter that yields a 5-kHz to 10-MHz output, with better than  $\pm 1\%$  linearity, from a 0 to 5V input. The LM160's 20-nsec propagation delay allows **Fig 18**'s circuit to run much faster than monolithic VFCs.

The LM160's output switches the 50-pF capacitor between a reference voltage (furnished by the LM385) and the comparator's negative input. The comparator's output pulse width is unimportant so long as it permits complete charging and discharging of the capacitor. The LM160 also drives the 5-pF/510 $\Omega$  network, providing regenerative feedback to reinforce its output transitions.

When this positive feedback decays, any negativegoing LM160 output is followed by a positive-going edge after an interval determined by the  $5\text{-pF}/510\Omega$ time constant (Fig 19, traces A and B).

The actual integration capacitor—the 0.01-µF unit never charges beyond 100 mV because it's constantly reset by charge dispensed from the switched 50-pF capacitor (**Fig 19**, trace C). When the LM160's output goes negative, the 50-pF capacitor takes charge from

Fig 17—A delayed narrow pulse (trace D) from Fig 16's 1-IC circuit specs delay and width of 340 and 30 µsec, respectively.

## Two comparator ICs yield a fast, linear VFC

Fig 18—Producing 5-kHz to 10-MHz output, this V/Fconverter circuit uses two comparator ICs and features  $\pm 1\%$ linearity. The LM160 is the heart of the converter; the LM311 prevents lockup.

Fig 19—A clean 10-MHz output (trace D) results from an LM160's action in Fig 18's V/F converter. Trace C shows the charge-dispensing current from Fig 18's 50-pF capacitor. the 0.01-µF capacitor, resulting in a lower voltage.

The LM160's negative-going output also produces a short negative pulse—via the 5-pF/510 $\Omega$  feedback—at its positive input. When this negative pulse decays to a point where the positive input is just higher than the negative input, the 50-pF capacitor again receives a charge, and the entire cycle repeats. Diodes D<sub>1</sub> and D<sub>2</sub> compensate for diodes D<sub>3</sub> and D<sub>4</sub>, minimizing temperature drift.

The LM160's inverted output (Fig 19, trace D) serves as circuit output and also drives the LM311 comparator circuit to prevent LM160 lockup. Without it, any condition (such as startup and input overdrive) that allows the 0.01- $\mu$ F capacitor to charge beyond its normal operating point could cause the LM160's output to go to the -5V rail and stay there.

The LM311 prevents lockup by pulling the LM160's negative input toward -5V. The  $10-\mu F/10-k\Omega$  network determines when the LM311 switches on. When the VFC runs normally, the  $10-\mu F$  capacitor charges to a negligibly small voltage, holding the LM311 off. The LM160's inverted output stays HIGH if the VFC stops running (if lockup occurs), forcing the LM311 to turn on and restarting the circuit.

To calibrate the circuit, apply a 5V input and adjust the 20-k $\Omega$  potentiometer for a 10-MHz output. Then apply 2.5 mV and adjust the 50-k $\Omega$  potentiometer for a 5-kHz output. When building this circuit, use a ground plane and good grounding techniques and locate the components associated with the LM160 inputs as close as possible to the inputs.

#### Author's biography

Jim Williams, now a consultant, was applications manager in National Semiconductor's Linear Applications Group (Santa Clara, CA), specializing in analog-circuit and instrumentation development, when this article was written. Before joining the firm, he served as a consultant at Arthur D Little Inc and directed the Instrumentation Develop-

ment Lab at the Massachusetts Institute of Technology. A former student of psychology at Wayne State University, Jim enjoys tennis, art and collecting antique scientific instruments in his spare time.