# TOSHIBA

FILE NO. 526-9401

# VIDEO WALL PROJECTION UNIT P4100U

# **SERVICE TEXT**

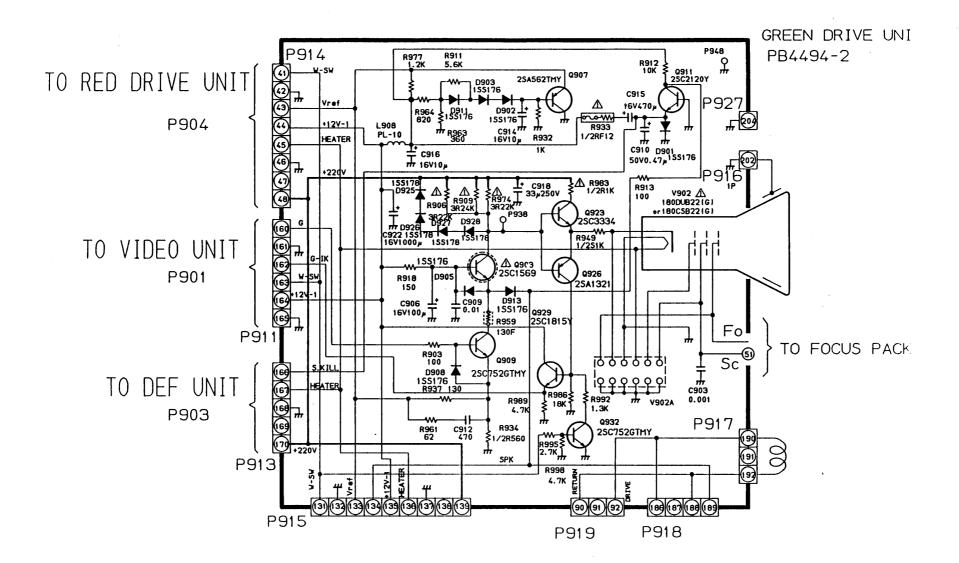

# **TOSHIBA CORPORATION**

PRINTED IN JAPAN APR., 1994 So

# CONTENTS

### SECTION 1 INTRODUCTION

| INT  | RODUCTION           | 1-1 |

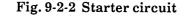

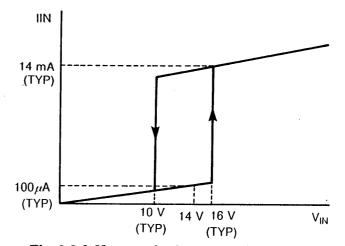

|------|---------------------|-----|

|      | DESCRIPTION         |     |

|      | FEATURES            |     |

| 1-3. | LIST OF UNITS       | 1-3 |

| 1-4. | NAME AND DIMENSIONS | 1-3 |

| 1-5. | SPECIFICATIONS      | 1-4 |

| 1-6. | BLOCK DIAGRAM       | 1-5 |

| 1-7. | PARTS ARRANGEMENT   | 1-6 |

...4

| •   |

|-----|

| 2-1 |

| 2-2 |

|     |

| 2-2 |

| 2-2 |

| 2-2 |

| 2-3 |

| 2-3 |

| 2-3 |

| 2-4 |

| 2-4 |

| 2-4 |

| 2-5 |

| 2-6 |

| 2-6 |

| 2-7 |

| 2-7 |

|     |

| 2-7 |

|     |

$\mathcal{A}$

# **SECTION 3**

----

| MIC   | ROPROCESSOR                    | 3-1  |

|-------|--------------------------------|------|

| 3-1.  | OUTLINE OF SYSTEM              | 3-2  |

| 3-2.  | SYSTEM MICROPROCESSOR          | 3-4  |

| 3-3.  | POWER RESET BLOCK              | 3-7  |

| 3-4.  | <b>REMOTE CONTROL RECEIVER</b> |      |

|       | BLOCK                          | 3-8  |

| 3-5.  | RS-232C SIGNAL TRANSMITTER/    |      |

|       | RECEIVER BLOCK                 | 3-9  |

| 3-6.  | REAR KEY FETCH BLOCK           | 3-9  |

| 3-7.  | NONVOLATILE MEMORY BLOCK       | 3-10 |

| 3-8.  | DEFLECTION SYSTEM CONTROL      |      |

|       | BLOCK                          | 3-12 |

| 3-9.  | VIDEO SYSTEM CONTROL BLOCK     | 3-13 |

| 3-10. | POWER SOURCE INTERLOCKING      |      |

|       | MODE                           | 3-15 |

| 3-11. | SYSTEM CONTROL MODES           | 3-16 |

| 3-12. | SYSTEM CONTROL BY RS-232C      |      |

|       | INTERFACE                      | 3-21 |

# **SECTION 4**

.

| VID   | EO CIRCUIT                             | 4-1  |

|-------|----------------------------------------|------|

| 4-1.  | OUTLINE OF VIDEO CIRCUIT               | 4-2  |

| 4-2.  | INPUT SIGNAL SWITCHING CIRCUIT         | 4-3  |

| 4-3.  | CONTROL SIGNAL GENERATOR               |      |

|       | CIRCUIT                                | 4-5  |

| 4-4.  | DIGITAL COMB FILTER                    | 4-7  |

| 4-5.  | CHROMA SYSTEM OF VIDEO                 |      |

|       | CIRCUIT                                | 4-10 |

|       | 4-5-1. Outline of V/C/D IC (TA8845AN)  | 4-10 |

|       | 4-5-2. Video Signal Processing Circuit | 4-13 |

|       | 4-5-3. Color Circuit                   | 4-20 |

| 4-6.  | SHADING CORRECTION CIRCUIT             | 4-26 |

| 4-7.  | DRIVE REGULATING CIRCUIT               | 4-30 |

| 4-8.  | AKB CIRCUIT                            | 4-31 |

| 4-9.  | CRT DRIVE CIRCUIT                      | 4-34 |

| 4-10. | ABL INTERLOCKING CIRCUIT               | 4-36 |

# **SECTION 5**

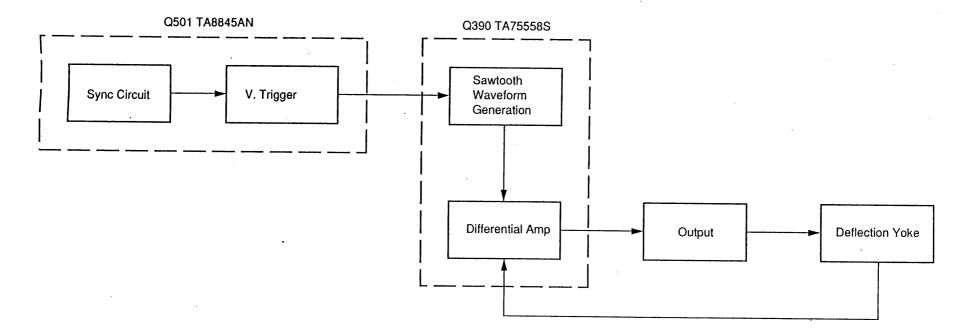

| VE   | RTICAL DEFLECTION CIRCUIT                      | 5-1  |

|------|------------------------------------------------|------|

| 5-1. | OUTLIN OF VERTICAL DEFLECTION                  |      |

|      | CIRCUIT                                        | 5-2  |

|      | 5-1-1. Comparison Between Model CX32C81        | 5-2  |

|      | 5-1-2. Basic Theory of Operation               | 5-3  |

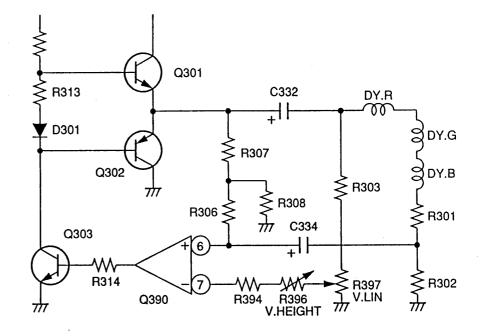

| 5-2. | V DEFLECTION CIRCUIT                           | 5-4  |

|      | 5-2-1. Reference Saw-Tooth Waveform Voltage    |      |

|      | Generation Circuit                             | 5-5  |

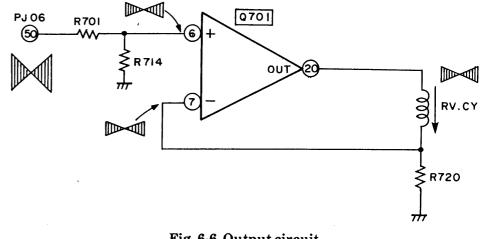

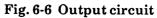

|      | 5-2-2. V Output Circuit                        | 5-6  |

|      | 5-2-3. Linearity Correction and Adjustment     |      |

|      | Circuit                                        | 5-6  |

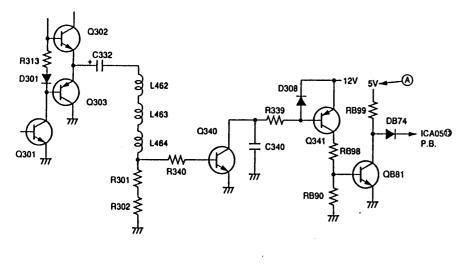

| 5-3. | <b>PROTECTION CIRCUIT FOR V</b>                |      |

|      | DEFLECTION STOP                                | 5-7  |

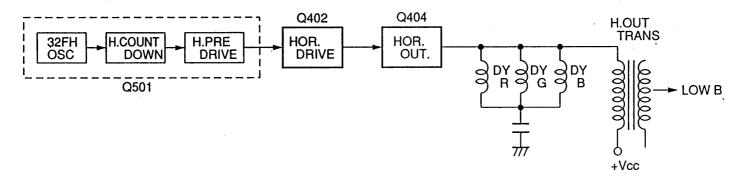

| 5-4. | OUTLINE OF HORIZONTAL                          |      |

|      | DEFLECTION CIRCUIT                             | 5-8  |

| 5-5. | THEORY OF OPERATION (N2DB)                     | 5-9  |

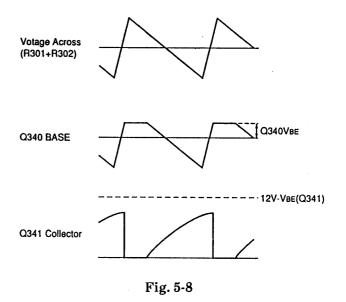

|      | 5-5-1. Horizontal Start Circuit                | 5-9  |

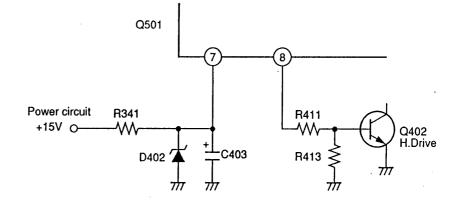

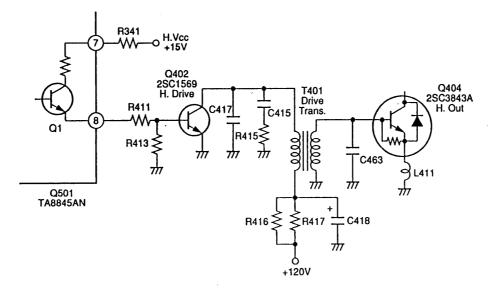

|      | 5-5-2. H Drive Circuit                         | 5-10 |

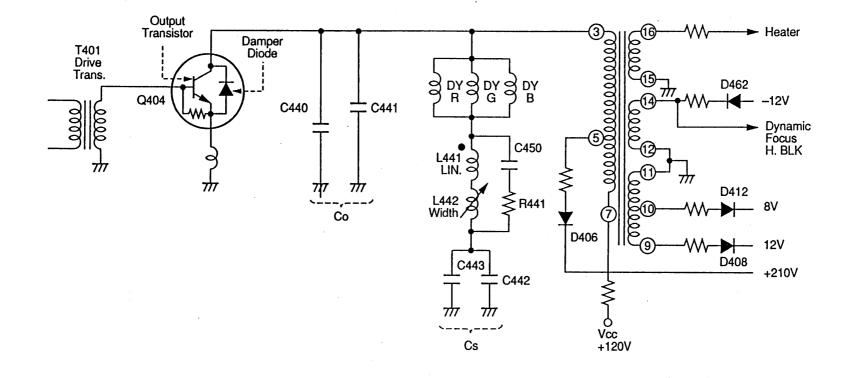

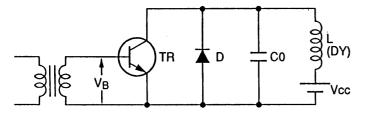

|      | 5-5-3. H Output Circuit                        | 5-11 |

|      | 5-5-4. Protection Circuit for H Output Circuit | 5-18 |

|      |                                                |      |

### **SECTION 6**

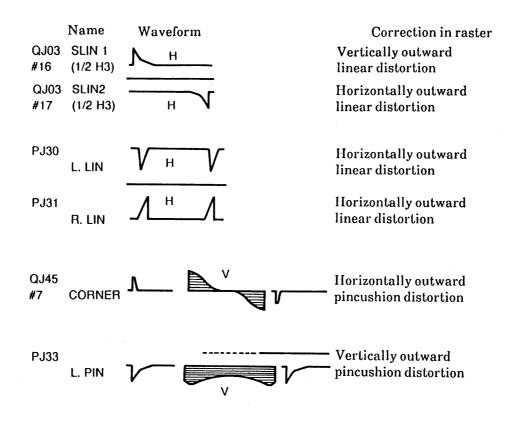

| COI  | <b>NVERGENCE CIRCUIT</b>              | 6-1  |

|------|---------------------------------------|------|

| 6-1. | OUTLINE                               | 6-2  |

| 6-2. | <b>CORRECTION SIGNAL GENERATOR</b>    |      |

|      | CIRCUIT                               | 6-2  |

| 6-3. | GAIN CONTROL CIRCUIT                  | 6-7  |

| 6-4. | COMPOSING CIRCUIT                     | 6-8  |

| 6-5. | <b>CONVERGENCE OUTPUT CIRCUIT</b>     | 6-8  |

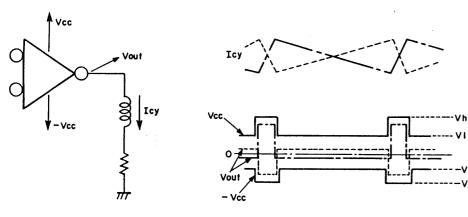

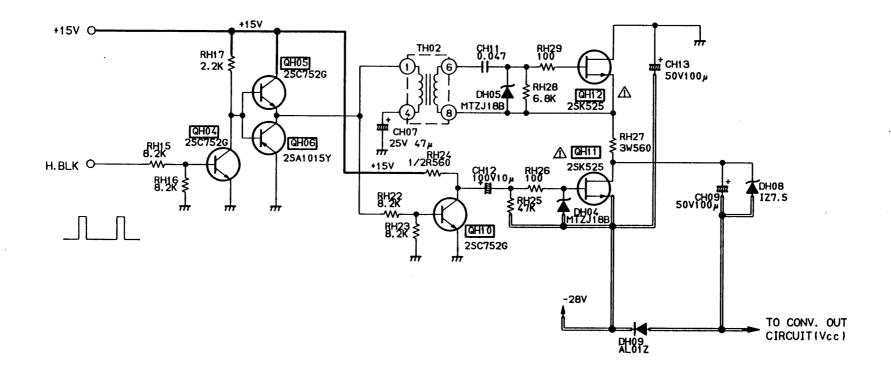

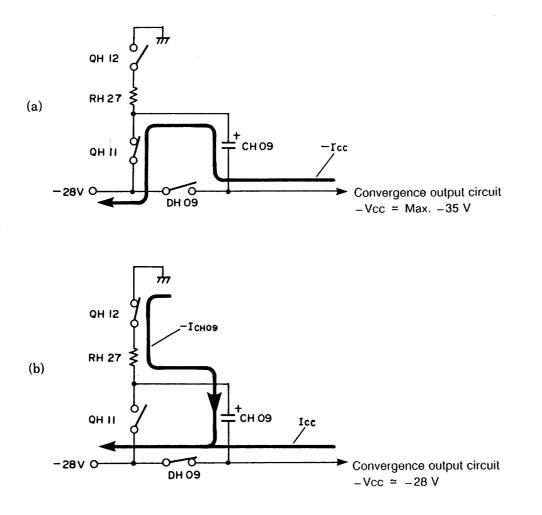

| 6-6. | PUMP-UP CIRCUIT                       | 6-9  |

|      | 6-6-1. Positive Power Pump-up Circuit | 6-9  |

|      | 6-6-2. Negative Power Pump-up Circuit | 6-13 |

## **SECTION 7**

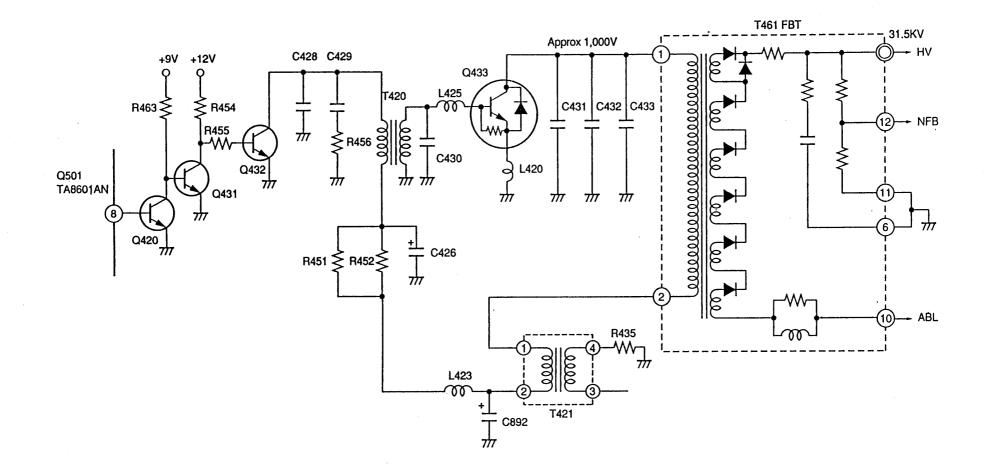

# HIGH VOLTAGE CIRCUIT 7-1 7-1. OUTLINE 7-2

| 7-2. | HIGH VOLTAGE GENERATION     |     |

|------|-----------------------------|-----|

|      | CIRCUIT                     | 7-2 |

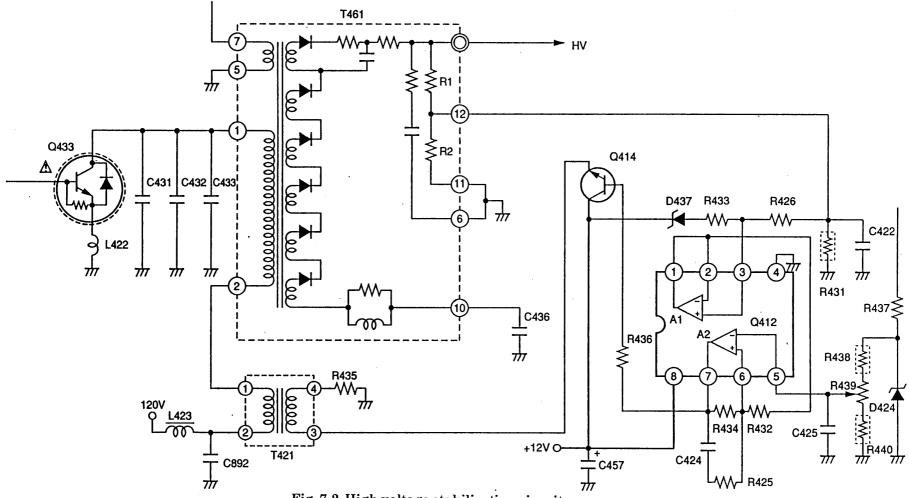

| 7-3. | HIGH VOLTAGES STABILIZATION |     |

|      | CIRCUIT                     | 7-4 |

|      | 7-3-1. Circuit Operation    | 7-5 |

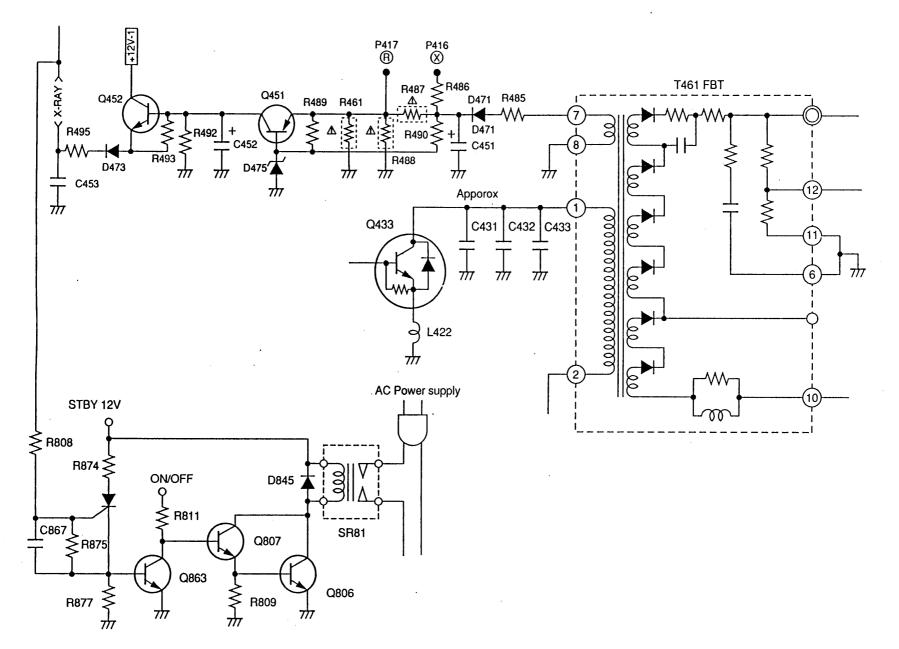

| 7-4. | X RAY PROTECTION CIRCUIT    | 7-6 |

#

| 8-1. | OUTLINE                    | 8-2 |

|------|----------------------------|-----|

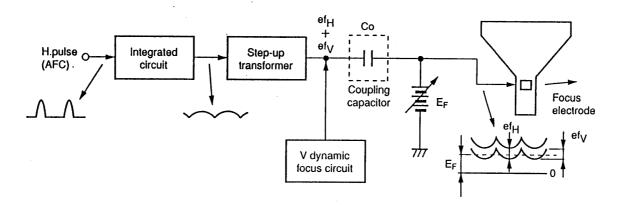

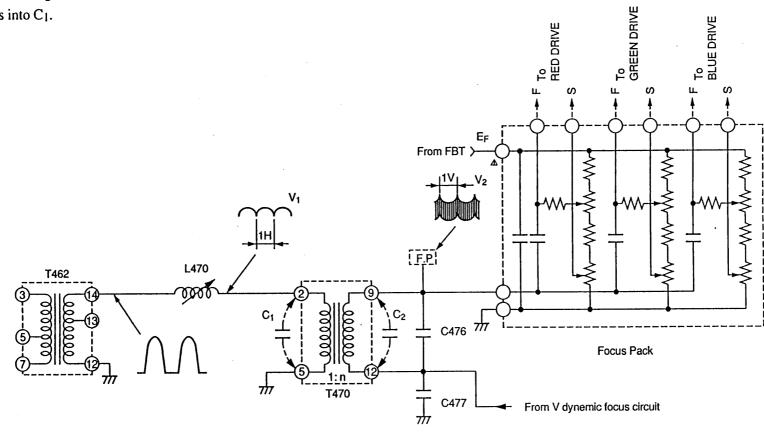

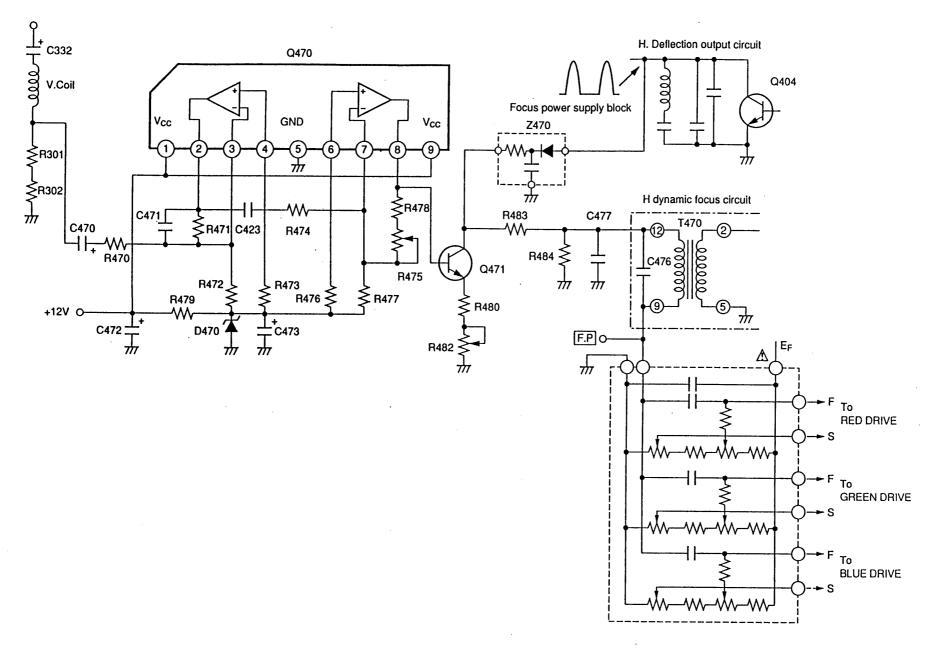

| 8-2. | H DYNAMIC FOCUS CIRCUIT    | 8-2 |

|      | 8-2-1. Theory of Operation | 8-2 |

|      | 8-2-2. Circuit Operation   | 8-3 |

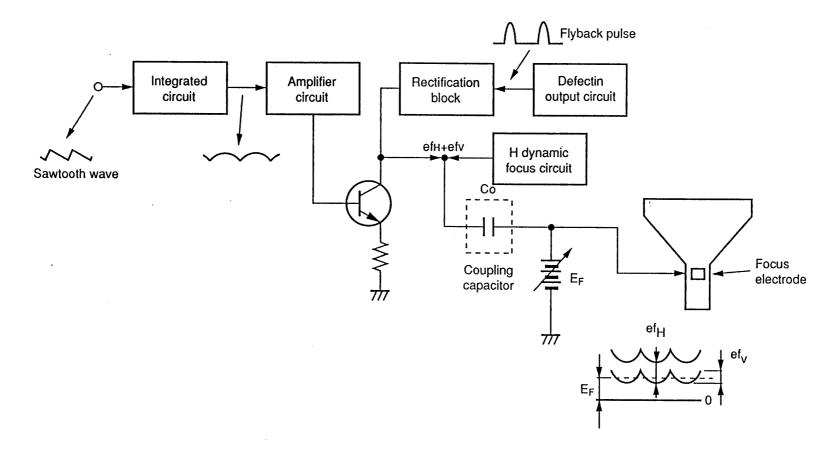

| 8-3. | V DYNAMIC FOCUS CIRCUIT    | 8-4 |

|      | 8-3-1. Theory of Operation | 8-4 |

|      | 8-3-2. Circuit Operation   | 8-5 |

# **SECTION 9**

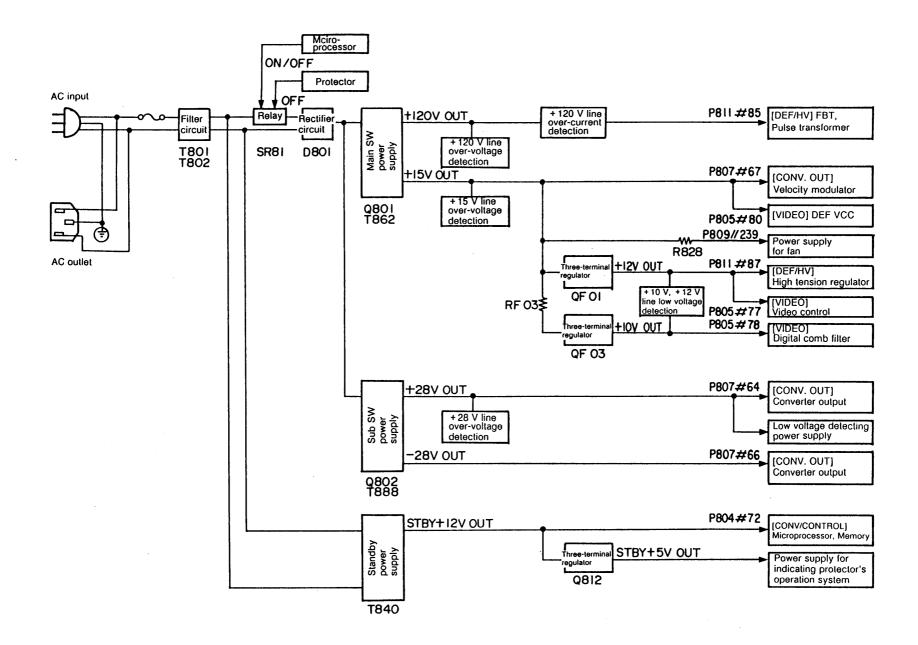

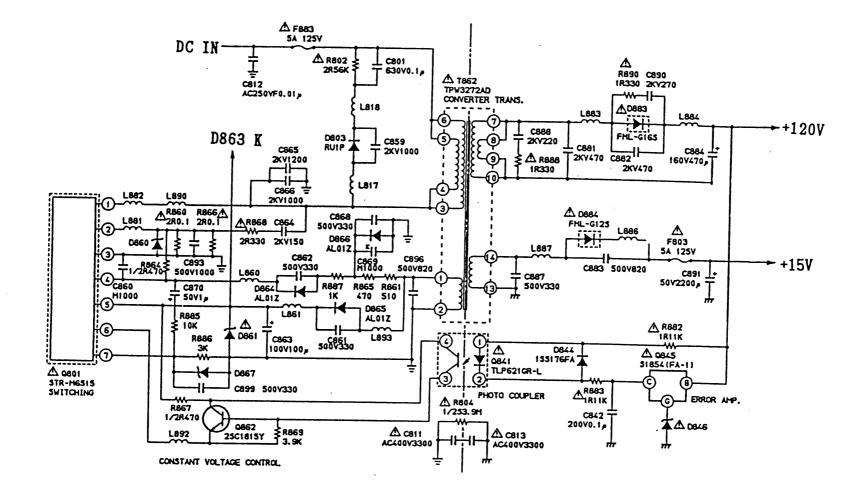

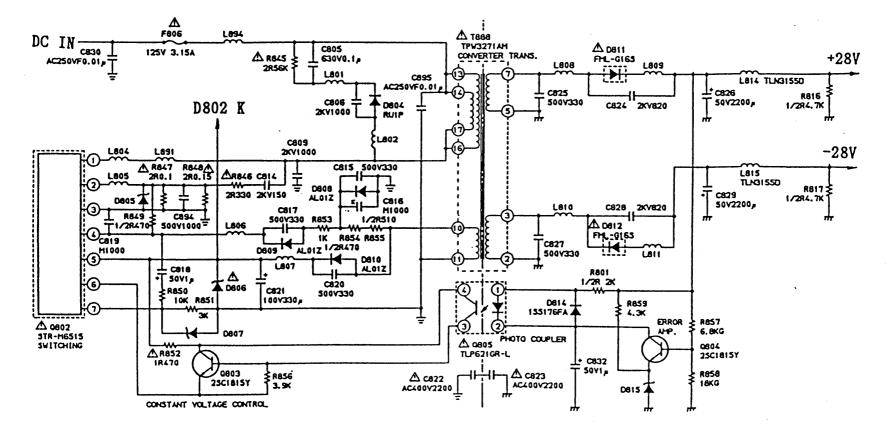

| POV  | VERS   | SUPPLY CIRCUIT                                         | 9-1  |

|------|--------|--------------------------------------------------------|------|

| 9-1. | OUT    | LINE                                                   | 9-2  |

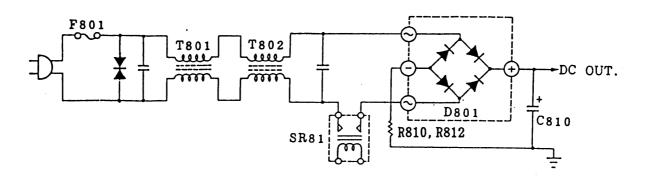

| 9-2. | REC'   | TIFIER CIRCUIT                                         | 9-4  |

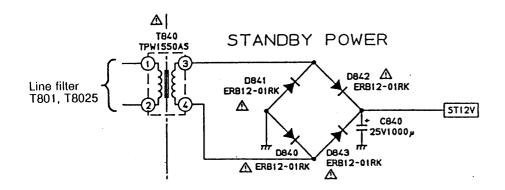

| 9-3. | STAN   | NDBY POWER SUPPLY CIRCUIT                              | 9-5  |

| 9-4. | MAI    | N POWER SUPPLY CIRCUIT                                 | 9-5  |

| 9-5. | SUB    | POWER SUPPLY CIRCUIT                                   | 9-7  |

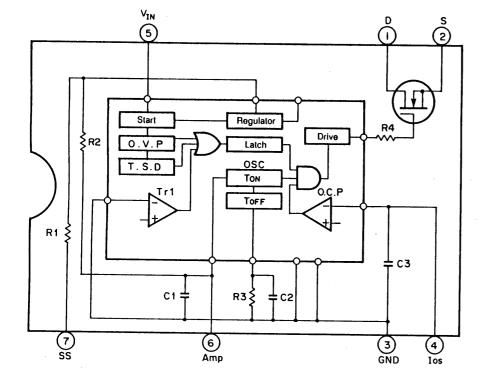

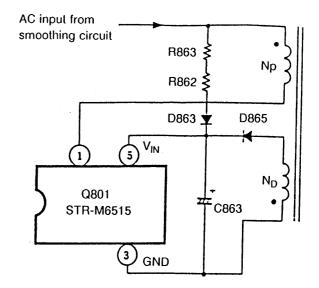

| 9-6. | OPE    | RATION OF VOLTAGE CONTROL                              |      |

|      | IC Q8  | 801 (STR-M6515)                                        | 9-9  |

|      | 9-6-1. | Operation of STR-M6515 Terminals and Its               |      |

|      |        | Peripheral Circuits                                    | 9-10 |

|      | 9-6-2. | Amp Terminal (pin 6), Oscillator,                      |      |

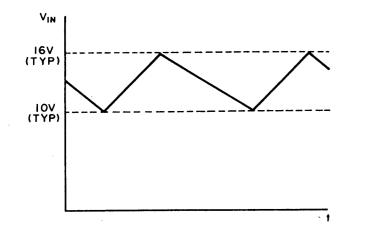

|      |        | Constant-voltage Control Circuit                       | 9-11 |

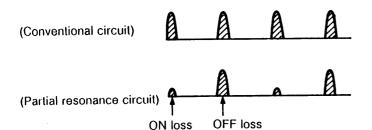

|      | 9-6-3. | Partial Resonance Circuit                              | 9-13 |

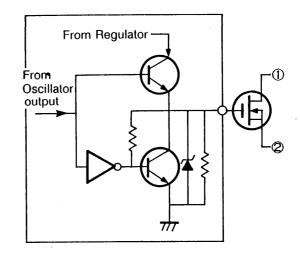

|      | 9-6-4. | Drive Circuit                                          | 9-14 |

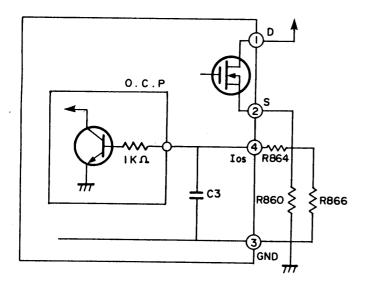

|      | 9-6-5. | I <sub>OS</sub> terminal (pin 4), O.C.P. (Over Current |      |

|      |        | Protection) Circuit                                    | 9-15 |

|      | 9-6-6. | Latch Circuit                                          | 9-15 |

|      | 9-6-7. | Overheat Protection Circuit                            | 9-16 |

|      | 9-6-8. | Over-voltage Protection Circuit                        | 9-16 |

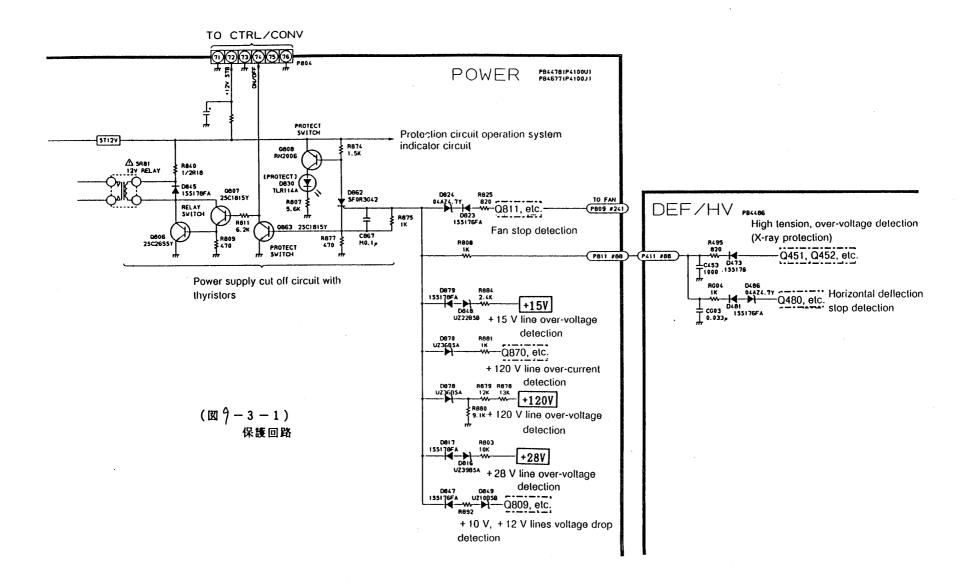

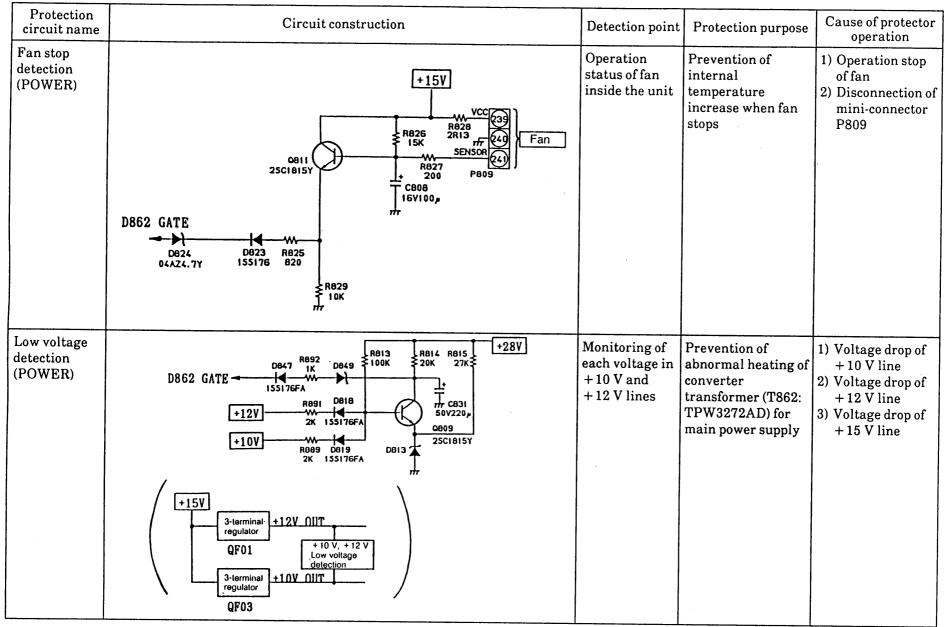

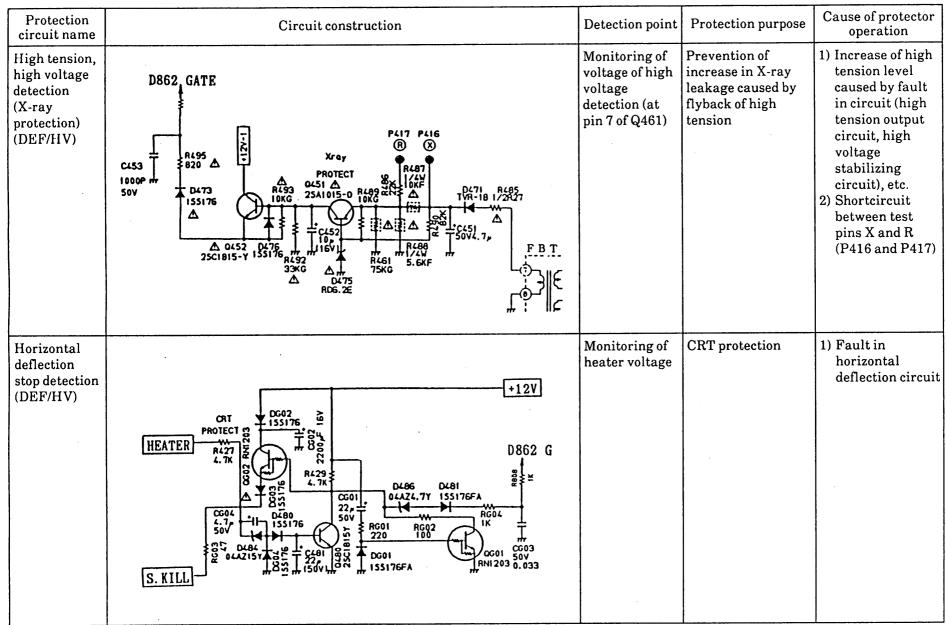

| 9-7. | PRO    | TECTION CIRCUITS                                       | 9-17 |

#

# SECTION 1. INTRODUCTION

--

### **1-1. DESCRIPTION**

rear

P4100U is 41" video wall projection unit. The p4100U consists of two pieces main constructions so called "front box" and "light box". It can be made small when not in used. So, it is easy to transfer, store, install or maintenanced. So it can be repaired easily. The alignment can be implemented both computer and remote hand set. (Available in option)

This service text explains operations of main circuits of the P4100U.

# **1-2. FEATURES**

#### Mechanism

| Item                           | Features                                                                                                                                                                              |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Screen Edge                    | <ul> <li>2.5mm</li> <li>merit –</li> <li>less obvious than the other when<br/>enlarged picture</li> </ul>                                                                             |

| Cabinet Structure              | <ul> <li>Separate type (2 parts)</li> <li>merit -</li> <li>Several assemble methods</li> <li>Easy replaceable electronics</li> <li>Easy access electronics while servicing</li> </ul> |

| Compact Size<br>Transportation | <ul> <li>Slide-in electronics</li> <li>merit -         <ul> <li>less foot-print for warehousing and transportation</li> </ul> </li> </ul>                                             |

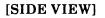

| Depth                          | <ul> <li>1,110mm (43.7")</li> <li>merit -</li> <li>less projecting cubes from wall</li> </ul>                                                                                         |

| Lifting Method                 | • Versatile Handles in more locations                                                                                                                                                 |

#### Optical

| Item              | Features                                                                                                                        |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Screen Technology | <ul> <li>Improved Vertical view angle by<br/>additional lenticular</li> <li>merit –</li> <li>Wider observation angle</li> </ul> |

|                   | <ul> <li>Non linear distribution of diffuser</li> <li>merit -</li> <li>Improved vertical/horizontal color shift</li> </ul>      |

#### Electronics

| Item               | Features                                                                                                                                                               |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Adjustment         | <ul> <li>Remote Control (15m Cable detachable)</li> <li>merit –</li> <li>possible to adjust at view point</li> <li>even after wall setup adjustment is easy</li> </ul> |

| RS-232C Adjustment | <ul> <li>All remote control functions are equipped</li> <li>merit -</li> <li>PC can control all adjustments</li> </ul>                                                 |

| Test Pattern       | <ul> <li>Single cross and cross hatch</li> <li>merit -</li> <li>Both static and dynamic convergences<br/>adjustment possible</li> </ul>                                |

### 1-3. LIST OF UNITS

|   | Unit<br>name | Circuit<br>name  | Unit<br>construction       | Name of<br>module   | Size (mm) |

|---|--------------|------------------|----------------------------|---------------------|-----------|

| 1 | PB4478       | POWER            |                            | TLC137TR/<br>R8700S | 330×249   |

| 2 | PB4486       | DEF              |                            | TLC137TR/<br>R8700S | 330×249   |

| 3 | PB4487       | CONV<br>OUT      | Two boards<br>of the same  | TLC134              | 330×249   |

| 4 | PB4492       | VIDEO            |                            | TLC134              | 330×249   |

| 5 | PB4493       | CONTROL/<br>CONV |                            | TLC134              | 330×249   |

| 6 | PB4494       | CPT-D/<br>COMB   | Four differ-<br>ent boards | TLC134              | 249×249   |

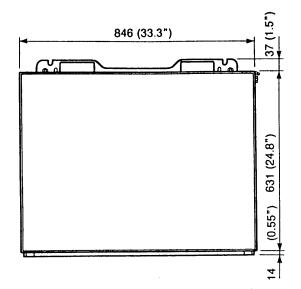

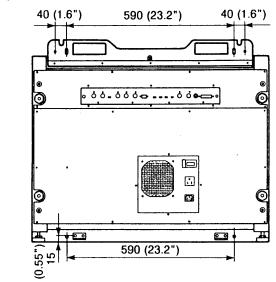

## **1-4. NAME AND DIMENSIONS**

[FRONT]

[REAR]

# **1-5. SPECIFICATIONS**

| Ту  | ре                           | 41" Projection Unit                                          |                                                                                                                                                                                       |  |  |  |  |  |

|-----|------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ΤV  | System                       | NTSC                                                         |                                                                                                                                                                                       |  |  |  |  |  |

| Pro | ojection tube                | $7$ " CRT $\times$ 3                                         |                                                                                                                                                                                       |  |  |  |  |  |

| Re  | solution                     | 800 line or more (Horizontal)<br>350 line or more (Vertical) |                                                                                                                                                                                       |  |  |  |  |  |

| Us  | able field of view           | 150° (Horizontal),                                           | 60° (Vertical)                                                                                                                                                                        |  |  |  |  |  |

| Us  | able temperature             | 5~35°C (41~95°F                                              | )                                                                                                                                                                                     |  |  |  |  |  |

| Inp | outsignals                   |                                                              |                                                                                                                                                                                       |  |  |  |  |  |

|     | Video input                  | Input terminal<br>Input level                                | BNC connector $	imes$ 1<br>1V(p-p) (75 $\Omega$ ) Standard level                                                                                                                      |  |  |  |  |  |

|     | Video output                 | Output terminal                                              | BNC connector $\times 1$                                                                                                                                                              |  |  |  |  |  |

|     | Y/C separate<br>input        | Input terminal<br>Input level                                | Luminance (Y):<br>BNC connector $\times 1$<br>Chromainance (C):<br>BNC connector $\times 1$<br>Luminance (Y):<br>$1V(p-p) (75\Omega)$<br>Chrominance (C):<br>$0.286V(p-p) (75\Omega)$ |  |  |  |  |  |

|     | Ext. control<br>signal input | Input terminal<br>Signal input                               | BNC connector $\times$ 1<br>Open: Video input<br>Short circuit:<br>Y/C separate input                                                                                                 |  |  |  |  |  |

|     | RGB input                    | Input terminal<br>Input level                                | D SUB 9-pin (male) connector<br>$\times$ 1<br>R, G, B signal:<br>0.7V(p-p) (75 $\Omega$ )<br>Sync signal:<br>0.3V(p-p) (75 $\Omega$ )                                                 |  |  |  |  |  |

|     | Remote control<br>input      | Input terminal<br>Signal input                               | $\phi$ 3.5mm terminal<br>Remote signal, +3V, GND                                                                                                                                      |  |  |  |  |  |

|                                | RS-232C port         | Input terminal<br>Speed<br>Mode                                                              | D SUB 25-pin (female)<br>connector × 1<br>1,200, 2,400, 4,800, 9,600 baud<br>No parity, 8 bit, 1 stop bit |  |  |  |

|--------------------------------|----------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| Co                             | mbination I/O        | Input terminal                                                                               | DIN 5-pin connector $	imes 2$                                                                             |  |  |  |

| 1                              | hite balance<br>itch | 2 mode selectable                                                                            |                                                                                                           |  |  |  |

| Electrical<br>requirement      |                      | AC 120V, 60Hz                                                                                |                                                                                                           |  |  |  |

| Po                             | wer consumption      | 260W (370VA)                                                                                 |                                                                                                           |  |  |  |

| Di                             | mensions             | 846(W) × 682(H) × 1110(D) mm<br>(33.3"(W)×26.9"(H)×43.7"(D))<br>(excluding protruding parts) |                                                                                                           |  |  |  |

| Weight         85kg (187 lbs.) |                      |                                                                                              |                                                                                                           |  |  |  |

| Ac                             | cessories            | Control cable (DIN 5-pin connector)<br>Power cable                                           |                                                                                                           |  |  |  |

\* A control cable is supplied for controlling video will projection unit being used toghther.

\* The specifications and design of this product are subject to change without notice due to improvement.

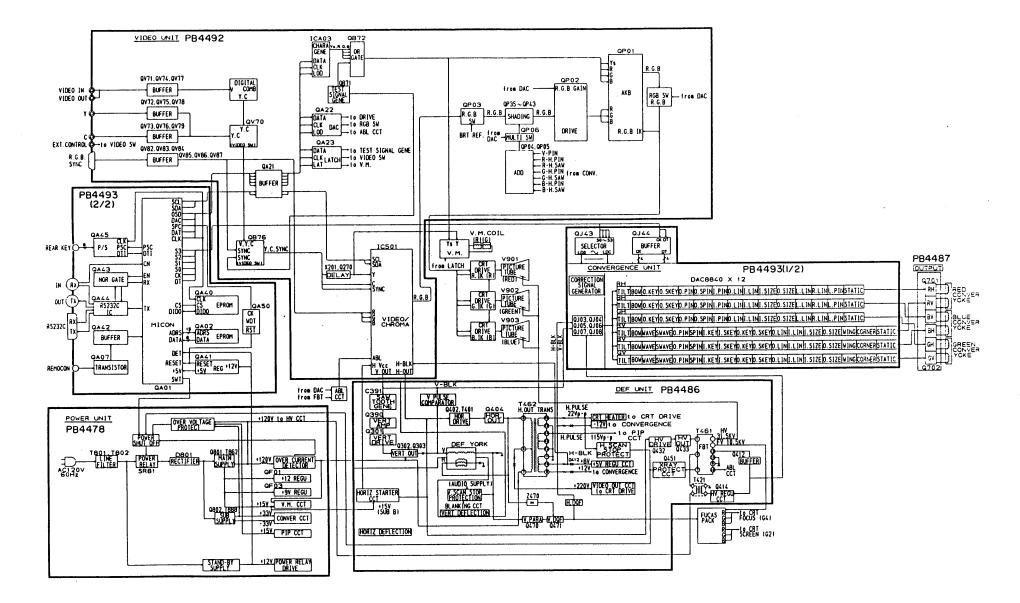

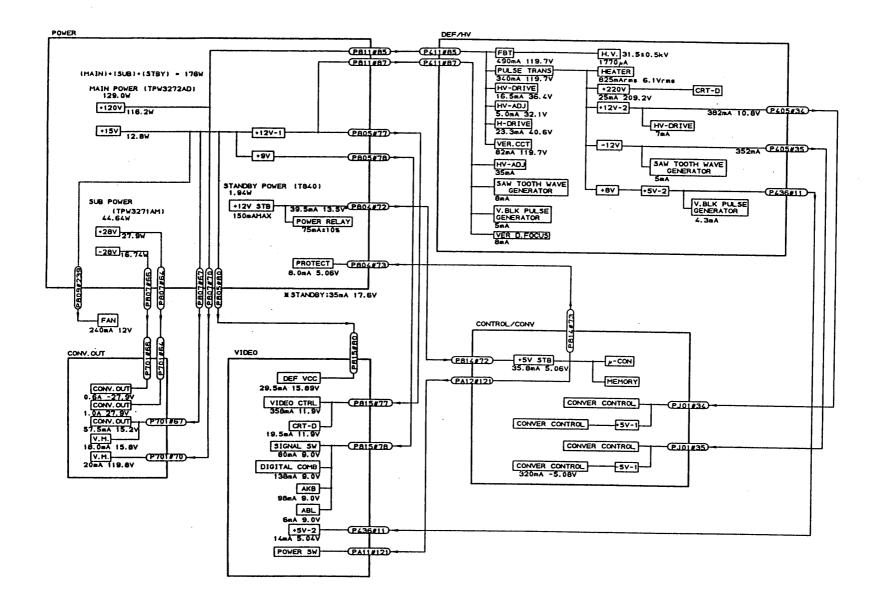

#### **1-6. BLOCK DIAGRAM**

1-7. PARTS ARRANGEMENT

۰.

# SECTION 2. OPTICAL SYSTEM

#### **2-1. NECK CONSTRUCTION**

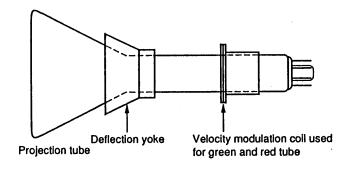

#### 2-1-1. Main Components of Neck of Projection Tube

#### 2-1-2. Theory of Operation

As component parts of the neck of the projection tube, there are (1) deflection yoke (consisting of main yoke, sub-yoke, centering magnet) and (2) velocity modulation coil provided.

The main yoke of the deflectin yoke is composed of horizontal and vertical deflection yokes that turn light beam horizontally and vertically respectively.

The sub-yoke is called the convergence yoke, which is composed of horizontal and vertical coils. The sub-yoke functions to adjust distortion and coloring of picture with regulating current supplied from the convergence output circuit.

The centering magnet that is composed of bipolar magnets and installed behind the deflection yoke functions to adjust picture position in the screen. The velocity modulation coil functions to make the picture clear by modulating deflection velocity.

#### 2-1-3. Projection Tube

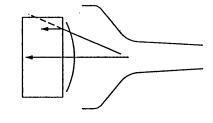

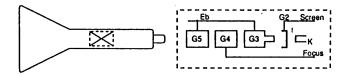

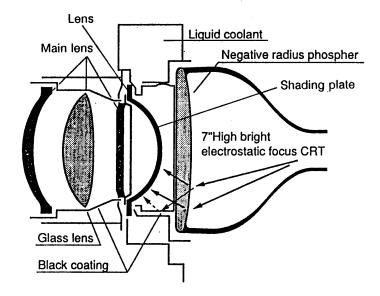

The flourescent screen is concavely curved with a radius of 350 mm. This concave gathers light beams in edge portions in the direction of the optical axis for efficient use of the quantity of light of the projection tube.

Electrostatic focus

Parabolic waveform voltage applied to the FOCUS terminal in the horizontal and vertical periods gets the picture to be in focus uniformly in the center and edge portions of the screen.

The velocity modulation circuit is additionally installed to make the picture clearer.

#### 2-2. FUNCTIONS OF MAIN COMPONENTS

#### 2-2-1. Outline

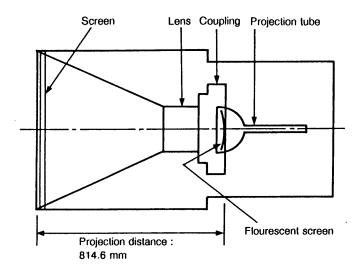

The optical system of the P4100U(J) is mainly composed of the screen, the lens and the projection tube.

The distance between the flourescent screen of the projection tube and the screen is 814.6 mm.

#### 2-2-2. Theory of Operation

Fig. 2-2

#### 2-3. SCREEN

#### 2-3-1. Effect of Flesnel Sheet

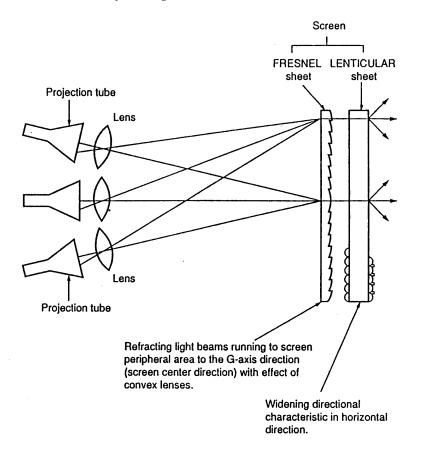

Concaves and convexes that are concentrically arranged on the audience side of the Flesnel sheet have the same effect as convex lenses, and the uneven surface turns refracted rays nearly in parallel with the normal illumination direction to the screen even not only for the center part of the screen but also for the edge portions. This effect results from the focal length of the Flesnel lens so that it is designed to fucus on the emission pupil of the lens.

Moreover, the other side of the Flesnel sheet toward the projection lens has horizontally parallel fine unnevenness called the vertical lenticule, which has an effect on vertical expansion of light beam.

FRESNEL sheet Frojection Lens tube V. lenticular side Flesnel lens Without FRESNEL sheet

Fig. 2-3

In a video projection system that employs one Flesnel sheet, rays in the edge portions of the screen are generally refracted in the direction of the optical axis. However, this projection system refracts rays to be parallel with the optical axis to remove luminance difference from the neighboring screens for other sets since this system uses multiple Flesnel sheets.

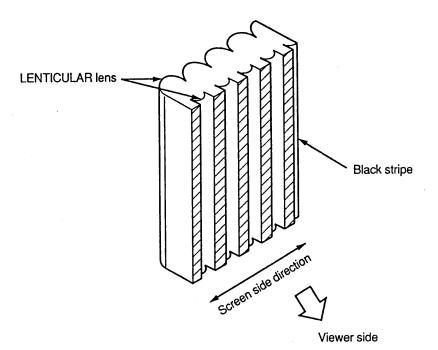

#### 2-3-2. Outward Appearance of Lenticular Sheet

Fig. 2-4

Fig. 2-5

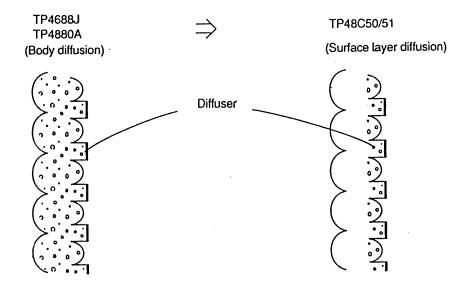

Light beams are gathered in diffusers on the layer surface for efficient illumination, and the luminance is consequently raised by 10% approximately.

The P4100U(J) employs the lenticular sheet for surface diffusion.

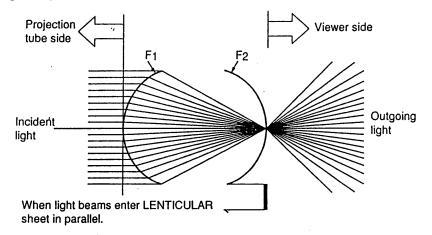

#### 2-3-3. Effect of Lenticular Sheet

The lenticular sheet is effective to diffuse rays that are obliquely applied to the screen similarly to rays irradiated to the screen at a right angle when the screen is viewed from the front.

#### 2-4. EFFECT OF OPTICAL COUPLING

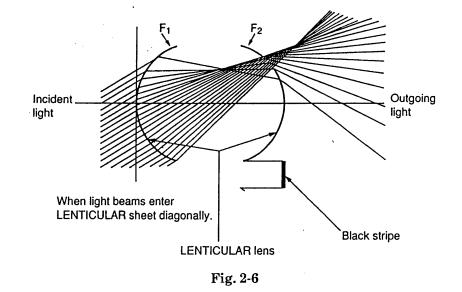

If something (liquid) having a refractive index similar to that of glass fills between the projection tube and the lens, it reduces reflection of rays in the boundary and accordingly improves contrast and loss in quantity of light.

Moreover, such a liquid not only raises the power of the projection tube by its cooling effect but also prevents the surfaces of the projection tube and the lens from getting dust.

Fig. 2-7

#### 2-5. LENS

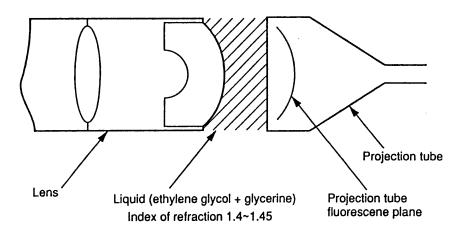

The optical system that are mainly composed of the main lens, concave lens, concave fluorescent screen and projection tube realizes the lens system of a short focal length.

Thanks to the short focal length of the the lens system, the projection unit can be designed remarkably thin and compact.

Fig. 2-8

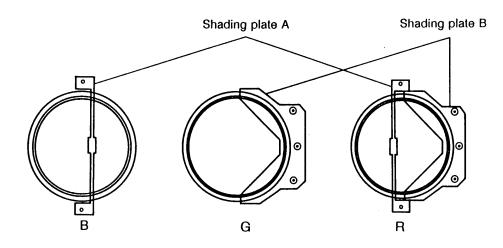

#### 2-5-1. Shading Plate

# Fig. 2-9 C lens and coupling block as viewed from the screen side (Main lenses are removed.)

Two kinds of shading plates (four shading plates in total) are inserted between the C lens (coupling) and the main lens for preventing picture from irregular coloring. Each shading plate is concaved 2 to 5 mm to the C lens side.

Don't remove any setscrew retaining the shading plate, otherwise coupling liquid leaks out.

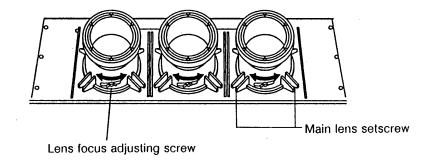

#### 2-5-2. Focus Adjustment

Focalization of the lens system can be adjusted according to the following procedure.

Loosen the setscrew and turn the lens slowly clockwise and counterclockwise to get the lens to come into the best focus on the screen. After this adjustment, tighten the setscrew to secure the lens not to go out of focus.

## 2-6. PRECAUTIONS ON REPLACEMENT OF LENS AND PROJECTION TUBE

When dismounting the main lens, only remove four setscrews (a main lens) retaining it. If any other screw is removed, coupling liquid will leak out.

When mounting the main lens again, loosen the focus adjusting screw and turn the main lens fully counterclockwise as viewed from the screen side beforehand.

The projection tube to be supplied as a service part is an assembly incorporating the C lens and coupling with coupling liquid sealed inside.

Fig. 2-10

# SECTION 3. MICROPROCESSOR

## **3-1. OUTLINE OF SYSTEM**

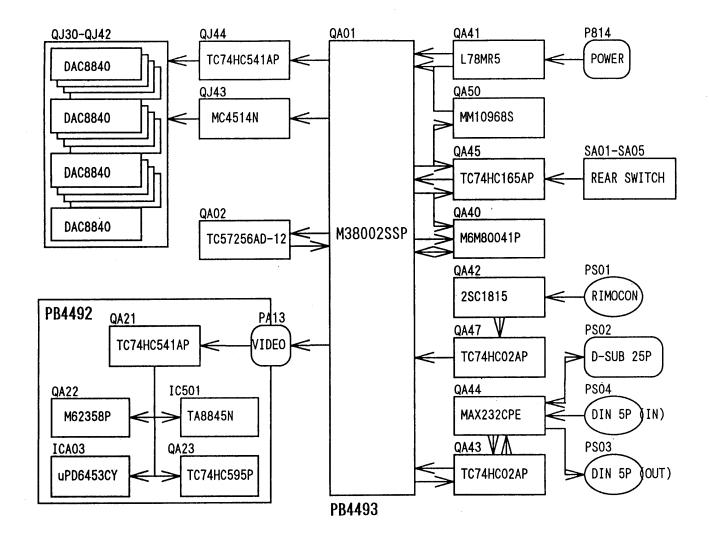

The system microprocessor of the video wall projection unit (P4100U) is entirely newly designed under the developing concept of an easy maintenance program such as employment of external program ROM, structured notation, parts modularity, multi-filing system, and so on.

Main functions of the system microprocessor are processing of received remote control data, processing of transmission and reception of RS-232C data, processing of control inputs such as input data of key switches, processing of control outputs such as deflection system control output, video system control output, system control output, etc. besides processing of status holding by readout and write-in various regulating data from/to the nonvolatile memory. The features of the system microprocessor are remarkable improvement in the precision and drastic time saving in adjustment as a result that the deflection control system can be adjusted by the external method (remote control) with the S/P controlled DAC replacing the conventional internal adjustment method (manual) with variable resistors.

For the P4100U, those adjustments can be performed with external control signals of the RS-232C standard, moreover, respective units can be controlled and adjusted individually or together even when they are connected in a multi-unit system.

Fig. 3-1-1 System block diagram

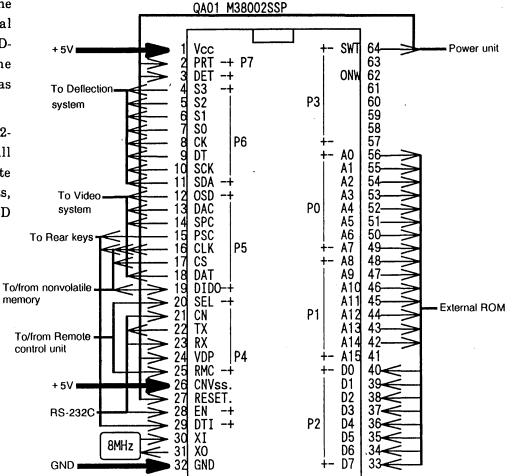

#### **3-2. SYSTEM MICROPROCESSOR**

A Mitsubishi's 8-bit microcontroller (M38002SSP) is employed as the system microprocessor, QA01, which does not use the internal programming area but uses QA02 (Toshiba's EPROM, TC57256AD-12) as an external program ROM. As a result, change of the specifications of the system microprocessor and maintenance such as repair of bug are very easy.

As shown in Fig. 3-2-1 'Pin assignment of microprocessor' and Fig. 3-2-2 'Table of pin functions', the system microprocessor manages all inputs and outputs of control signals such as processings of remote control inputs, RS-232C inputs, adjustment data inputs and outputs, deflection system control signals, video system control signals, OSD display control signals, etc.

Fig. 3-2-1 Pin assignment of system microprocessor

| Pin<br>No. | Pin<br>Name | Function Input/<br>Output Logic/Detail |        | Remark                    |                     |

|------------|-------------|----------------------------------------|--------|---------------------------|---------------------|

| 1          | Vcc         | Power supply                           | Input  | +5V                       |                     |

| 2          | PRT         | Protect monitor<br>input               | Input  | Detection at low<br>level | Not con-<br>nected  |

| 3          | DET         | Low voltage<br>detection input         | Input  | Detection at low<br>level |                     |

| 4          | S3          | DAC8840<br>selection 3                 | Output | For deflection<br>system  |                     |

| 5          | S2          | DAC8840<br>selection 2                 | Output | For deflection<br>system  |                     |

| 6          | S1          | DAC8840<br>selection 1                 | Output | For deflection<br>system  |                     |

| 7          | SO          | DAC8840<br>selection 0                 | Output | For deflection<br>system  |                     |

| 8          | СК          | Clock for<br>DAC8840                   | Output | For deflection<br>system  |                     |

| 9          | DT          | Data for DAC8840                       | Output | For deflection<br>system  |                     |

| 10         | SCK         | I2C clock for<br>TA8845N               | Output | For video<br>adjustment   | To video<br>circuit |

| 11         | SDA         | I2C data for<br>TA8845N                | Output | For video<br>adjustment   | To video<br>circuit |

| 12         | OSD         | uPD6453CY load                         | Output | For OSD                   | To video<br>circuit |

| 13         | DAC         | M62358P load                           | Output | For video<br>adjustment   | To video<br>circuit |

| 14         | SPC         | TC74HC595AP<br>latch                   | Output | For video<br>adjustment   | To video<br>circuit |

| 15         | PSC         | TC74HC165AP<br>load                    | Output | For fetch of rear key     |                     |

| 16         | CLK         | Common clock for devices               | Output | Common clock              | To video<br>circuit |

| Pin<br>No. | Pin<br>Name | Function                                    | Input/<br>Output | Logic/Detail                              | Remark              |

|------------|-------------|---------------------------------------------|------------------|-------------------------------------------|---------------------|

| 17         | CS          | M6M80041P chip selection                    | Output           | For nonvolatile<br>memory                 |                     |

| 18         | DAT         | Common data for devices                     | Output           | Common data                               | To video<br>circuit |

| 19         | DIDO        | Data for<br>M6M80041P                       | Input/<br>Output | For nonvolatile<br>memory                 |                     |

| 20         | SEL         | Remote control selection                    | Input            | For check of remote control insertion     | Not con-<br>nected  |

| 21         | CN          | RS-232C<br>combination                      | Input            | For check of system<br>bus connection     |                     |

| 22         | тх          | RS-232C<br>transmission data                | Output           | Data output for RS-<br>232C               |                     |

| 23         | RX          | RS-232C<br>reception data                   | Input            | Data input for RS-<br>232C                |                     |

| 24         | VDP         | VD pulse                                    | Input            | Vertical blanking<br>pulse                | Not con-<br>nected  |

| 25         | RMC         | Reception data<br>from remote<br>controller | Input            | Reception data for<br>remote control      |                     |

| 26         | CNVss       | Operation mode setting                      | Input            | External ROM operation with $+5$ V        |                     |

| 27         | RESET       | External reset                              | Input            | Reset operation at<br>low level           |                     |

| 28         | EN          | RS-232C enable                              | Output           | Enable operation at low level             |                     |

| 29         | DTI         | Data for<br>TC74HC165AP                     | Input            | Data to fetch rear<br>key                 |                     |

| 30         | XI          | Oscillating input                           | Input            |                                           |                     |

| 31         | хо          |                                             | Output           | Generally connected<br>with X'tal (8 MHz) |                     |

| 32         | GND         | Ground                                      | Input            | +0V                                       |                     |

Fig. 3-2-2 Table of pin functions (1/2)

| Pin<br>No. | Pin<br>Name | Function                          | Input/<br>Output | Logic/Detail           | Remark             |

|------------|-------------|-----------------------------------|------------------|------------------------|--------------------|

| 33         | D7          | Data for external<br>ROM (MSB)    | Input            | Program data input     |                    |

| 34         | D6          | Data for external<br>ROM          | Input            | Program data input     |                    |

| 35         | D5          | Data for external<br>ROM          | Input            | Program data input     |                    |

| 36         | D4          | Data for external<br>ROM          | Input            | Program data input     |                    |

| 37         | D3          | Data for external<br>ROM          | Input            | Program data input     |                    |

| 38         | D2          | Data for external<br>ROM          | Input            | Program data input     |                    |

| 39         | D1          | Data for external<br>ROM          | Input            | Program data input     |                    |

| 40         | D0          | Data for external<br>ROM (LSB)    | Input            | Program data input     |                    |

| 41         | A15         | Address for external<br>ROM (MSB) | Output           | Program data<br>output | Not con-<br>nected |

| 42         | A14         | Address for<br>external ROM       | Output           | Program data<br>output |                    |

| 43         | A13         | Address for<br>external ROM       | Output           | Program data<br>output |                    |

| 44         | A12         | Address for<br>external ROM       | Output           | Program data<br>output |                    |

| 45         | D11         | Address for<br>external ROM       | Output           | Program data<br>output |                    |

| 46         | A10         | Address for<br>external ROM       | Output           | Program data<br>output |                    |

| 47         | A9          | Address for<br>external ROM       | Output           | Program data<br>output |                    |

| 48         | A8          | Address for<br>external ROM       | Output           | Program data<br>output |                    |

ŧ.

| Pin<br>No. | Pin<br>Name | Function                          | Input/<br>Output | Logic/Detail            | Remark             |

|------------|-------------|-----------------------------------|------------------|-------------------------|--------------------|

| 49         | A7          | Address for<br>external ROM       | Output           | Program data<br>output  |                    |

| 50         | A6          | Address for<br>external ROM       | Output           | Program data<br>output  |                    |

| 51         | A5          | Address for<br>external ROM       | Output           | Program data<br>output  |                    |

| 52         | A4          | Address for<br>external ROM       | Output           | Program data<br>output  |                    |

| 53         | A3          | Address for<br>external ROM       | Output           | Program data<br>output  |                    |

| 54         | A2          | Address for<br>external ROM       | Output           | Program data<br>output  |                    |

| 55         | A1          | Address for<br>external ROM       | Output           | Program data<br>output  |                    |

| 56         | A0          | Address for external<br>ROM (LSB) | Output           | Program data<br>output  |                    |

| 57         |             | N. C                              | Output           |                         | Not con-<br>nected |

| 58         |             | N. C                              | Output           |                         | Not con-<br>nected |

| 59         |             | N.C                               | Output           |                         | Not con-<br>nected |

| 60         |             | N.C                               | Output           |                         | Not con-<br>nected |

| 61         |             | N. C                              | Output           |                         | Not con-<br>nected |

| 62         | ONW         | External waiting                  | Input            | No waiting with +5<br>V |                    |

| 63         |             | N. C                              | Output           |                         | Not con-<br>nected |

| 64         | SWT         | Power switch                      | Output           | Power on with $+5$ V    |                    |

Fig. 3-2-2 Table of pin functions (2/2)

3-6

#### **3-3. POWER RESET BLOCK**

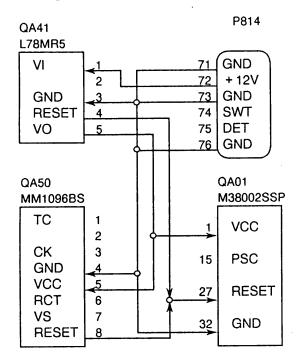

As shown in Fig. 3-3-1 the power reset block employs a three-terminal regulator (L78MR5) with power reset function as the power IC, QA41, and a watchdog timer (MM10968S) as the reset IC, QA50.

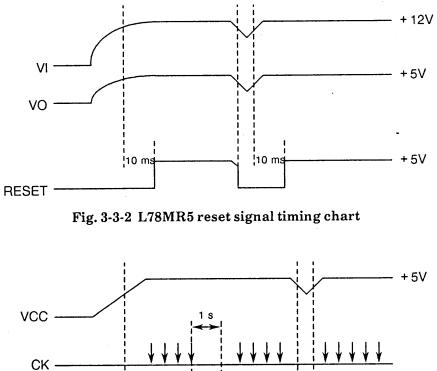

The power IC QA41, which inputs +12 V DC power of standby power supply while outputs +5 V DC power, supplies reset signal to the system microprocessor QA01 on the timing shown in Fig. 3-3-2 "L78MR5 reset signal timing chart" when the power is on.

Fig. 3-3-1 Power reset block

The reset IC QA50 inputs load signal to fetch rear key (to be mentioned later) and, if there is no input of the load signal for about one second, it judges the system microprocessor QA01 is running away and supplies reset signal to the system microprocessor QA01 on the timing shown in Fig. 3-3-3 "MM1096BS reset signal timing chart".

Fig. 3-3-3 MM1096BS reset signal timing chart

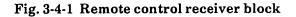

#### 3-4. REMOTE CONTROL RECEIVER BLOCK

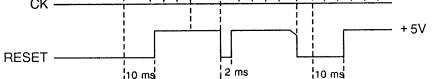

In the remote control receiver block the transistor QA42 (2SC1815) converts remote control signal of 3 V level supplied from the remote control unit (accessory, CT- ) that is connected with the remote terminal as shown in Fig. 3-4-1 into 5 V level signal. This signal is supplied through the noise elimination filter to the buffer QA47 (TC74HC02AP) for shaping waveform, and then supplied to the system microprocessor QA01 on the timing shown in Fig. 3-4-2 "Timing chart of reception signal from remote control unit".

Fig. 3-4-2 Timing chart of reception signal from remote control unit

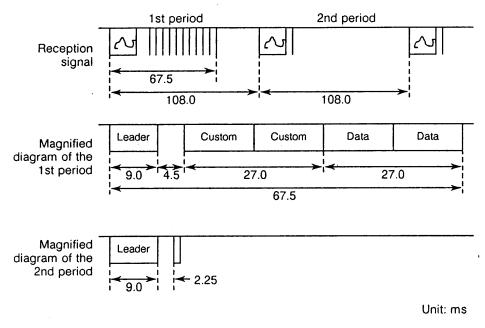

## 3-5. RS-232C SIGNAL TRANSMITTER/ RECEIVER BLOCK

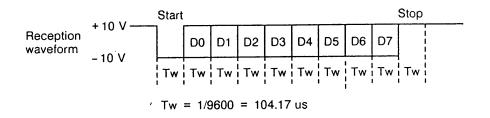

In the RS-232C signal transmitter/receiver block, RS-232C signal that is input through the RS-232C connector (D-SUB 25-pin) PS02 or input through the system bus input connector (DIN 5-pin) PS04 on the timing shown in Fig. 3-5-2 (see Fig. 3-5-1, too) is selected by passing either input signal through QA44 of the DC/DC converter for RS-232C (MAX232CPE) and QA43 of the deta selector (TC74HC02AP), and the selected signal is supplied to the system microprocessor QA01.

This RS-232C signal is controlled by QA01 and then supplied to the system bus output connector PS03 (DIN 5-pin).

For identify management of respective systems, enable signal is controlled to output or not to output RS-232C signal input, in other words, if the signal has the identity number (to be described later), it will be output as it is; or, if it has no identity number, it will not be output.

Fig. 3-5-2 is just an example of communication conditions in which signaling speed is 9600 bps, bit pulse length is 8 bits, and stop bit is 1, without parity bit.

Communication conditions:

9600 bps, 8 bits pulse length, 1 stop bit, without parity

#### 3-6. REAR KEY FETCH BLOCK

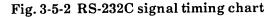

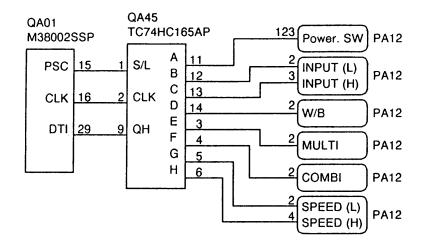

As shown in Fig. 3-6-1 "Rear key fetch block", the P/S of QA45 (TC74HC165AP) of the rear key fetch block holds the operation status of respective rear keys with input data from SA01 to SA05 as well as that of the power switch with input data from PA12 of the video unit. The system microprocessor QA01 fetches those status holding data on the timing shown in Fig. 3-6-2 "TC74HC165AP timing chart". In concrete, data fetch is performed at a certain interval (every 10 ms) in the steady state besides at the initialization by turning on the AC power supply. Therefore, the power can be turned on or off with the power switch instantly (1 sec later in actual operation).

Fig. 3-6-1 Rear key fetch block

Fig. 3-6-2 TC74HC165AP timing chart

#### **3-7. NONVOLATILE MEMORY BLOCK**

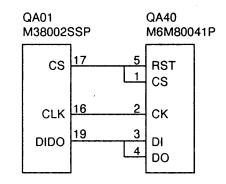

In the nonvolatile memory block employs the nonvolatile memory QA40 (M6M80041P) to store various regulating data as shown in Fig. 3-7-1.

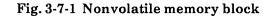

When power is on (AC on), the system microprocessor QA01 reads all regulating data out of the memory on the timing shown in Fig. 3-7-2(A) "Read timing chart" to hold the previously regulated status. When writing regulating data in the memory, the system microprocessor QA01 writes all regulating data on the timing shown in Fig. 3-7-2(B) "Write timing chart" to store all current data for holding the present regulating status.

However, if something faulty (momentary power failure, etc.) occurs in writing regulating data, there is possibility to write data erroneously. To avoid such error in writing data, the initial data stored in the system microprocessor QA01 are read out and written in the memory when any error in data writing is detected.

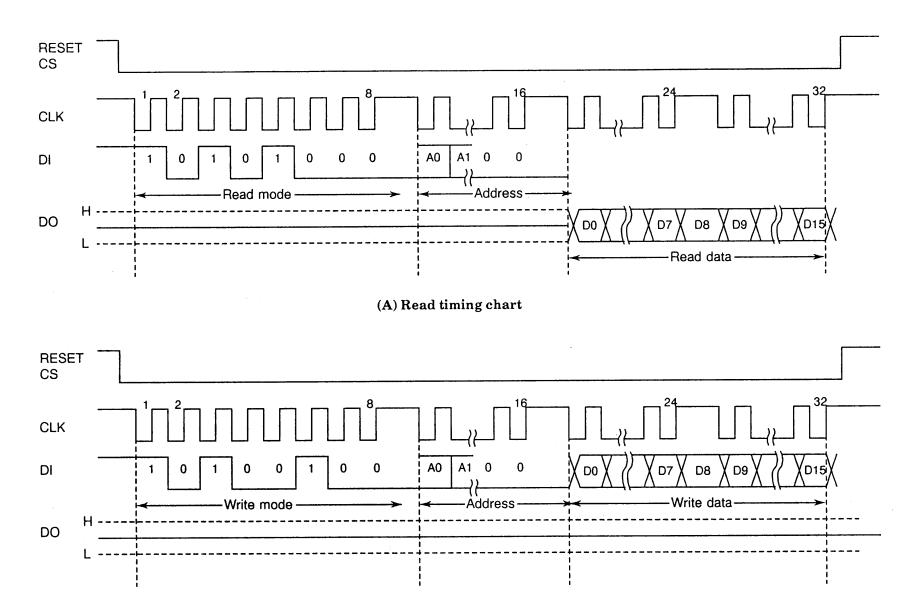

Fig. 3-7-3 illustrates the nonvolatile memory map used for the system microprocessor.

(B) Write timing chart

Fig. 3-7-2 Write/read timing chart of nonvolatile memory

3-12

| Address | LSB<br>0 | 1               | 2           | 3    | 4    | 5  | 6    | 7 | 8                        | 9     | 10                     | 11   | 12   | 13  | 14   | мsв<br>15 |

|---------|----------|-----------------|-------------|------|------|----|------|---|--------------------------|-------|------------------------|------|------|-----|------|-----------|

| 00      |          | Video (TA8845N) |             |      |      |    |      |   |                          |       | Dri                    | ve ( | 1/2) | Cut | off( | (1/2)     |

| 10      | V        | /ide            | o (M        | 623  | 58P  | )  |      |   | ID                       |       |                        |      |      |     |      |           |

| 20      | R        | -H d            | lefle       | ctio | n (D | AC | 3840 | ) | R-V deflection (DAC8840) |       |                        |      |      |     |      |           |

| 30      | B        | -H d            | efle        | ctio | n (D | AC | 3840 | ) | E                        | 3-V ( | V deflection (DAC8840) |      |      |     |      | ))        |

| 40      | G        | -H d            | efle        | ctio | n (D | AC | 3840 | ) | G-V deflection (DAC8840) |       |                        |      |      | ))  |      |           |

| 50      | (D       | Vid             | leo<br>8840 | ))   |      |    |      |   |                          |       |                        |      |      |     |      |           |

| 60      |          |                 |             |      |      |    |      |   |                          |       |                        |      |      |     |      |           |

| 70      |          |                 |             |      |      |    |      |   |                          |       |                        |      |      |     |      |           |

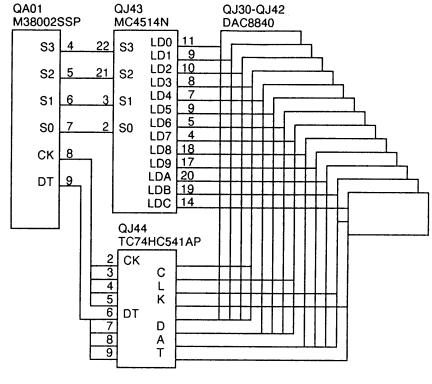

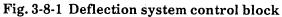

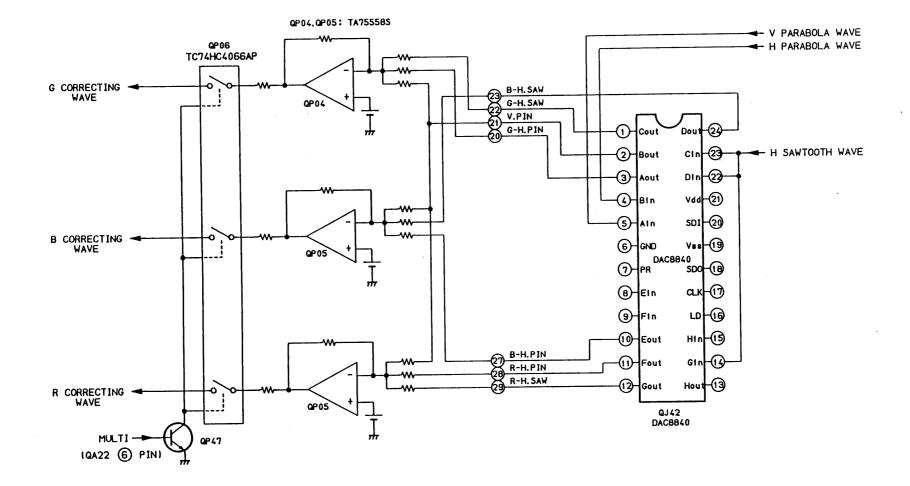

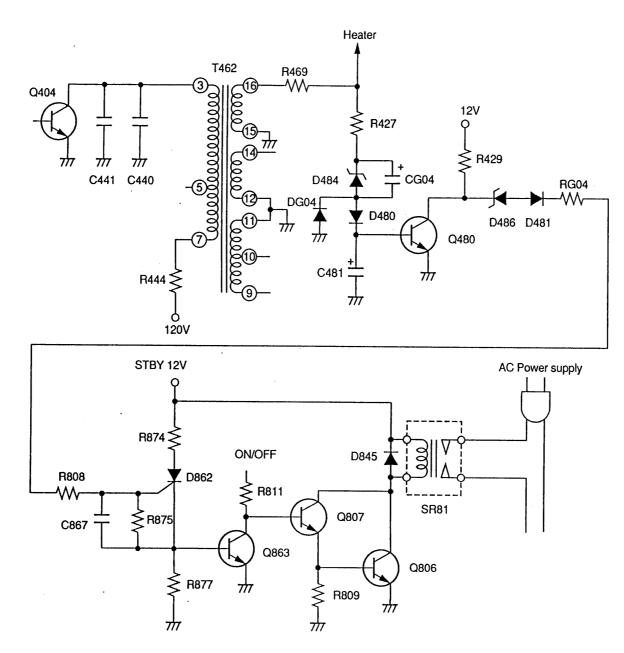

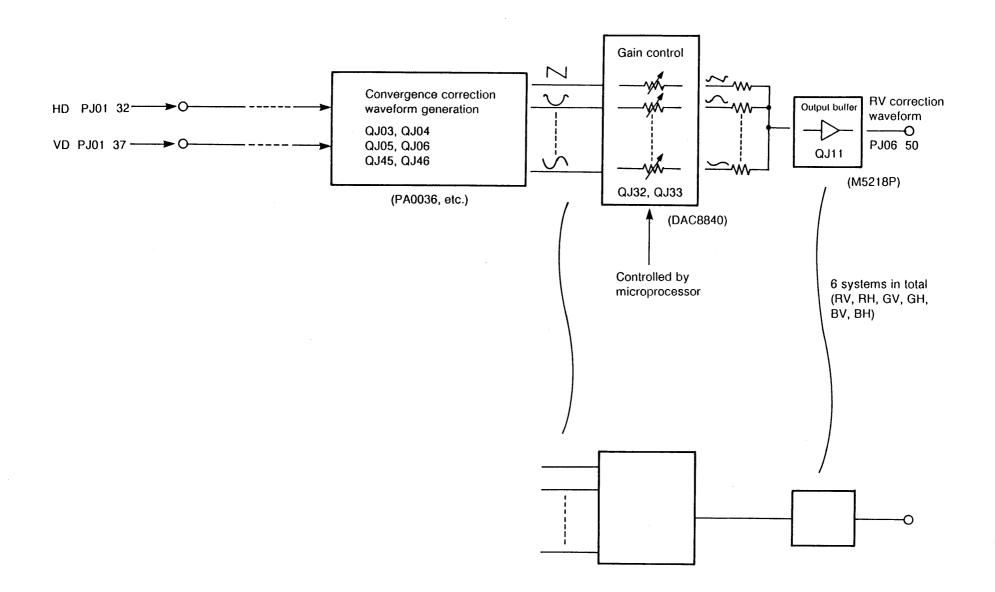

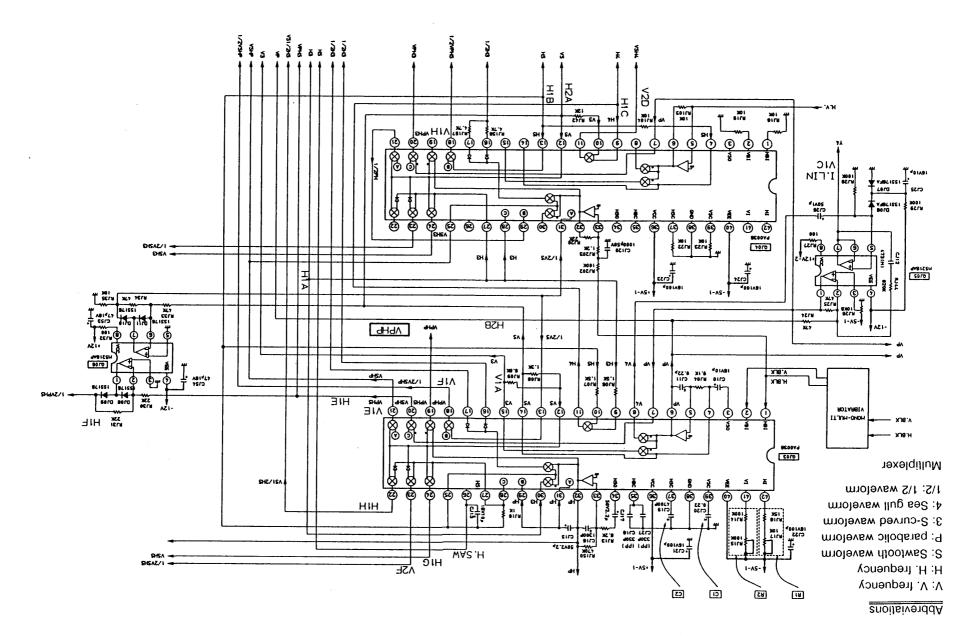

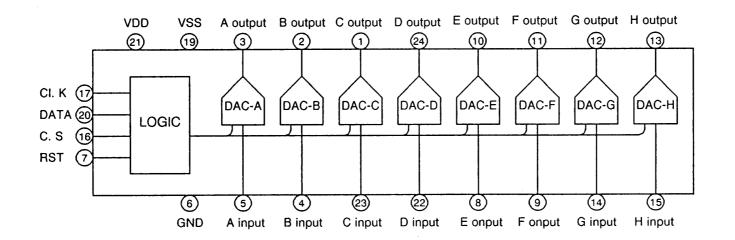

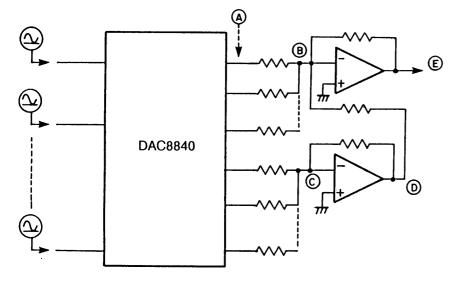

### **3-8. DEFLECTION SYSTEM CONTROL BLOCK**

In the deflection system control block, the line decoder QJ43 (MC4514N) outputs load signals while the buffer QJ44 (TC74HC541AP) outputs clock and data signals to control respective deflection system control DACs QJ30 to QJ42 (DAC8840) as shown in Fig. 3-8-1.

Those signals are used to hold the previous status in reading all regulating data as the power is on, while they are used to recover abnormal data if there occurs something faulty such as noise in output signal in the refresh processing (regular data output processing).

Fig. 3-8-2 DAC8840 timing chart

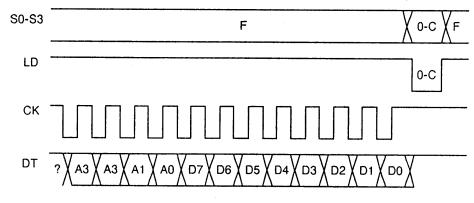

## **3-9. VIDEO SYSTEM CONTROL BLOCK**

In the video system control block, various control signals are supplied through the buffer QA21 (TC74HC541AP) to the following control ICs as shown in Fig. 3-9-1 "Video system control diagram".

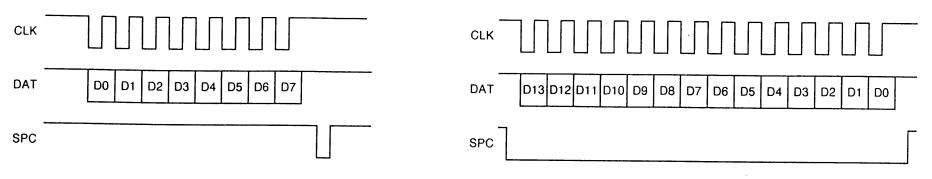

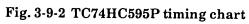

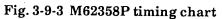

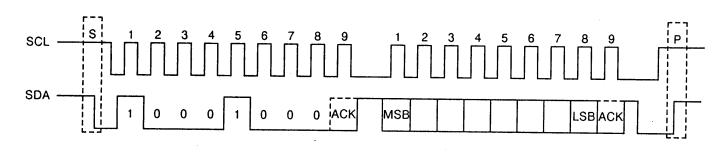

- QA23 (TC74HC595AP), an S/P for the selector, generates signals to switch input signals and test signals on the timing shown in Fig. 3-9-2 "TC74HC595AP timing chart".

- (2) QA22 (M62358P) of a serial control DAC generates mode switching signal and regulating signal for the video system on the timing shown in Fig. 3-9-3 "M62358P timing chart".

- (3) ICA03 (μPD6453CY-514) of the OSD display IC, which is supplied with control signal on the timing shown in Fig. 3-9-2 "μPD6453CY timing chart", generates on-screen character display signal on the timing determined by a free-running frequency according to a V. or H. pulse that is also supplied to QA22.

- (4) IC501 (TA8845N) of the video control LSI generates various video regulating signals on the timing shown in Fig. 3-9-4 "TA8845N timing chart".

Fig. 3-9-1 Video system control diagram

Fig. 3-9-4 TA8845N timing chart

3-14

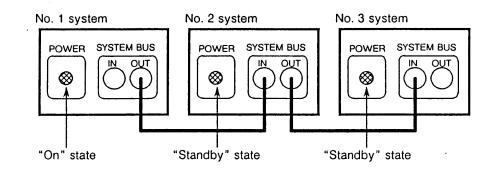

#### 3-10. POWER SOURCE INTERLOCKING MODE

The power source interlocking mode means the status that the power to be supplied to this system is turned on or off interlocking with power on/off operation of the system at the previous stage when multiple systems are connected in daisy chain.

For effectuating the power source interlocking mode in such a multisystem connection as shown in Fig. 3-10-1, only the system at the front of the multi-system connection must be turned on with its power switch on the rear panel set to the "on" position (depressed status), and the other systems following in the connection must be set in the standby mode (power switch is not depressed). In this interlocking setup, the systems following the first system are turned on/off 1 second behind on/off operation of the first system.

When the following systems are set in the standby mode, keep it in mind that they cannot be turned on or off externally by the remote control unit or the RS-232C interface, because the standby mode is provided only for the power source interlocking mode in which the following systems are turned on/off only by the power source interlocking signal.

Moreover, if respective systems need individual operation, set their power switch to the on position, since all the systems are operated as same as the first system in the power source interlocking on mode.

Fig. 3-10-1 Multi-system connection

#### **3-11. SYSTEM CONTROL MODES**

There are some system control modes prepared for operation of this system.

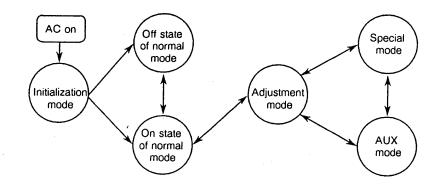

As shown in Fig. 3-11-1, the state transition of the system control modes starts with the "initialization mode" just after the AC power on, and then transfers to the "normal mode". After the normal mode, the state transfers to the "adjustment (ADJUST) mode" that is classified into the "auxiliary (AUX) mode" and the "special mode".

In the initialization mode, the stored data of the rear keys status are read out of the nonvolatile memory besides the last regulating data, and the systems are set in the same operation status as previously done according to the readout data. At the same time, when the power switches are switched on, the systems are set in the "on" state of the normal mode, or, when the power switches are set to standby mode, the systems are set in the "off" state of the normal mode.

In the "off" state of the normal mode, the systems accept the power-on operation only to be ready to transfer to the "on" state of the normal mode. From the "on" state of the normal mode, the systems can be transferred to the "off" state of the normal mode or to the adjustment mode by making choice of the adjustment mode. When the systems are transferred to the adjustment mode, the AUX mode or the special mode is directly selectable besides the general adjustment mode.

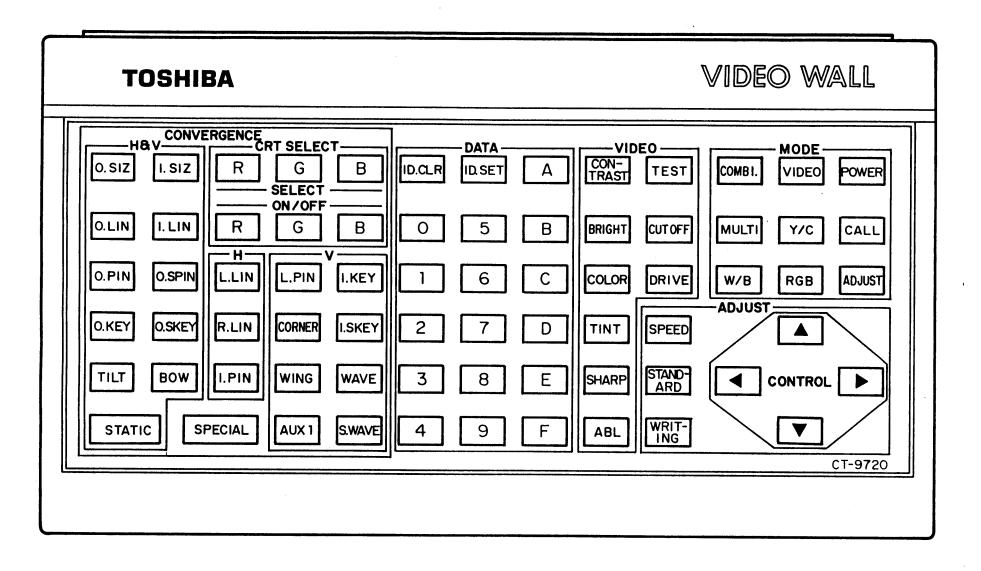

Fig. 3-11-2 is a table of control items operable in relating control modes, while Fig. 3-11-3 shows an outward appearance of the optional remote control unit (CT-9720).

Fig. 3-11-1 Control mode transition diagram

3-16

|          | Control Mode |                                                     |        | Command |     |         |                   |                   |         |     |

|----------|--------------|-----------------------------------------------------|--------|---------|-----|---------|-------------------|-------------------|---------|-----|

| Item     | Sort         | Detail                                              | Normal | Adjust  | AUX | Special | Remote<br>control | unit <sup>]</sup> | RS-232C |     |

| POWER    | MODE         | Power on/off                                        | 0      |         |     |         | \$40              | PON               | POF     |     |

| CALL     | MODE         | Display mode on/off                                 | 0      |         |     |         | \$41              | DON               | DOF     |     |

| ADJUST   | MODE         | Adjustment mode on/off                              | 0      |         |     |         | \$42              | AJY               | AJN     |     |

| · VIDEO  | MODE         | Video input selection                               | 0      |         |     |         | \$43              | IN1               |         |     |

| Y/C      | MODE         | Y/C input selection                                 | 0      |         |     |         | \$44              | IN2               |         |     |

| RGB      | MODE         | R/G/B input selection                               | 0      |         |     |         | \$45              | IN3               |         |     |

| COMBI    | MODE         | Combination on/off                                  | 0      |         |     |         | \$46              | CBY               | CBN     |     |

| MULTI    | MODE         | Multi-mode on/off                                   | 0      |         |     |         | \$47              | MMY               | MMN     |     |

| W/B      | MODE         | White balance 1/2                                   | 0      |         |     |         | \$48              | WB1               | WB2     |     |

| UP       | ADJUST       | Vertical increment of adjustment value              |        | 0       |     |         | \$18              | VLP               |         |     |

| DOWN     | ADJUST       | Vertical decrement of adjustment value              |        | 0       |     |         | \$19              | VDW               |         |     |

| LEFT     | ADJUST       | Horizontal decrement of adjustment value            |        | 0       |     |         | \$1A              | VLF               |         |     |

| RIGHT    | ADJUST       | Horizontal increment of adjustment value            |        | 0       |     |         | \$1B              | VRG               |         |     |

| SPEED    | ADJUST       | Adjustment value increment-decrement rate switching |        | 0       |     |         | \$1C              | VSP               |         |     |

| STANDARD | ADJUST       | Not connected                                       |        | 0       |     |         | \$1D              | VST               |         |     |

| WRITING  | ADJUST       | Adjustment value write selection                    |        | 0       |     |         | \$1E              | VWR               |         |     |

| CONTRAST | VIDEO        | Contrast selection                                  |        | 0       |     |         | \$50              | CNT               |         |     |

| BRIGHT   | VIDEO        | Brightness selection                                |        | 0       |     |         | \$51              | BRT               |         |     |

| COLOR    | VIDEO        | Color selection                                     |        | 0       |     |         | \$52              | COL               |         |     |

| TINT     | VIDEO        | Tint selection                                      |        | 0       |     |         | \$53              | TIN               |         |     |

| SHARP    | VIDEO        | Sharpness selection                                 |        | 0       |     |         | \$54              | SHP               |         |     |

| ABL      | VIDEO        | ABL selection                                       |        | 0       |     |         | \$55              | ABL               |         |     |

| CUTOFF   | VIDEO        | Cutoff selection                                    |        | 0       |     |         | \$57              | LOW               |         |     |

| DRIVE    | VIDEO        | Drive selection                                     |        | 0       |     |         | \$58              | HIG               |         |     |

| TEST     | VIDEO        | Test signal selection (OFF/1/2)                     | 1      | 0       |     |         | \$56              | TOF               | TS1     | TS2 |

Fig. 3-11-2 Control items by mode (1/3)

| Control  |        |                                                                   | Mode Command |        |     | <u></u> |                   |      |         |  |

|----------|--------|-------------------------------------------------------------------|--------------|--------|-----|---------|-------------------|------|---------|--|

| Item     | Sort   | Detail                                                            | Normal       | Adjust | AUX | Special | Remote<br>control | unit | RS-232C |  |

| R-ON/OFF | ON/OFF | Raster R on/off                                                   |              | 0      |     |         | \$15              | RON  | ROF     |  |

| G-ON/OFF | ON/OFF | Raster G on/off                                                   |              | 0      |     |         | \$16              | GON  | GOF     |  |

| B-ON/OFF | ON/OFF | Raster B on/off                                                   |              | 0      |     |         | \$17              | BON  | BOF     |  |

| R-SEL    | SELECT | Raster R selection                                                |              | 0      |     |         | \$12              | SLR  |         |  |

| G-SEL    | SELECT | Raster G selection                                                |              | 0      |     |         | \$13              | SLG  |         |  |

| B-SEL    | SELECT | Raster B selection                                                |              | 0      |     |         | \$14              | SLB  |         |  |

| L SIZ    | H&V    | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$80              | ISZ  |         |  |

| Q SIZ    | H&V    | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$81              | OSZ  |         |  |

| L LIN    | H&V    | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | <b>\$</b> 82      | ILN  |         |  |

| Q LIN    | H&V    | For detail, refer to description of deflection system adjustment. |              | 0      |     | 1       | \$83              | OLN  |         |  |

| Q PIN    | H&V    | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$84              | OPN  |         |  |

| Q SPIN   | H&V    | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$85              | OSP  |         |  |

| QKEY     | H&V    | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$86              | OKY  |         |  |

| QSKEY    | H&V    | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$87              | OSK  |         |  |

| TILT     | H&V    | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$88              | TLT  |         |  |

| BOW      | H&V    | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$89              | BOW  |         |  |

| STATIC   | H&V    | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$8A              | STC  |         |  |

| L PIN    | H      | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | <b>\$</b> 92      | IPN  |         |  |

| L LIN    | H      | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$90              | LLN  |         |  |

| R LIN    | H      | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$91              | RLN  |         |  |

| L PIN    | H      | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$94              | LPN  |         |  |

| CORNER   | v      | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | <b>\$</b> 95      | COR  |         |  |

| WING     | V      | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$96              | WNG  |         |  |

| LKEY     | V      | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$98              | IKY  |         |  |

| ISKEY    | V      | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$99              | ISK  |         |  |

| WAVE     | V      | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$9A              | WAV  |         |  |

| SWAVE    | V      | For detail, refer to description of deflection system adjustment. |              | 0      |     |         | \$9B              | SWV  |         |  |

Fig. 3-11-2 Control items by mode (2/3)

1

|         | Control |                                                    |        |        |     | Mode Command |                   |          |         |   |

|---------|---------|----------------------------------------------------|--------|--------|-----|--------------|-------------------|----------|---------|---|

| Item    | Sort    | Detail                                             | Normal | Adjust | AUX | Special      | Remote<br>control | unit     | RS-232C |   |

| AUX14   | ADJUST  | AUX mode on/off                                    |        | 0      |     |              | \$97              | AUX      |         |   |

| SPECIAL | ADJUST  | Special mode on/off                                |        | 0      |     |              | \$93              | -        |         |   |

| ID. CLR | DATA    | Identity erasure (In case of remote control: "")   |        | 0      |     |              | \$10              | IDC      |         |   |

| ID. SET | DATA    | Identity setting (In case of remote control: "99") |        | 0      |     |              | \$11              | IDS      |         |   |

| 0       | DATA    | Effective in "Special mode"                        |        |        |     | 0            | \$00              | -        |         |   |

| 1       | DATA    | Effective in "AUX mode" or "Special mode"          |        |        | 0   | 0            | \$01              | SHV      |         |   |

| 2       | DATA    | Effective in "AUX mode" or "Special mode"          |        |        | 0   | 0            | \$02              | SHA      |         |   |

| 3       | DATA    | Effective in "AUX mode" or "Special mode"          |        |        | 0   | 0            | \$03              | SHB      |         |   |

| 4       | DATA    | Effective in "AUX mode" or "Special mode"          |        |        | 0   | 0            | \$04              | OSD      |         |   |

| 5       | DATA    | Effective in "AUX mode" or "Special mode"          |        |        | 0   | 0            | \$05              | MNT      |         |   |

| 6       | DATA    | Effective in "Special mode"                        |        |        |     | 0            | \$06              |          |         |   |

| 7       | DATA    | Effective in "Special mode"                        |        |        |     | 0            | \$07              | _        |         |   |

| 8       | DATA    | Effective in "Special mode"                        |        |        |     | 0            | \$08              | ·        |         |   |

| 9       | DATA    | Effective in "Special mode"                        |        |        |     | 0            | \$09              | _        |         |   |

| Α       | DATA    | Not connected                                      |        |        |     |              | \$0A              |          |         |   |

| В       | DATA    | Not connected                                      |        |        |     |              | \$0B              |          |         |   |

| C       | DATA    | Not connected                                      |        |        |     |              | \$0C              | <u> </u> |         |   |

| D       | DATA    | Not connected                                      |        |        |     |              | \$0D              |          |         |   |

| E       | DATA    | Not connected                                      |        |        |     |              | \$0E              |          |         | _ |

| F       | DATA    | Not connected                                      |        |        |     |              | \$0F              |          |         |   |

Fig. 3-11-2 Control items by mode (3/3)

•

Fig. 3-11-3 Outward appearance of remote control unit

3-20

# 3-12. SYSTEM CONTROL BY RS-232C INTERFACE

The following explains the external control method by RS-232C interface.

The signal connection is a straight-line coding through PS02 of the RS-232C connector as shown in Fig. 3-12-1.

| Pin No. | Signal name | Detail of signal  | Input/Output |

|---------|-------------|-------------------|--------------|

| 1       | F.G         | Frame ground      | Input        |

| 2       | RX          | Reception data    | Input        |

| 3       | ТХ          | Transmission data | Output       |

| 7       | S. G        | Signal ground     | Input        |

Fig. 3-12-1 RS-232C connection conditions

Communication conditions should be set as shown in Fig. 3-12-2. For transmission rate, set the speed selector switch on the rear panel of the main unit to "0", "1", "2" or "3" as required; namely, setting to "0" for 1200 baud, "1" for 2400 baud, "2" for 4800 baud and "3" for 9600 baud.

| Communication condition | Detail of condition                                                                                                                                                                                                                                                                                                                    |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Communication method    | Transmission rate: 1200, 2400, 4800, 9600 baud<br>Parity bit: None, Data bit: 8 bits, Stop bit: 1 bit                                                                                                                                                                                                                                  |  |  |

| Communication<br>format | 7-bytes of "STX (1 byte) + IDT (2 bytes) + CMD (3<br>bytes) + EXT (1 byte)" is regarded as a signal block.<br>In the above description, STX is 02 h, ETX is 03 h,<br>IDT is Arabic numerals (0 to 9) and asterisk (*), and<br>CMD is RS-232C command characters listed in Fig.<br>3-11-2.<br>For inputting CMD, do in capital letters. |  |  |

#### Fig. 3-12-2 RS-232C communication conditions

Identity numbers that identify respective systems hooked up in the multi-system connection enable the operator to operate the systems individually or together with at the same time.

Identification can be done with couples of two numerals (0 to 9), and it is theoretically possible to register 100 identity numbers from 00 to 99. However, it is advised not to use "00" as an identity number.

For convenience of multi-system operation, it is recommended to use the asterisk (\*) key for a numeral key, since the asterisk represents all numerals in the same place as it is input; for example, if "\*2" is input for identification, the identity numbers of "02", "12", ...., "92" are subject to operation, or, if "3\*" is input, the identity numbers of "30", "31", ...., "39" are subject to operation.

When transmitting commands, make sure to take an interval of 100 ms at least between two commands. If interval between two commands is too short, it may result in failure in operation owing to misrecognition of the commands.

# **SECTION 4. VIDEO CIRCUIT**

.

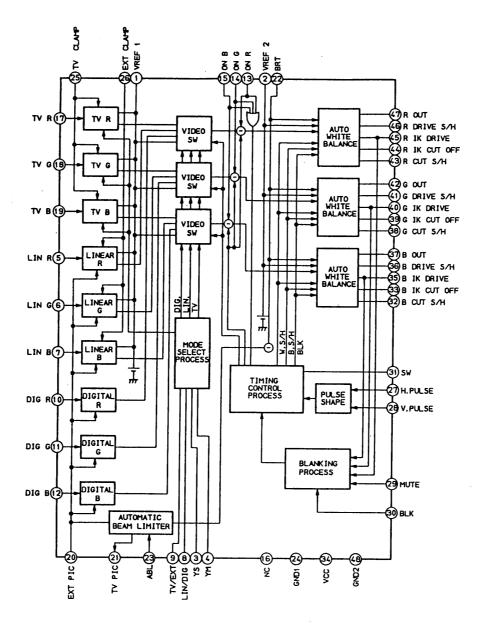

# **4-1. OUTLINE OF VIDEO CIRCUIT**

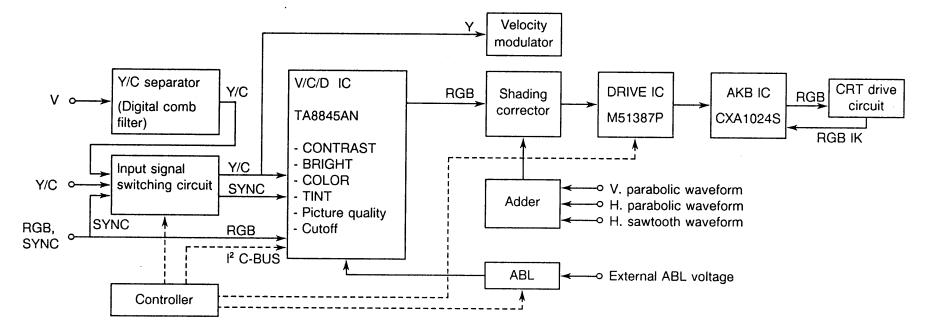

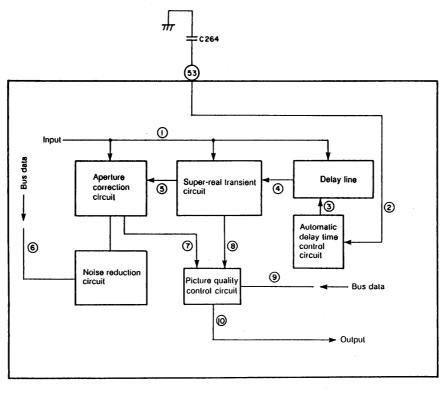

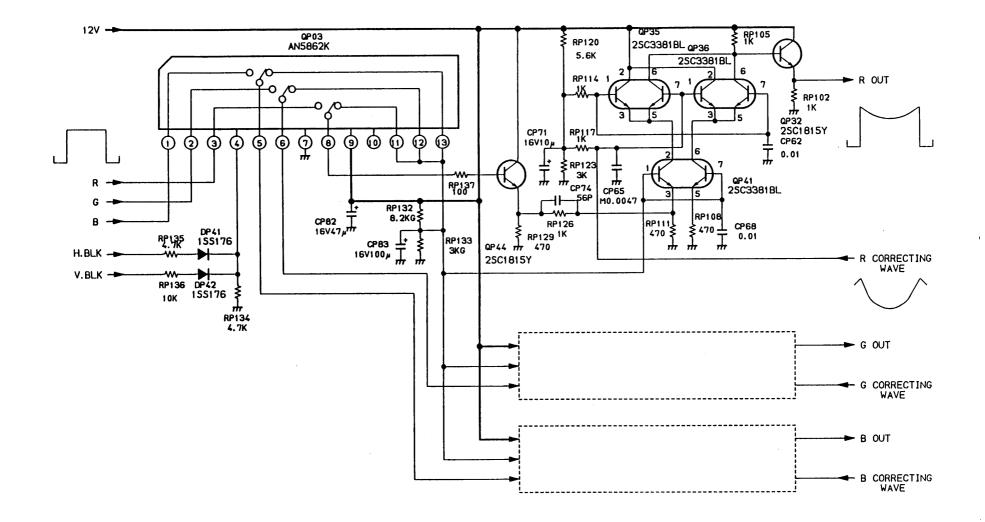

The video circuit operates in switching of input signals, Y/C separation and video chroma processing. Moreover, it performs shading correction (luminance adjustment and irregular color correction), AKB processing and ABL interlocking. Fig. 4-1-1 shows a block diagram of the video circuit.

Composite video signal input to the video circuit is separated into Y (luminance) signal and C (chrominance) signal by the digital comb filter. The Y/C separated video signals are supplied to the V/C/D IC through the signal switcher which switches between the Y/C-separated video signals and externally input Y and C signals. RGB signals are directly input to the V/C/D IC which switches between them and other RGB signals converted from the Y/C-separated signals.

The V/C/D IC controls contrast, brightness, color and tint signals by bus control.

RGB signals whose irregularities in luminance and color are corrected for the multi-screen system by the V/C/D IC are supplied to the drive IC that adjusts gain for white balancing. After that, the RGB signals are input to the AKB IC to compensate age changing of cathode current of the CRT, and further supplied to the CRT after they are amplified by the CRT drive circuit.

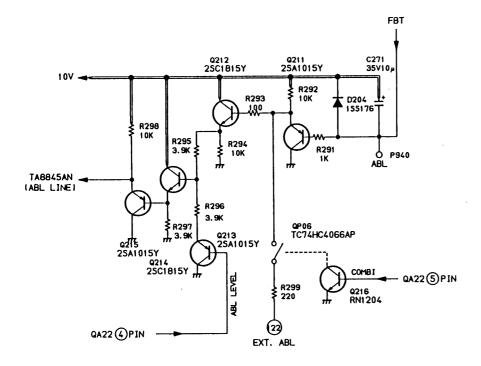

The ABL circuit adjusts ABL voltage of respective projection units interlocking the ABL voltage of all projection units so as to follow the lowest voltage.

Fig. 4-1-1 Video circuit block diagram

4-2

# 4-2. INPUT SIGNAL SWITCHING CIRCUIT

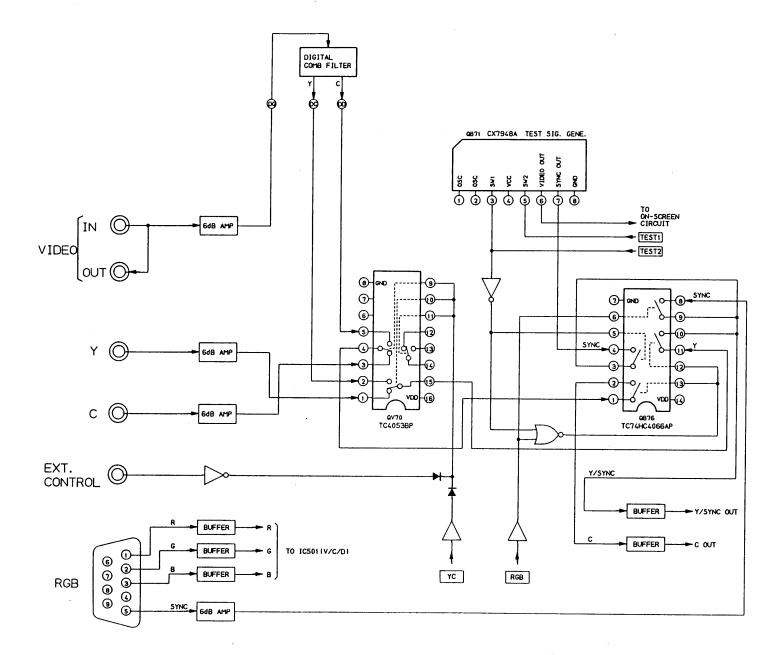

The input signal switching circuit not only switches between composite video signal input and Y & C signal input but also changes over synchronizing signals according to the input mode of RGB signals or internal test signal. A block diagram of the input signal switching circuit is shown in Fig. 4-2-1.

Composite video signal input through the video input terminal is separated into Y and C signals, and then supplied to the signal switcher QV70 of the input signal switching circuit. Since QV70 is supplied with other Y and C signals from the Y/C input terminal, the Y/C-separated signals are switched on/off by the YC control signal in QV70, and they are input to the synchronize changer QB76 if QV70 switches them on. QB76 switches between two synchronizing signals, one is of the Y signal and supplied from the RGB terminals and the other is supplied from QB71 of the test signal generator IC, with the control signals of "RGB" and "TEST1", and QB76 supplies a synchronizing signal to the Y input terminal or the SYNC input terminal of the V/C/D IC, IC501 (TA8845AN).

Table 4-2-1 shows the logic of the input switching. When video input is selected (the level of the control signal "YC" is low), the video input and Y/C input can be switched over by the EXT. CONTROL terminal as shown in Table 4-2-2.

| Input signal/Control signal | YC     | RGB | TEST 1 | TEST 2 |

|-----------------------------|--------|-----|--------|--------|

| VIDEO                       | L      | L   | Н      | Н      |

| Y/C                         | Н      | L   | Н      | Н      |

| RGB                         | L or H | Н   | Н      | Н      |

| TEST1 (cross pattern)       | L or H | L   | L      | L      |

| TEST2 (mesh pattern)        | L or H | L   | L      | H      |

#### Table 4-2-1 Logic of input switching

| EXT. CONTROL terminal | Input signal |  |  |

|-----------------------|--------------|--|--|

| Shortcircuit          | Y/C          |  |  |

| Open circuit          | VIDEO        |  |  |

# Table 4-2-2 Specifications of EXT. CONTROL terminal

4-4

# 4-3. CONTROL SIGNAL GENERATOR CIRCUIT

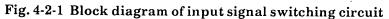

In the control signal generator circuit, the 8-bit serial-in parallel-out shift register QA23 (TC74HC595AP) controls input signal switching with three-wire serial data from the microprocessor, and the D-A converter QA22 (M62358P) outputs analog control voltage. A block diagram of the circuit is shown in Fig. 4-3-1.

QA23 performs parallel output under control of the DATA, CLK and S/P-LAT lines, while QA22 performs D-A conversion under control of the DATA, CLK and DAC-LOD lines. the DATA and CLK lines are used in common with the on-screen display IC, ICA03 ( $\mu$ PD6453CY-514).

#### QA23 (TC74HC595AP)

| Pin<br>No. | Pin<br>Name                                   | Function                           | Output level<br>(H = 5 V, L = 0 V)                    |  |  |

|------------|-----------------------------------------------|------------------------------------|-------------------------------------------------------|--|--|

| 15         | YC                                            | VIDEO/Y,C switching                | VIDEO = L, YC = H                                     |  |  |

| 1          | RGB RGB switching                             |                                    | RGB-H, Normal = L                                     |  |  |

| 2          | 2 TEST 1 Internal test signal switching       |                                    | In reception of TEST signal L,<br>Normal = $H$        |  |  |

| 3          | 3 TEST 2 Internal test signal switching       |                                    | Cross pattern = L,<br>Mesh pattern = H,<br>Normal = H |  |  |

| 4          | 4 VMS Velocity modulation<br>on/off switching |                                    | Fixed at L (ON)                                       |  |  |

| 5          | VMG                                           | Velocity modulation gain switching | Fixed at H (Gain: Max.)                               |  |  |

| 6          | QG                                            | Not connected (open)               |                                                       |  |  |

| 7          | QH                                            | Not connected (open)               |                                                       |  |  |

Names, functions and output levels of output terminals of QA23 and QA22 are respectively shown in Table 4-3-1.

#### QA22 (M62358P)

| Pin<br>No. | Pin<br>Name | Function                          | Output level                                                                                  |

|------------|-------------|-----------------------------------|-----------------------------------------------------------------------------------------------|

| 14         | DRIVE R     | R drive regulation                | 0 ~ 9 V                                                                                       |

| 15         | DRIVE G     | G drive regulation                | 0 ~ 9 V                                                                                       |

| 16         | DRIVE B     | B drive regulation                | 0 ~ 9 V                                                                                       |

| 17         | RASTER R    | R raster switch                   | ON = 0 V, OFF = 5 V                                                                           |

| 18         | RASTER G    | G raster switch                   | ON = 0 V, OFF = 5 V                                                                           |

| 19         | RASTER B    | B raster switch                   | ON = 0 V, OFF = 5 V                                                                           |

| 4          | ABL LEVEL   | ABL voltage<br>regulation         | 0 ~ 9V                                                                                        |

| 5          | COMBI       | ABL interlocking switching        | ON = 0 V, OFF = 5 V                                                                           |

| 6          | MULTI       | Shading correction switching      | ON = 0 V, OFF = 5 V                                                                           |

| 7          | MUTE        | Video muting                      | $\begin{array}{l} \text{MUTE ON} = 5 \text{ V}, \\ \text{MUTE OFF} = 0 \text{ V} \end{array}$ |

| 8          | OSD LEVEL   | On-screen brightness<br>switching | LEVEL 1 = 4.5 V, $LEVEL 2 = 2.25 V$                                                           |

| 9          | A12         | Not connected (open)              |                                                                                               |

**Table 4-3-1**

Fig. 4-3-1 Block diagram of control signal generator circuit

# **4-4. DIGITAL COMB FILTER**

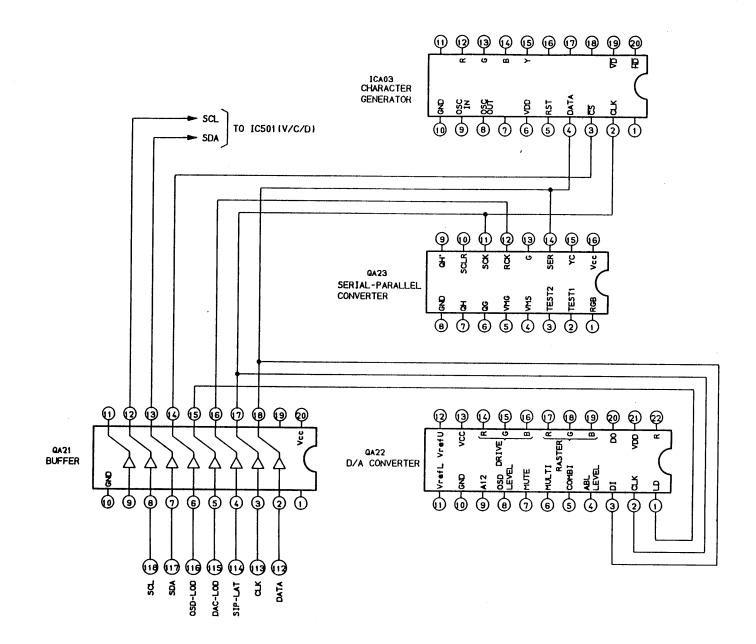

1) Outline

The digital comb filter separates input video signal into Y and C signals with the 2H memory.

As compared with previously used analog 2-CCD comb filters, this digital comb filter is designed to be simplified in adjustment.

|                  | Digital comb filter | 2-CCD comb filter |

|------------------|---------------------|-------------------|

| Adjusting points | Adjustment-free     | 8 points          |

Table 4-4-1Comparison between digital comb filter and<br/>2-CCD comb filter

2) Signal flow

Fig. 4-4-1 shows signal amplitude and DC voltage at main points besides signal flow as a whole.

- 3) ICs used in the circuit

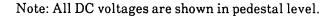

- (1) QZ01 (TC9063N)

This IC, which incorporates an A-D converter, D-A converters and 2H line memory, functions as the Y/C separator with the 2H memory. Its system block diagram is shown in Fig. 4-4-2.

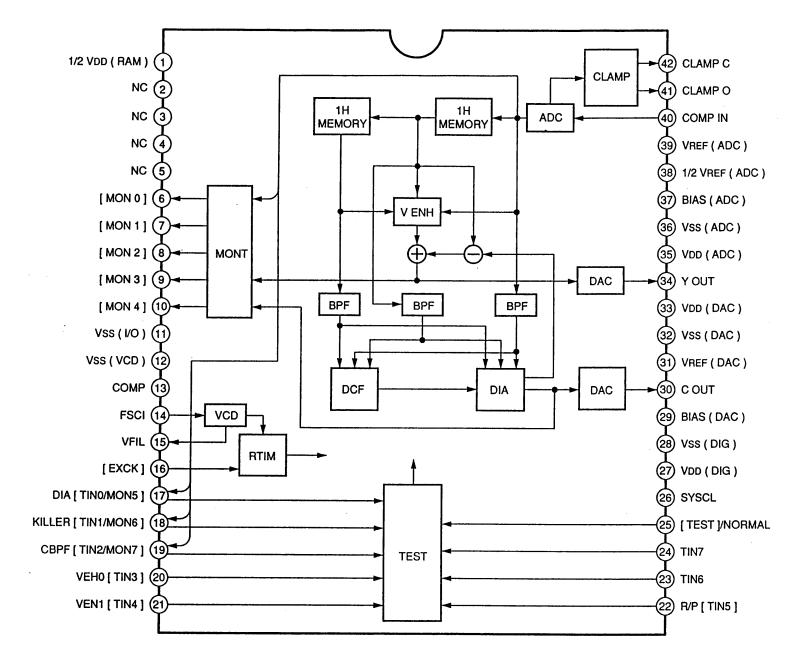

(2) QZ02 (TA8858N)

This IC which has built-in filters, amplifiers, switches, etc. is used in combination with QZ01 (TC9063N). Its system block diagram is shown in Fig. 4-4-3.

(3) QZ03 (TA8749S)

This IC functions as the PLL oscillator, which inputs 1 fsc (3.58 MHz) signal oscillated in the chroma system of the video circuit and outputs 4 fsc (14.3 MHz) signal to QZ01 (TC9063N).

### Fig. 4-4-1 Digital comb filter circuit

Fig. 4-4-2 TC9063N system block diagram

Fig. 4-4-3 TA8858N system block diagram

# 4-5. CHROMA SYSTEM OF VIDEO CIRCUIT

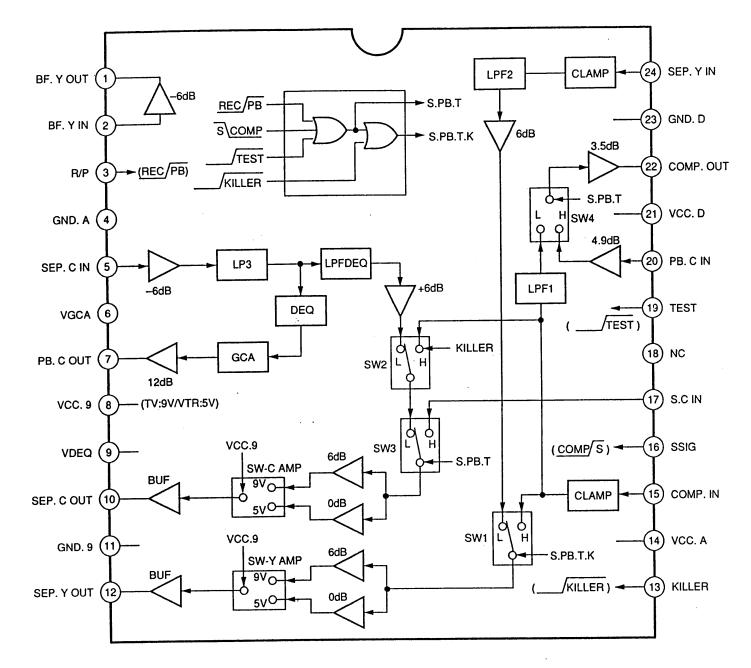

# 4-5-1. Outline of V/C/D IC (TA8845AN)

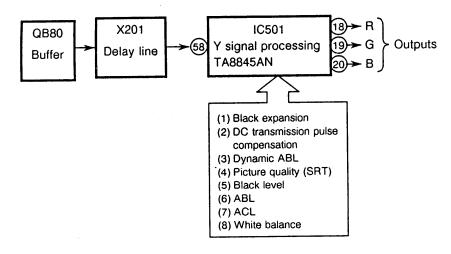

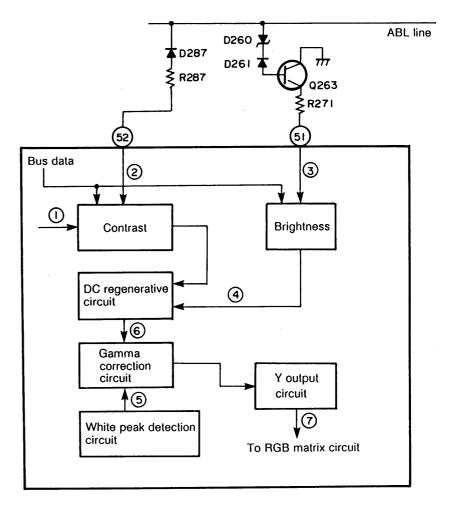

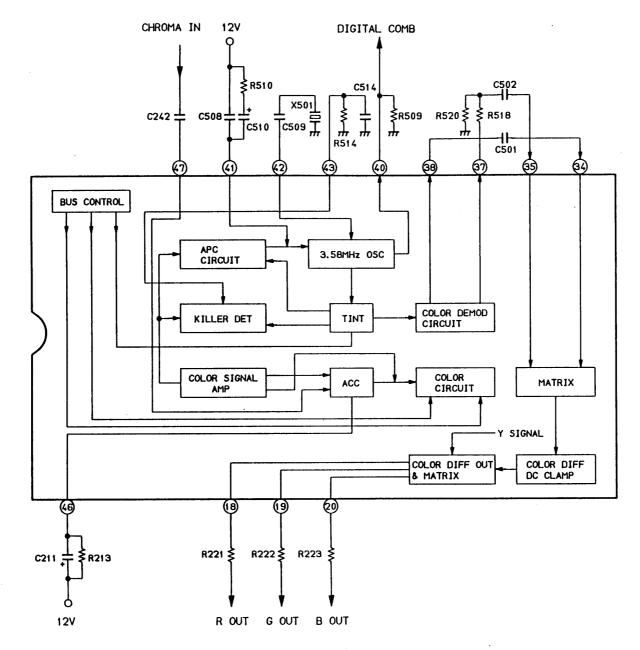

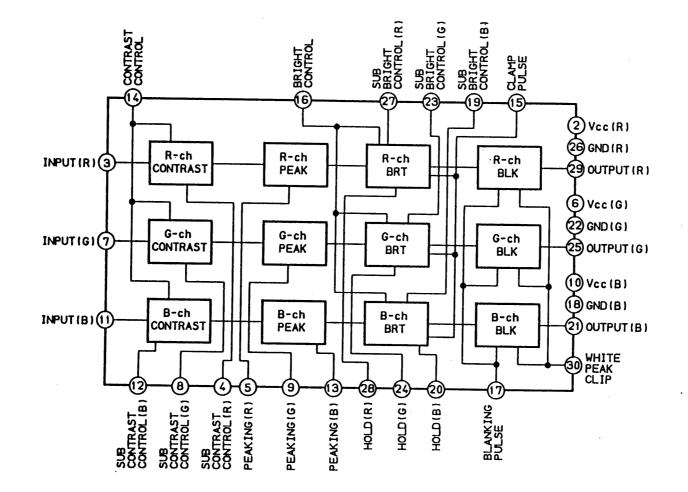

The chroma system of the video circuit employs the V/C/D IC, TA8845N, which is a multi-functional IC for realizing high-quality picture projection, namely, it internally incorporates R/G/B switching circuit, D-A converter for video control by the microprocessor, superreal transient circuit and other functions besides the bus control for white balance adjustment and for manufacture adjustment items.

- 1) Features of respective blocks

- (1) Video signal processing circuit (Video block)

- Besides the basic signal processing circuits such as adjustment circuits for brightness, contrast and quality of picture, DC playback circuit, etc., this block is featured by the following circuits.

- ① Super-real transient circuit

- ② Color detail emphasis circuit

- 3 Active noise reduction circuit

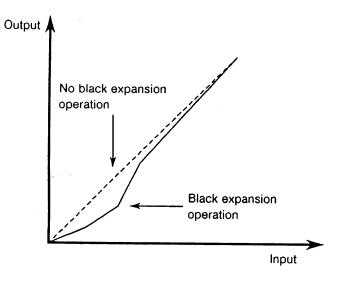

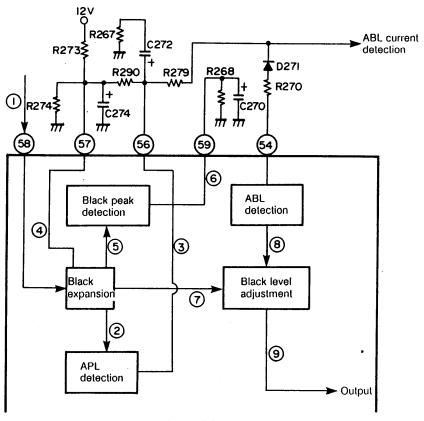

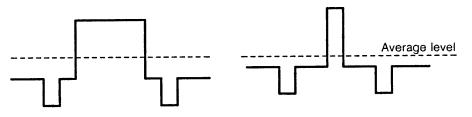

- (4) Black expansion circuit

- (5) High bright color circuit

- 6 White balance control circuit

- ⑦ Cut-off control circuit

- ⑧ Analog RGB circuit

- On-screen display circuit

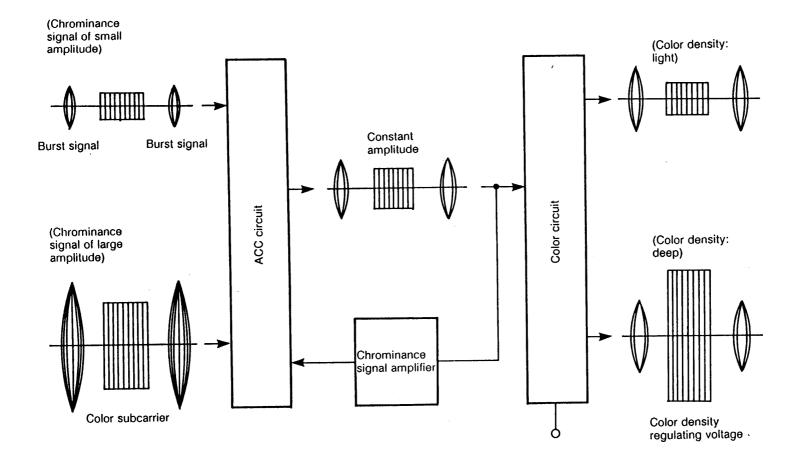

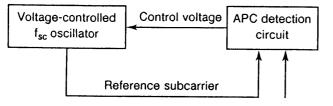

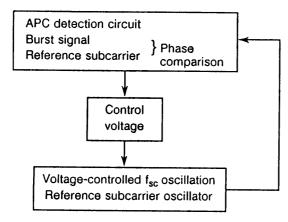

- (2) Chrominance signal processing circuit (Chroma block) This block which is mainly composed of such basic signal processing circuits as ACC (automatic color control circuit), color synchronizing circuit, color demodulation circuit, various tint regulating circuits has the following features.

- ① Adjustment-free 3.58 MHz oscillator thanks to the new circuitry which is hardly influenced by irregularity of IC elements.

- ② I.Q. filter built in the IC.

- 3 New fresh color circuit

- (4) Color limiter circuit

- 5 Color gamma correction circuit

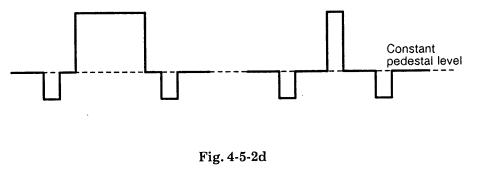

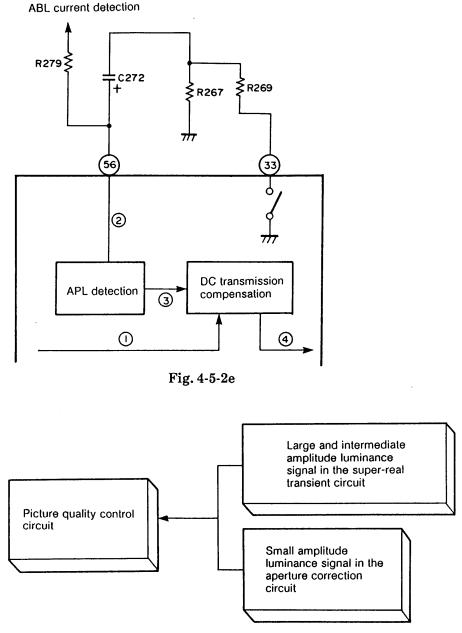

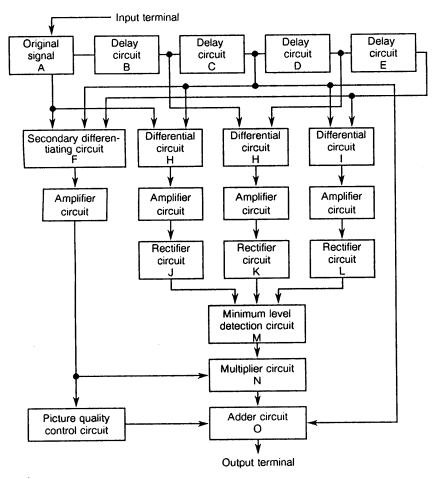

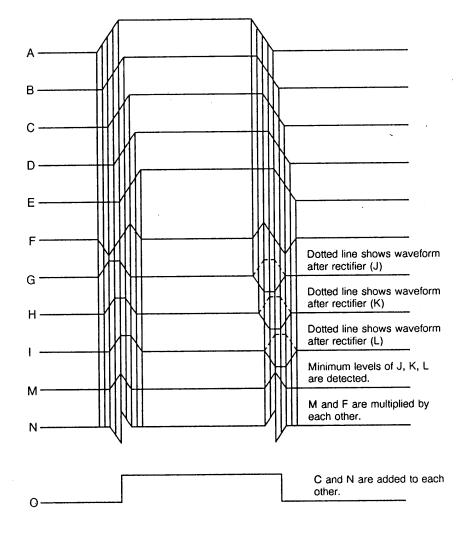

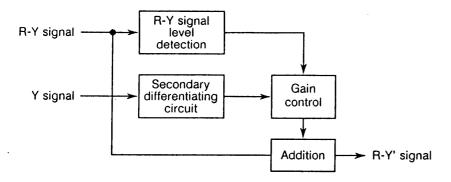

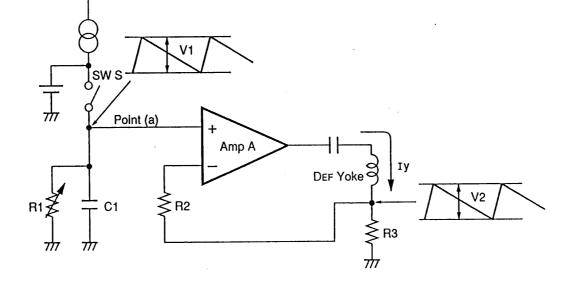

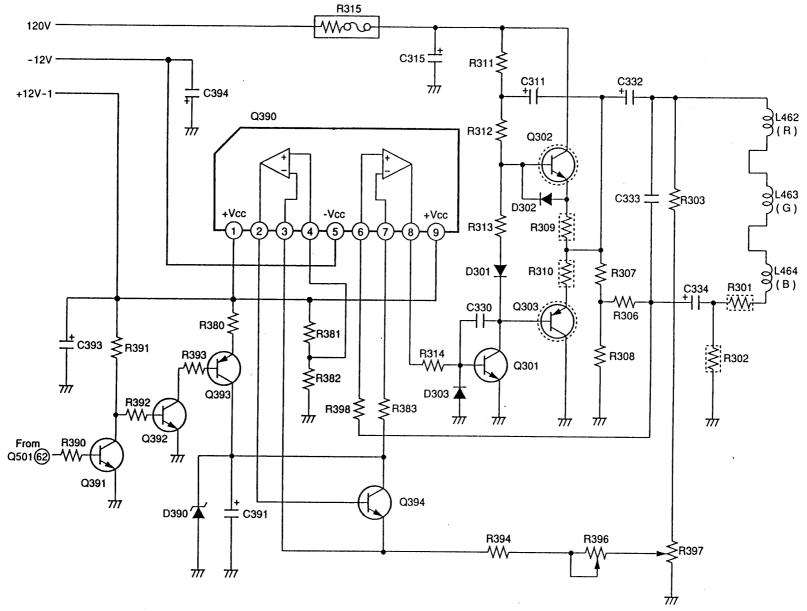

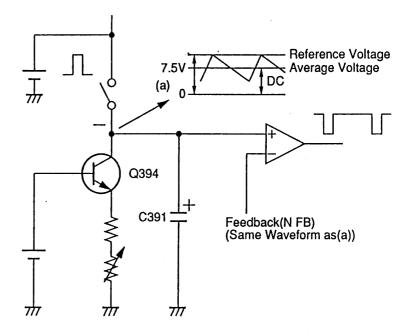

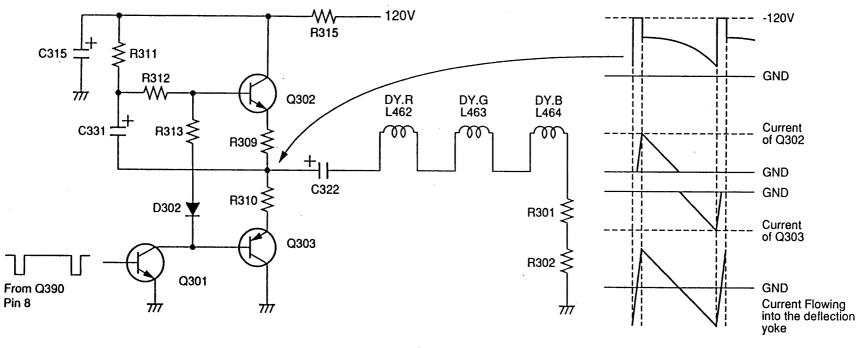

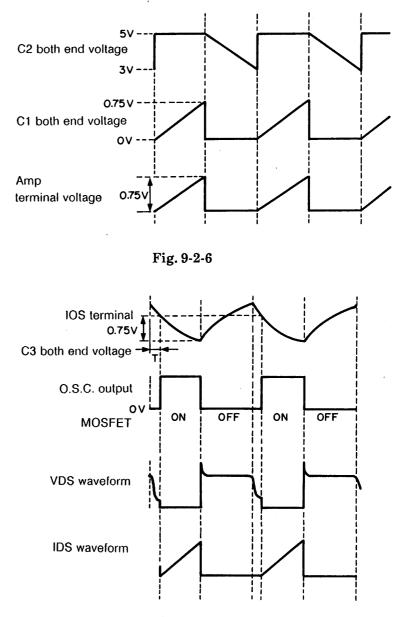

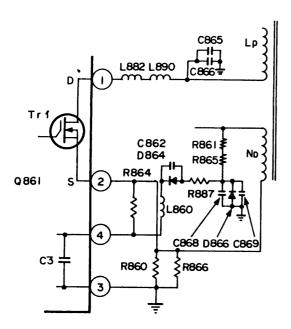

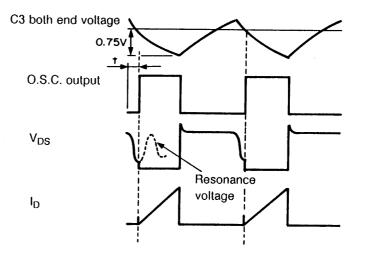

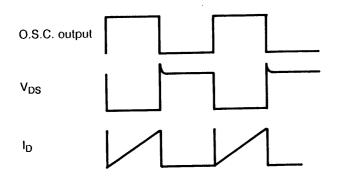

- (3) Deflection processing circuit (Deflection block)