he process of converting an analog voltage into an equivalent digital signal (analog-todigital conversion, commonly referred to as A/D conversion or ADC) is somewhat more complicated than D/A conversion. Over time several methods of A/D conversion—simultaneous, counter, electromechanical, etc. have been developed.

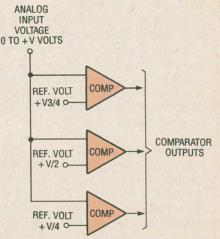

**Simultaneous Conversion.** Simultaneous conversion (probably the simplest of all methods of A/D conversion) uses a number of comparators in its design. The analog signal to be digitized serves as one input to each comparator; the other input to each comparator is connected to its own reference voltage, as shown in Fig. 1. In our example, the reference voltages are +V/4, +V/2, and  $\frac{3}{4}(+V)$ , where +V is the maximum signal voltage the circuit can handle.

If the analog input exceeds the reference voltage to any comparator, that comparator's output goes high. That means there are four voltage ranges that can be detected and effectively discerned by our circuit: If all comparator outputs are low, the analog in-

\*Our gratitude is extended to the EIA/CEG for the creation of this course, especially to the consultants who brought it to fruition: Dr. William Mast, Appalachian State University; Mr. Joseph Sloop, Surry Community College; Dr. Elmer Poe, Eastern Kentucky University. The Digital Microprocessor Course is reprinted here with the permission of the Electronic Industries Association/Consumer Electronic Group (EIA/CEG). The complete parts kit is available from EIA/CEG. For further information, contact EIA/CEG Product Services Department, 1722 Eye Street, NW, Suite 200, Washington, DC 20006; or call 202/457-4986.

put signal must be between 0 and + V/4. If the output of U1 is high, and U2 and U3 are low, then the input must be between + V/4 and + V/2. If U1 and U2 are high while U3 is low, the input must be between + V/2 and  $\frac{3}{4}(+V)$ . Finally, if all comparator outputs are high, the input signal must be between  $\frac{3}{4}(+V)$  and + V/2 and  $\frac{3}{4}(+V)$  and + V/2

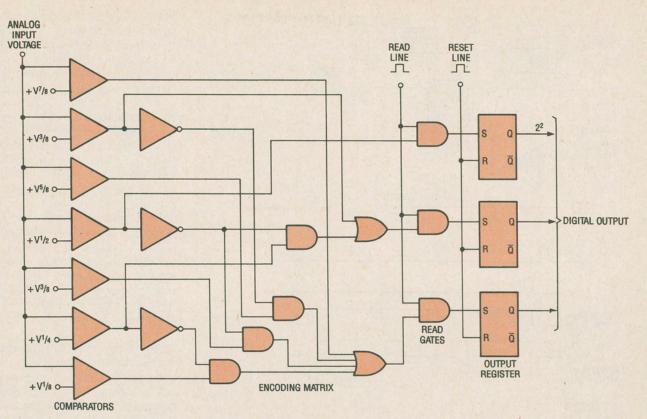

The three comparator's outputs can be fed into a coding network that converts their combined output into a twobit digital value. The bits of the coding network can then be fed to a register for storage and final output.

In order to gain a clear understanding of simultaneous A/D conversion, let's look at the three-bit converter shown in Fig. 2. Note that seven comparators allowing the input to be divided into eight ranges—are required to convert the analog input into a 3-bit digital signal. The simultaneous A/D converter is quite straightforward and relatively easy to understand. However, as the number of bits in the digital number increases, the number of comparators increases very rapidly. Because of that, simultaneous conversion becomes too expensive where larger numbers are involved. So other methods are used for numbers more than three or four bits wide.

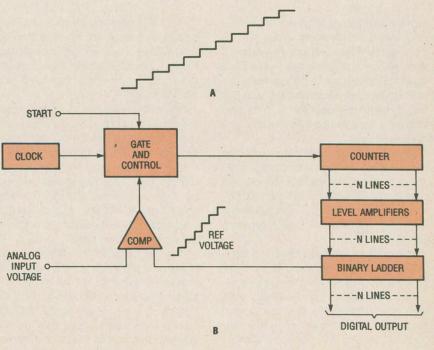

The Counter Method. The counter method of A/D conversion uses only one comparator and a variable reference voltage, which is applied to the comparator. Such a converter contains a simple binary counter, from which the digital output values (and the device's

Fig. 1. Simultaneous conversion requires a number of comparators in its design. The analog signal to be digitized serves as one input to each comparator, the other input to each comparator is a standard reference voltage.

Fig. 2. Seven comparators—allowing the input to be divided into eight ranges—are

required to convert an analog input to a 3-bit digital signal.

name) are derived. The counter must be an *n*-bit counter, where *n* is the desired number of output bits.

At first, the counter output is not sent to the outside world. Instead, the digits it produces are only available to a D/A converter inside the chip via a series of level amplifiers. That converter is a standard binary ladder (like that described in the D/A Converter exercise last month).

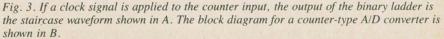

When a clock signal is applied to the counter input, it causes the output of the binary ladder to appear like the staircase waveform shown in Fig. 3A.

## PARTS LIST FOR THE A/D CONVERTER EXERCISE

U1—ADC0804 8-bit analog-to-digital converter, integrated circuit LED1–LED8—Jumbo light-emitting

diode

R1–R8–270-ohm, ¼-watt, 5% resistor R9–10,000-ohm, ¼-watt, 5% resistor R10–100,000-ohm, trimmer

potentiometer C1—150-pF, ceramic-disc capacitor S1—SPST switch

Breadboard, voltmeter, logic probe, +5-

volt power source, wire, etc.

That staircase is used as the reference voltage needed for the comparator (see Fig. 3B). When the reference voltage approximately matches the analog input, the comparator signals the control circuitry.

When that happens, the control circuitry pauses the counter by interrupt-

65

MARCH 1991

Fig. 4. In A we show a control circuit that could be used with the converter shown in Fig. 3B. The waveforms for one conversion are shown here in B.

ing the clock signal. It then allows the counter's current digital value to appear at the chip's output pins via registers. The control circuit then waits for a start signal to coax it into getting the next value. Upon receiving the start signal, it resets the counter to zero and allows clock pulses to reach the counter.

The circuit can be considered a closed-loop control system: An error signal is generated at the comparator output by taking the difference between the analog input and the feedback signal (the staircase reference voltage).

The error is detected by the control circuit, and the clock advances the counter so that the error signal is reduced by increasing the feedback voltage. When the error is reduced to zero, the feedback voltage is equal to the analog input. At that point, the control circuit stops the counter, and the system stops. Although this type of A/D converter offers high resolution and is much simpler than the simultaneous method, it requires a longer conversion time. Because the counter advances one count for each cycle of the clock, the clock determines the maximum conversion rate.

Figure 4A shows a portion of the control circuit that can be used in the converter shown in Fig. 3B. The waveforms for one conversion are shown Fig. 4B. The positive edge of the START pulse is used to reset the counter and to trigger the one-shot (denoted O.S.). The oneshot's output sets the control flip-flop, which allows the clock to advance the counter via an AND gate.

A delay between the counter's RESET pulse and the beginning of the clock pulses ensures that all the flip-flops in the counter are reset before the count begins. Once the reference voltage equals the analog input voltage, the comparator output resets the control flip-flop and stops the count.

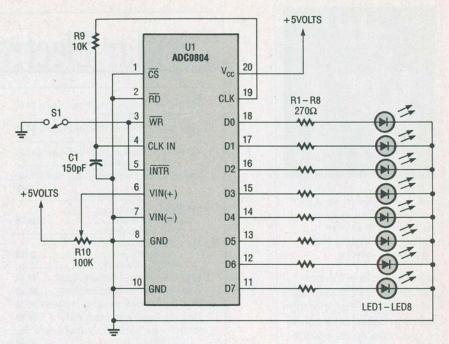

An obvious method for speeding up the process is to eliminate the need to

reset the counter each time a conversion is made. If that were done, the counter would not begin at zero each time, but instead would begin at the value of the last conversion and attempt to alter its value to match the current signal level. However, that means that the counter would have to be capable of counting either up or down. There is also the need for additional logic circuitry, since we must decide whether to count up or down by examining the output of the comparator.

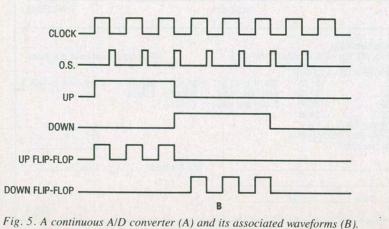

An A/D converter that uses an updown counter—called a continuous A/ D converter—is shown in Fig. 5A. A waveform typical of that converter is shown in Fig. 5B. There are a variety of other methods for digitizing analog signals—too many to discuss in detail in this article—but let's look at a few.

## **Other Converter Configurations.**

The Successive-Approximation method is the process by which an analog voltage is approximated one bit at a time beginning with the MSB (most-significant bit). Each conversion takes the same time and requires one conversion cycle for each bit. So the total conversion time is equal to the number of bits multiplied by the time required for one conversion cycle (normally one clock cycle).

Another method for reducing the total conversion time of a simple counter converter is to divide the counter into sections—that configuration is called a "section counter." To understand how the total conversion time might be reduced by the section method, assume we have a standard eightbit counter. If the counter is divided into two equal counters of four bits each, we have a section converter.

The converter sets the section containing the four least-significant bits (or LSB's) to all 1's and then advances the other section until the ladder voltage exceeds the input voltage. At that point, the four LSB's are reset and advance until the ladder voltage equals the input voltage. Such converters are often used in digital voltmeters.

Electromechanical A/D conversion is another very important method; it involves the translation of the angular position of a shaft into digital information. A common application of that technique is in large radar installations, and many other aircraft and aerospace applications, where the azimuth and *(Continued on page 98)*

## DIGITAL COURSE

(Continued from page 66)

elevation information are determined from shaft position.

A/D Converter Exercise. The majority of measurements, such as light, sound, heat, humidity, etc., yield analoa voltages. In order to use such information with digital circuits, that information must be transformed into logic signals. A circuit capable of performing that conversion is the ADC0804, a TTL-compatible CMOS 8-bit successive-approximation A/D converter that provides an 8-bit binary output. The ADC0804 has a built in clock generator (whose frequency is set by an external RC network), several flip-flops, a binary ladder/ decoder, a comparator, a successiveapproximation register, an 8-bit shift register, output latches, and more.

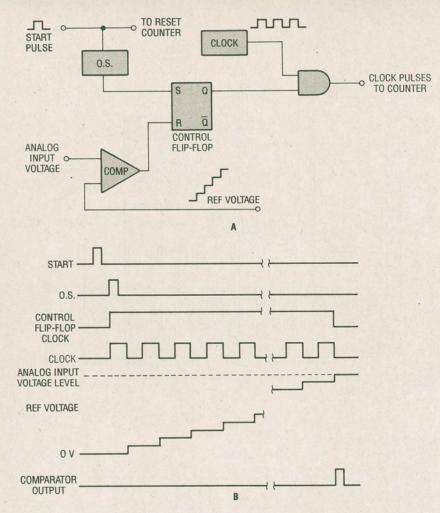

Fig. 6. The ADC0804 is set up in the free-running mode to provide an 8-bit output.

Figure 6 shows the ADC0804 set up to provide an 8-bit digital output based on an analog voltage derived from potentiometer R10. The ADC0804 is set up in the free-running mode by connecting the RD and CS pins to ground. In that mode the IC will continually perform AD conversions. (By the way, switch S1 must be momentarily closed to ensure the start-up of the conversion process.)

Breadboard the circuit in Fig. 6, and apply power (in this case, +5 volts from the previously breadboarded power supply). Monitor the analog input voltage of U1 at pin 6 (V<sub>in</sub>) using a voltmeter. Adjust R10 so that the analog input to the converter at pin 6 is 2.5 volts. If no activity is detected, momentarily close S1. With an analog input of 2.5 volts, what is the digital output, as indicated by the LED's?

Record the analog input and digital output for several settings of R10. Remove power from the circuit. Calculate the analog voltage value from the digital outputs by first changing the digital value into a decimal number. Then divide the decimal number by 256, and multiply the resulting value by the reference voltage (+5 volts) or in mathematical terms:

## $V_{in} = ADC \text{ output} \times 5/256$

How does your calculated output value compare with the known analog input value? How accurately do your calculations reflect the analog input voltages?