# Fundamentals of Electronics

Book 2:

Amplifiers: Analysis and Design

Thomas F. Schubert, Jr. Ernest M. Kim

Synthesis Lectures on Digital Circuits and Systems

## Fundamentals of Electronics Book 2

Amplifiers: Analysis and Design

## Synthesis Lectures on Digital Circuits and Systems

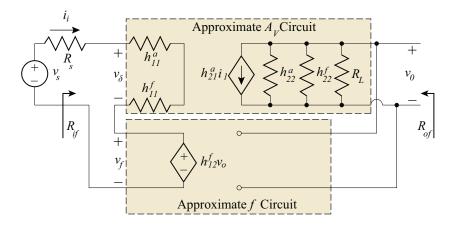

#### Editor

#### Mitchell A. Thornton, Southern Methodist University

The *Synthesis Lectures on Digital Circuits and Systems* series is comprised of 50- to 100-page books targeted for audience members with a wide-ranging background. The Lectures include topics that are of interest to students, professionals, and researchers in the area of design and analysis of digital circuits and systems. Each Lecture is self-contained and focuses on the background information required to understand the subject matter and practical case studies that illustrate applications. The format of a Lecture is structured such that each will be devoted to a specific topic in digital circuits and systems rather than a larger overview of several topics such as that found in a comprehensive handbook. The Lectures cover both well-established areas as well as newly developed or emerging material in digital circuits and systems design and analysis.

Fundamentals of Electronics: Book 2 Amplifiers: Analysis and Design Thomas F. Schubert, Jr. and Ernest M. Kim 2015

Fundamentals of Electronics: Book 1 Electronic Devices and Circuit Applications Thomas F. Schubert and Ernest M. Kim 2015

Applications of Zero-Suppressed Decision Diagrams Tsutomu Sasao and Jon T. Butler 2014

Modeling Digital Switching Circuits with Linear Algebra Mitchell A. Thornton 2014

Arduino Microcontroller Processing for Everyone! Third Edition Steven F. Barrett 2013

Boolean Differential Equations Bernd Steinbach and Christian Posthoff 2013 Bad to the Bone: Crafting Electronic Systems with BeagleBone and BeagleBone Black Steven F. Barrett and Jason Kridner

2013

Introduction to Noise-Resilient Computing

S.N. Yanushkevich, S. Kasai, G. Tangim, A.H. Tran, T. Mohamed, and V.P. Shmerko 2013

Atmel AVR Microcontroller Primer: Programming and Interfacing, Second Edition Steven F. Barrett and Daniel J. Pack

2012

Representation of Multiple-Valued Logic Functions

Radomir S. Stankovic, Jaakko T. Astola, and Claudio Moraga 2012

Arduino Microcontroller: Processing for Everyone! Second Edition

Steven F. Barrett

2012

Advanced Circuit Simulation Using Multisim Workbench

David Báez-López, Félix E. Guerrero-Castro, and Ofelia Delfina Cervantes-Villagómez 2012

Circuit Analysis with Multisim

David Báez-López and Félix E. Guerrero-Castro 2011

Microcontroller Programming and Interfacing Texas Instruments MSP430, Part I

Steven F. Barrett and Daniel J. Pack

2011

Microcontroller Programming and Interfacing Texas Instruments MSP430, Part II

Steven F. Barrett and Daniel J. Pack

2011

Pragmatic Electrical Engineering: Systems and Instruments

William Eccles

2011

Pragmatic Electrical Engineering: Fundamentals

William Eccles

2011

Introduction to Embedded Systems: Using ANSI C and the Arduino Development

Environment

David J. Russell

2010

#### Arduino Microcontroller: Processing for Everyone! Part II

Steven F. Barrett 2010

#### Arduino Microcontroller Processing for Everyone! Part I

Steven F. Barrett 2010

#### Digital System Verification: A Combined Formal Methods and Simulation Framework

Lun Li and Mitchell A. Thornton 2010

#### Progress in Applications of Boolean Functions

Tsutomu Sasao and Jon T. Butler 2009

#### Embedded Systems Design with the Atmel AVR Microcontroller: Part II

Steven F. Barrett 2009

#### Embedded Systems Design with the Atmel AVR Microcontroller: Part I

Steven F. Barrett 2009

Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller II: Digital and Analog Hardware Interfacing

Douglas H. Summerville 2009

Designing Asynchronous Circuits using NULL Convention Logic (NCL)

Scott C. Smith and JiaDi 2009

## Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller I: Assembly Language Programming

Douglas H.Summerville 2009

#### Developing Embedded Software using DaVinci & OMAP Technology

B.I. (Raj) Pawate 2009

#### Mismatch and Noise in Modern IC Processes

Andrew Marshall

2009

### Asynchronous Sequential Machine Design and Analysis: A Comprehensive Development of the Design and Analysis of Clock-Independent State Machines and Systems

Richard F. Tinder

2009

#### An Introduction to Logic Circuit Testing

Parag K. Lala 2008

#### Pragmatic Power

William J. Eccles

2008

#### Multiple Valued Logic: Concepts and Representations

D. Michael Miller and Mitchell A. Thornton

#### Finite State Machine Datapath Design, Optimization, and Implementation

Justin Davis and Robert Reese

2007

#### Atmel AVR Microcontroller Primer: Programming and Interfacing

Steven F. Barrett and Daniel J. Pack

2007

#### Pragmatic Logic

William J. Eccles

2007

#### PSpice for Filters and Transmission Lines

Paul Tobin

2007

#### PSpice for Digital Signal Processing

Paul Tobin

2007

#### PSpice for Analog Communications Engineering

Paul Tobin

2007

#### PSpice for Digital Communications Engineering

Paul Tobin

2007

#### PSpice for Circuit Theory and Electronic Devices

Paul Tobin

2007

#### Pragmatic Circuits: DC and Time Domain

William J. Eccles

2006

#### Pragmatic Circuits: Frequency Domain

William J. Eccles

2006

#### Pragmatic Circuits: Signals and Filters

William J. Eccles 2006

#### High-Speed Digital System Design

Justin Davis 2006

## Introduction to Logic Synthesis using Verilog HDL Robert B.Reese and Mitchell A.Thornton

2006

#### Microcontrollers Fundamentals for Engineers and Scientists

Steven F. Barrett and Daniel J. Pack 2006

#### Copyright © 2016 by Morgan & Claypool

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopy, recording, or any other except for brief quotations in printed reviews, without the prior permission of the publisher.

Fundamentals of Electronics: Book 2 Amplifiers: Analysis and Design

Thomas F. Schubert, Jr. and Ernest M. Kim

www.morganclaypool.com

ISBN: 9781627055642 paperback ISBN: 9781627055659 ebook

DOI 10.2200/S00680ED1V01Y201510DCS047

A Publication in the Morgan & Claypool Publishers series SYNTHESIS LECTURES ON DIGITAL CIRCUITS AND SYSTEMS

Lecture #47

Series Editor: Mitchell A. Thornton, Southern Methodist University

Series ISSN

Print 1932-3166 Electronic 1932-3174

## Fundamentals of Electronics Book 2

Amplifiers: Analysis and Design

Thomas F. Schubert, Jr. and Ernest M. Kim University of San Diego

SYNTHESIS LECTURES ON DIGITAL CIRCUITS AND SYSTEMS #47

#### **ABSTRACT**

This book, Amplifiers: Analysis and Design, is the second of four books of a larger work, Fundamentals of Electronics. It is comprised of four chapters that describe the fundamentals of amplifier performance. Beginning with a review of two-port analysis, the first chapter introduces the modeling of the response of transistors to AC signals. Basic one-transistor amplifiers are extensively discussed. The next chapter expands the discussion to multiple transistor amplifiers. The coverage of simple amplifiers is concluded with a chapter that examines power amplifiers. This discussion defines the limits of small-signal analysis and explores the realm where these simplifying assumptions are no longer valid and distortion becomes present. The final chapter concludes the book with the first of two chapters in Fundamental of Electronics on the significant topic of feedback amplifiers.

Fundamentals of Electronics has been designed primarily for use in an upper division course in electronics for electrical engineering students. Typically such a course spans a full academic years consisting of two semesters or three quarters. As such, Amplifiers: Analysis and Design, and two other books, Electronic Devices and Circuit Applications, and Active Filters and Amplifier Frequency Response, form an appropriate body of material for such a course. Secondary applications include the use with Electronic Devices and Circuit Applications in a one-semester electronics course for engineers or as a reference for practicing engineers.

#### **KEYWORDS**

active loads, amplifier configurations, amplifiers, cascaded amplifiers, cascode, current mirror, current sources, Darlington amplifiers, distortion, feedback amplifiers, feedback topologies: shunt-series feedback, series-series feedback, series-shunt feedback, shunt-shunt feedback; gain, multistage amplifiers, optimal biasing, power amplifiers: class A, class B, class AB, push-pull; return difference, transistor modeling, two-port networks: *b*-parameters, *g*-parameters, *z*-parameters, *y*-parameters; thermal modeling

## **Contents**

|   | Prefa | ce                                                                       |

|---|-------|--------------------------------------------------------------------------|

|   | Ackn  | owledgmentsxvii                                                          |

| 5 | Sing  | le Transistor Amplifiers                                                 |

|   | 5.1   | Review of Two-port Network Basics                                        |

|   |       | 5.1.1 Circuit Representation of a Two-port Network                       |

|   | 5.2   | BJT Low-frequency Models                                                 |

|   |       | 5.2.1 Determination of $h_{ie}$ and $h_{fe}$                             |

|   |       | 5.2.2 Determination of $h_{re}$ and $h_{oe}$                             |

|   | 5.3   | Common-Emitter Amplifiers                                                |

|   |       | 5.3.1 Common-Emitter Amplifiers with Non-zero Emitter Resistance 326     |

|   |       | 5.3.2 The Effect of Non-Zero $h_{oe}$ on Common-Emitter Amplifiers with  |

|   |       | an Emitter Resistor                                                      |

|   |       | 5.3.3 Coupling and Bypass Capacitors                                     |

|   |       | 5.3.4 Summary of Common-Emitter Amplifier Properties                     |

|   | 5.4   | Common-Collector Amplifiers                                              |

|   |       | 5.4.1 The Effect of Non-zero $h_{oe}$ on Common-Collector Amplifiers 343 |

|   | 5.5   | Common-Base Amplifiers                                                   |

|   |       | 5.5.1 The Effect of Non-zero $h_{oe}$ on Common-Base Amplifiers          |

|   | 5.6   | Comparison of BJT Amplifier Types                                        |

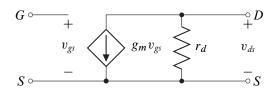

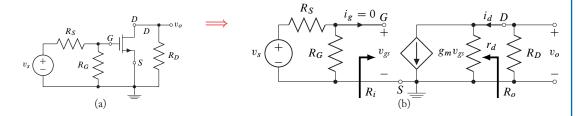

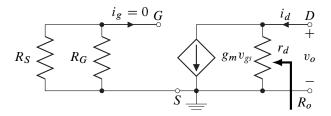

|   | 5.7   | FET Low-Frequency Models                                                 |

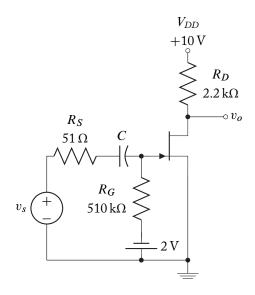

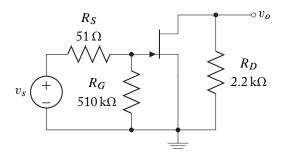

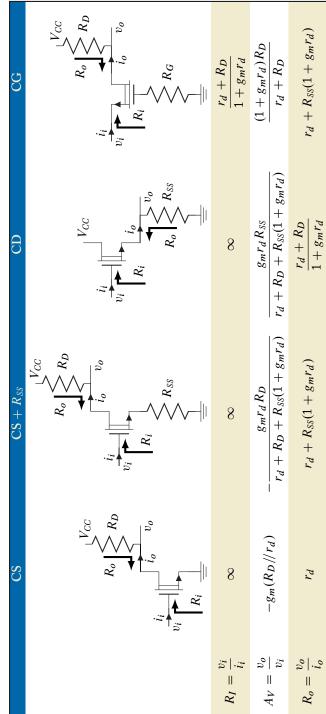

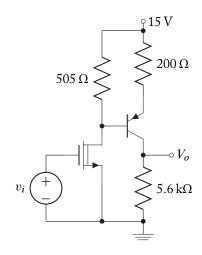

|   | 5.8   | Common-source Amplifiers                                                 |

|   |       | 5.8.1 Common-Source Amplifiers with Non-zero Source Resistance 367       |

|   | 5.9   | Common-Drain Amplifiers                                                  |

|   | 5.10  | Common-Gate Amplifiers                                                   |

|   | 5.11  | Comparison of FET Amplifier Types                                        |

|   | 5.12  | Biasing to Achieve Maximum Symmetrical Swing                             |

|   | 5.13  | Concluding Remarks                                                       |

|   | 5.14  | Problems                                                                 |

|   |       | References                                                               |

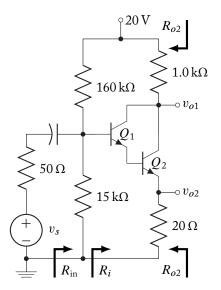

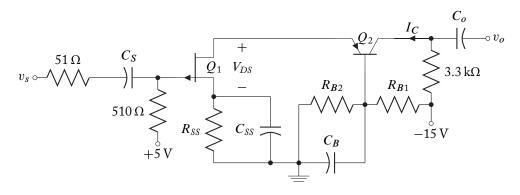

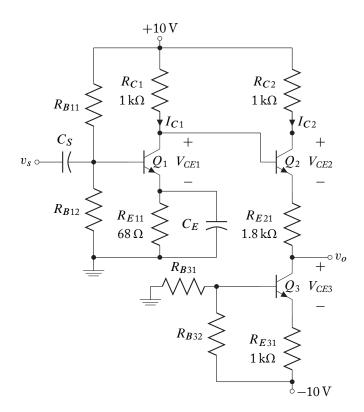

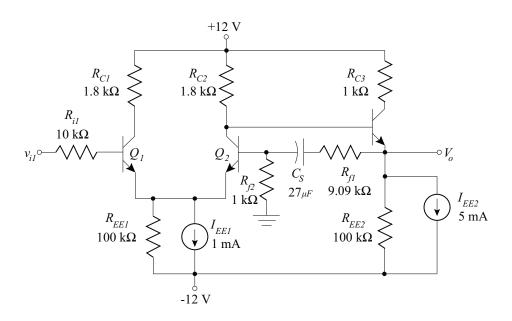

| 6 | Mul | ltiple-Transistor Amplifiers                                  | 423 |

|---|-----|---------------------------------------------------------------|-----|

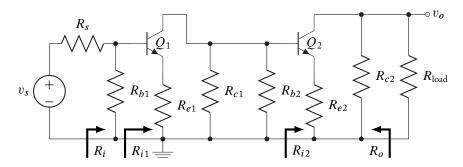

|   | 6.1 | Multistage Amps Using Simple Stages Cascaded                  | 424 |

|   |     | 6.1.1 Design Choices for Transistor Configuration in a        |     |

|   |     | Cascade-Connected Amplifier                                   | 432 |

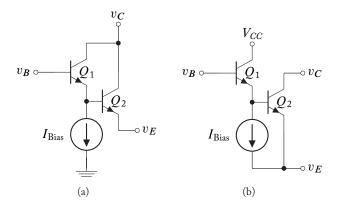

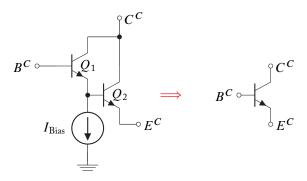

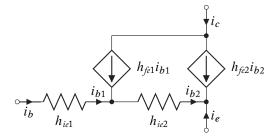

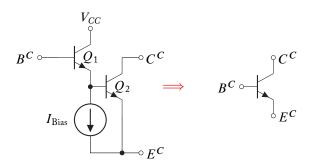

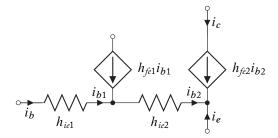

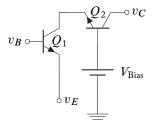

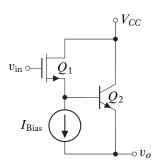

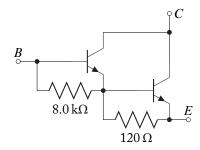

|   | 6.2 | Darlington and Other Similar Configurations                   |     |

|   |     | 6.2.1 The Darlington Configurations                           | 433 |

|   |     | 6.2.2 The Dual Common-Collector Darlington Configuration      |     |

|   |     | 6.2.3 The Common-Collector—Common-Emitter Darlington Pair     |     |

|   |     | 6.2.4 The Cascode Configuration                               |     |

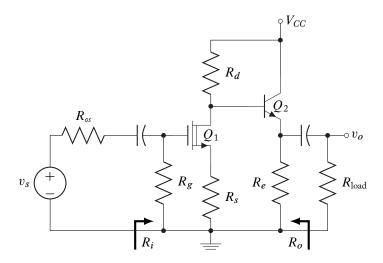

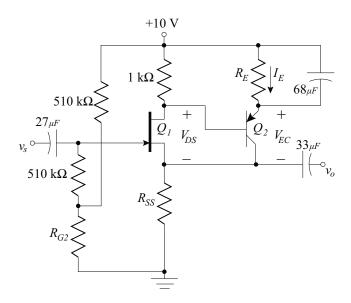

|   |     | 6.2.5 The BiFET Darlington Configuration                      |     |

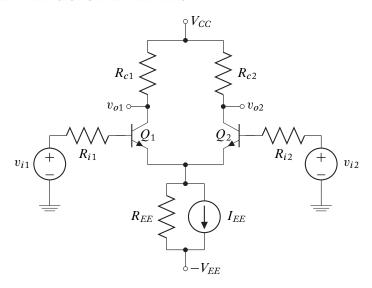

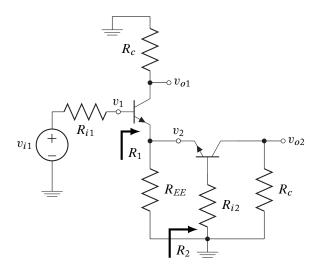

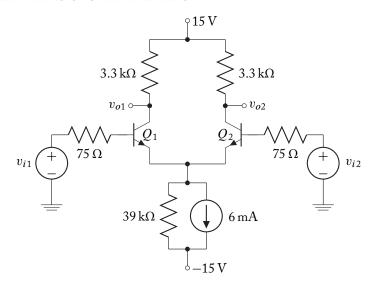

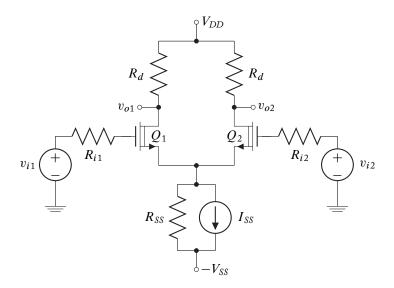

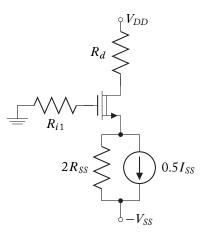

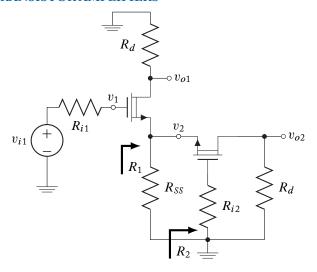

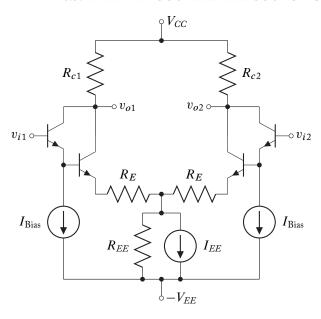

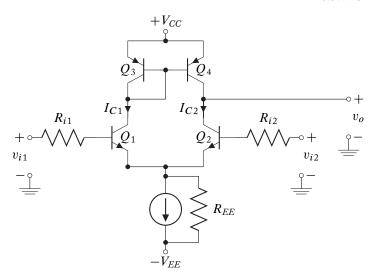

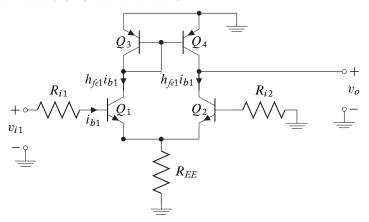

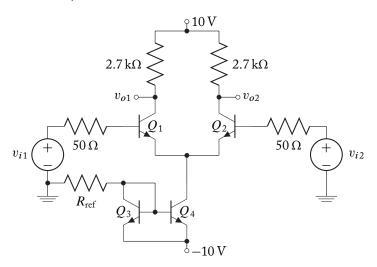

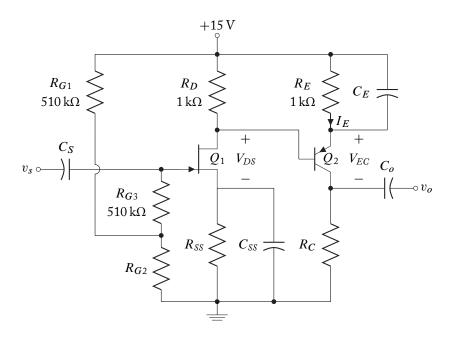

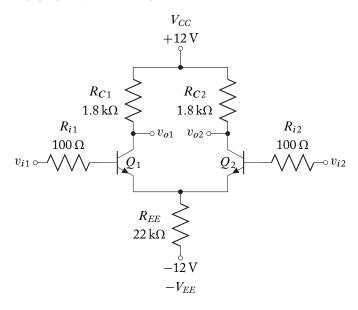

|   | 6.3 | Emitter-Coupled And Source-Coupled Pairs                      | 449 |

|   |     | 6.3.1 Emitter-Coupled Pairs                                   |     |

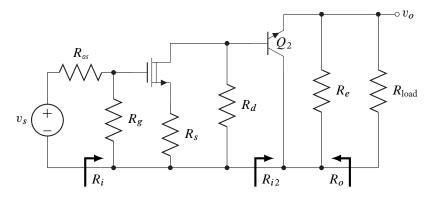

|   |     | 6.3.2 Source-Coupled Pairs                                    |     |

|   |     | 6.3.3 Variations on the Theme                                 |     |

|   |     | 6.3.4 Summary                                                 | 463 |

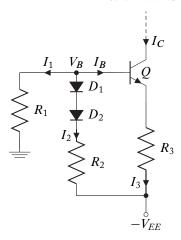

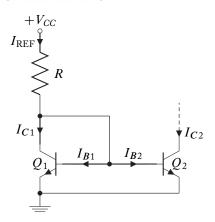

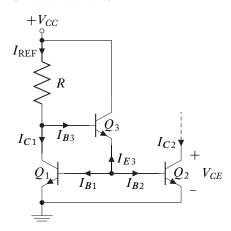

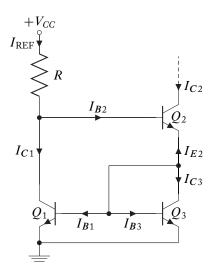

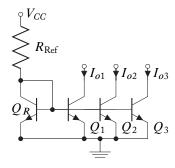

|   | 6.4 | Transistor Current Sources                                    |     |

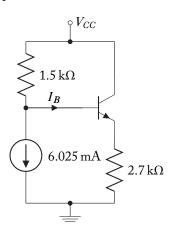

|   |     | 6.4.1 Simple Bipolar Current Source                           |     |

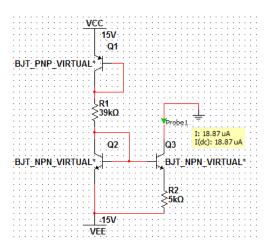

|   |     | 6.4.2 Current Mirror                                          |     |

|   |     | 6.4.3 Current Mirror with Additional Stability                |     |

|   |     | 6.4.4 Wilson Current Source                                   |     |

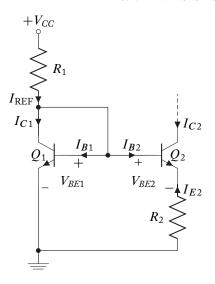

|   |     | 6.4.5 Widlar Current Source                                   |     |

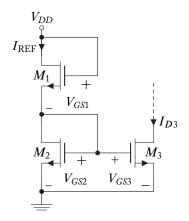

|   |     | 6.4.6 Simple MOSFET Current Mirror                            |     |

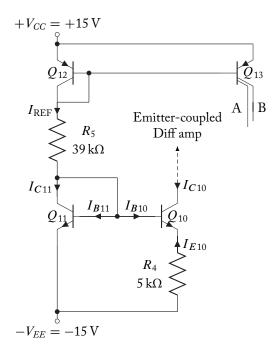

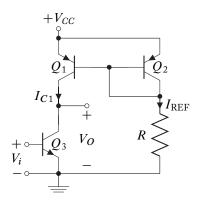

|   | 6.5 | Active Loads                                                  |     |

|   |     | 6.5.1 Common-Emitter Amplifier with Active Load               |     |

|   |     | 6.5.2 Common Source Amplifier with Active Load                |     |

|   |     | 6.5.3 Emitter-Coupled Differential Amplifier with Active Load |     |

|   | 6.6 | Concluding Remarks                                            |     |

|   | 6.7 | Problems                                                      |     |

|   |     | References                                                    | 510 |

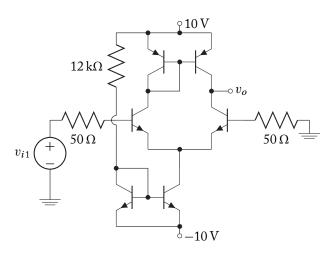

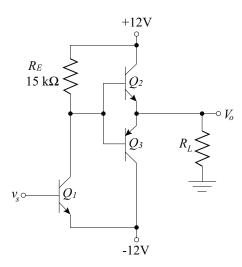

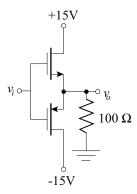

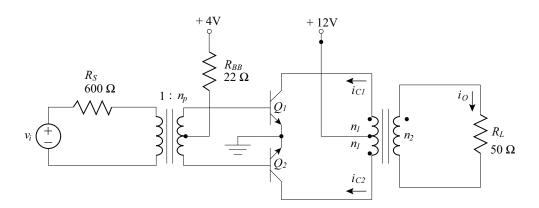

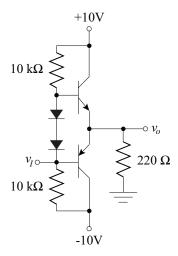

| 7 | Pow | ver Amplifiers and Output Stages                              | 511 |

| ' | 7.1 | Power Amplifier Classification                                |     |

|   | ,,, | 7.1.1 Classification Scheme                                   |     |

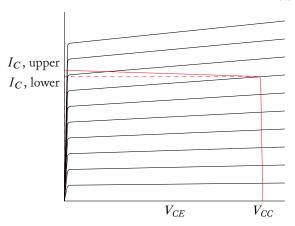

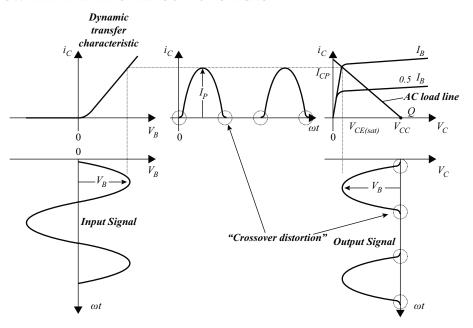

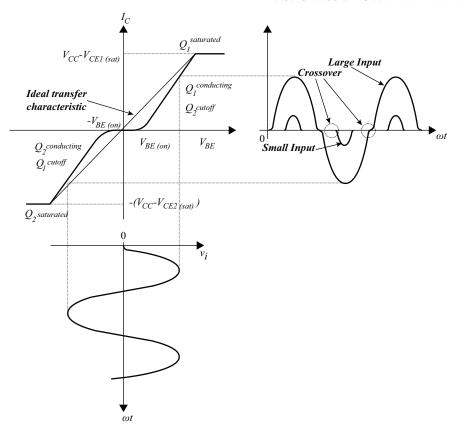

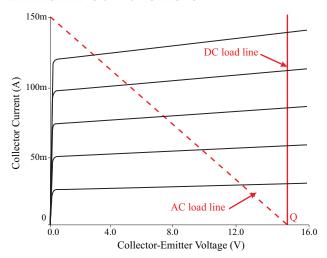

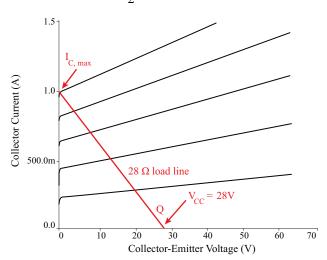

|   |     | 7.1.2 Limits on Distortionless "Small-Signal" Operation       |     |

|   | 7.2 | Class A Power Amplifiers                                      |     |

|   |     | 7.2.1 Common-Collector                                        |     |

|   |     | 7.2.2 Common-Emitter                                          |     |

|   |   | ٠ | ٠ |

|---|---|---|---|

| v | п | 1 | 1 |

|      | 7.2.3 Transformer-Coupled Class A Power Amplifier       |

|------|---------------------------------------------------------|

| 7.3  | Class B Power Amplifiers                                |

|      | 7.3.1 Complementary Class B (Push-Pull) Output Stage541 |

| 7.   | Class AB Power Amplifiers                               |

| 7.   | 5 Distortion                                            |

| 7.0  |                                                         |

| 7.   | 7 Concluding Remarks                                    |

| 7.   |                                                         |

|      | References                                              |

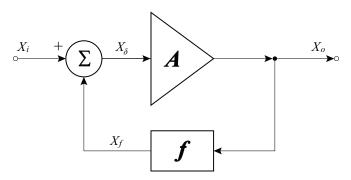

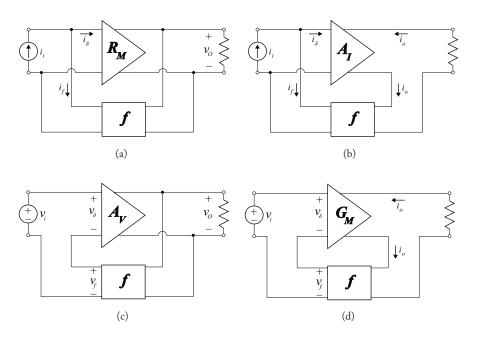

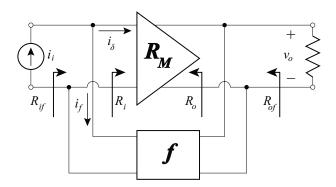

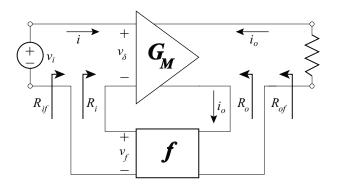

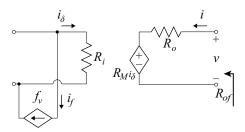

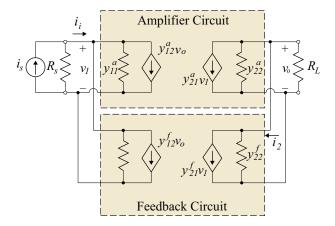

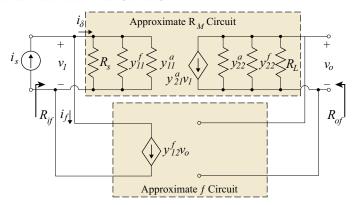

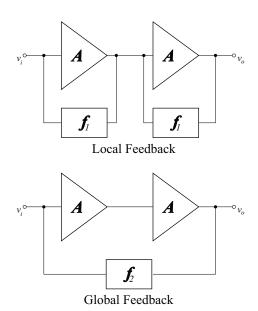

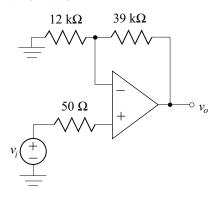

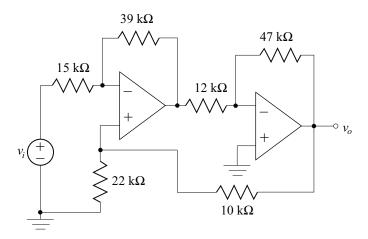

| 8 Fe | redback Amplifier Principles                            |

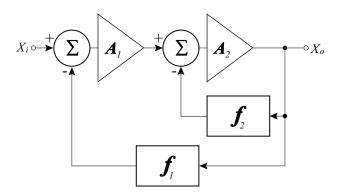

| 8.   | Basic Feedback Concepts                                 |

| 8.2  | 2 Feedback Amplifier Topologies                         |

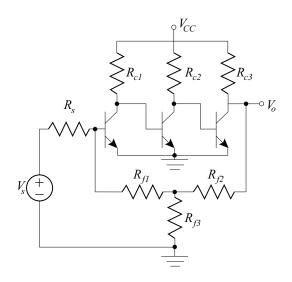

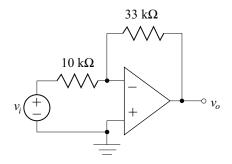

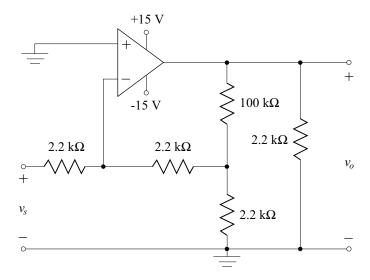

| 8.   | B Practical Feedback Configurations                     |

|      | 8.3.1 Shunt-Shunt Feedback                              |

|      | 8.3.2 Shunt-Series Feedback                             |

|      | 8.3.3 Series-Shunt Feedback                             |

|      | 8.3.4 Series-Series Feedback                            |

| 8.4  | 4 Concluding Remarks                                    |

| 8    | 5 Problems                                              |

|      | References                                              |

| A    | uthors' Biographies                                     |

## **Preface**

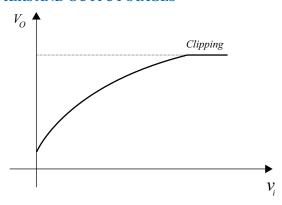

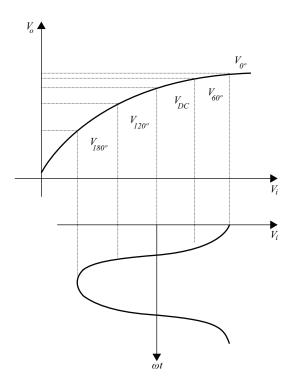

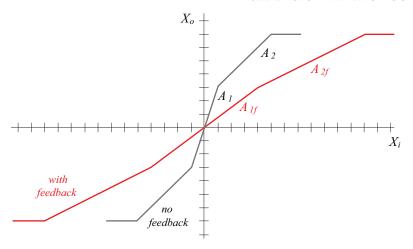

The basic principles of the operation of the four basic active elements, as described in Book 1, provide a good foundation for further study of electronic circuitry. Analog amplifiers constitute a major class of electronic circuitry and are a primary component in many applications. While it has been shown that electronic devices are basically non-linear, amplifiers typically operate within a region of incremental linearity. That is, a region where small variation in the input produces linearly amplified variation in the output. Analysis of such systems uses the principle of superposition: DC (or bias) conditions are separated from the AC (or variational) components of the input and output of an amplifier. The term "small-signal analysis" refers the use of linear models. "Large-signal analysis" implies operation near the transition between operational regions of an active device: such large-signal operation is typically non-linear and leads to distorted amplification.

This book begins with a review of two-port analysis. This review provides a basis for modeling transistors: they are most commonly modeled as two-port networks for small-signal analysis. At low frequencies the BJT is modeled by an *h*-parameter two-port and the FET as a modified hybrid- two-port. Simple amplifiers are approached by observing the previously observed region of operation that appeared between the two logic states of an inverter. All single-transistor amplifier configurations are analyzed and performance characteristics compared.

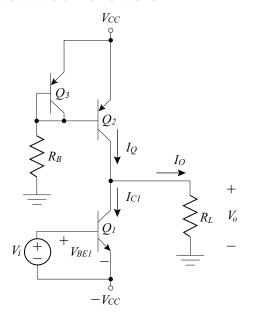

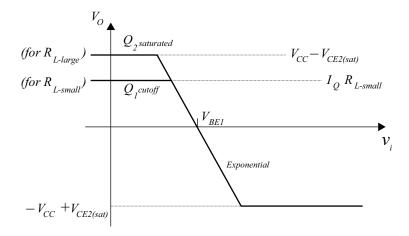

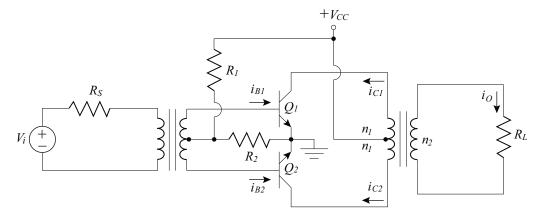

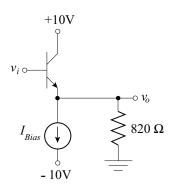

Multiple transistor amplifier circuitry is initially approached through cascading single transistor amplifiers using capacitive coupling. Only after the basic concepts are mastered, are the more complex circuits studied. Compound transistor configurations, such as the Darlington circuit, and direct-coupled amplifier stages are studied. As with single-transistor amplifiers, the previously observed linear region in ECL logic circuits leads to the study of emitter-coupled and source-coupled amplifiers. Common integrated circuit practices such as current source biasing and active loads are discussed.

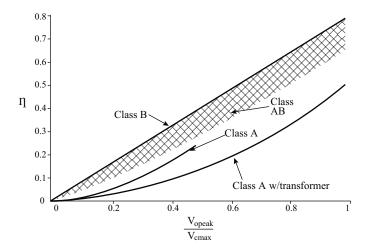

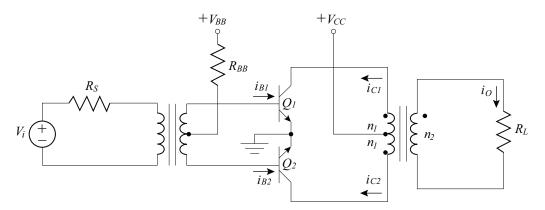

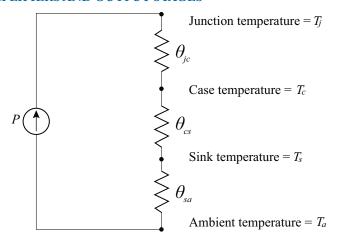

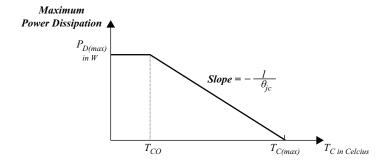

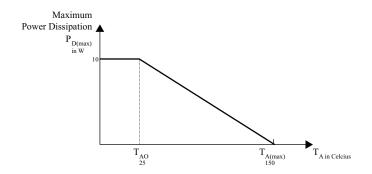

Power amplifiers provide a good counterexample to the use of small-signal analysis. By necessity, the output of a power amplifier is not small and consequently may contain distorted components. Both harmonic and intermodulation distortion analysis techniques are introduced and compared. Amplifier conversion efficiency is discussed for class A, B, and AB power amplifiers. Thermal considerations are presented using simple heat transfer models and are related to power amplifier design criteria and limitations.

Feedback principles are introduced initially as a technique to stabilize amplifier gain, reduce distortion, and control impedance. The various configurations are introduced and analyzed

#### xvi PREFACE

through two-port network analysis techniques. Improvement in frequency response is mentioned as an additional benefit but discussion is left for the next book in this series.

Thomas F. Schubert, Jr. and Ernest M. Kim October 2015

## Acknowledgments

In the development of any book, it seems that an infinite number of people provide and incalculable amount of guidance and help. While our thanks goes out to all those who helped, us, we can only mention a few of our many benefactors here. Special thanks go to Lynn Cox, who sparked our interest in writing an electronics text and, of course, to the staff at Morgan and Claypool Publishers, specifically Joe Claypool and Dr. C.L. Tondo.

Thomas F. Schubert, Jr. and Ernest M. Kim October 2015

## Single Transistor Amplifiers

Circuits containing single Bipolar Junction and Field Effect Transistors are capable of providing amplification in six basic configurations: three configurations for each type of transistor. In the common-emitter and common-collector configurations for BJTs, the input signal is injected at the base of the transistor: in the common-base configuration it is injected at the emitter. Similarly, FET configurations have the input injected in the gate for common-source and common-drain configurations, and at the source for the common-gate configuration. These six single-transistor configurations are basic building blocks of amplifier design.

The focus of attention in this chapter is on the significant performance characteristics of each amplifier configuration: the voltage gain, current gain, input resistance and output resistance. Each configuration has a unique set of performance characteristics that are dependent on the transistor characteristics as well as the configuration and value of surrounding circuit elements. This chapter primarily investigates discrete amplifiers where biasing is accomplished with voltage sources and resistances: later chapters will highlight BJT biasing with current sources as developed in Section 3.6 (Book 1). The performance of transistor amplifiers with current source biasing can be directly derived from the results presented in this chapter. The frequency range of interest is the socalled midband region: that range of frequencies below where the transistor characteristics begin to change with increasing frequency and above where any capacitive elements (many circuits have no capacitors and therefore the midband frequency range begins at DC) have significant effect on the circuit performance

Although amplifiers are usually comprised of more than one amplification stage, at least one of these six configurations is contained as an amplification stage in nearly every amplifier. The properties derived here form a solid foundation for the analysis and design of multistage amplifiers presented in later chapters.

#### 5.1 REVIEW OF TWO-PORT NETWORK BASICS

Electronic amplifiers are a subset of the system class commonly identified as *two-port networks*. In a two-port electronic network, signals are fed into a pair of terminals, amplified and/or modified by the system, and finally extracted at another pair of terminals. Each pair of terminals is identified as a port: signals are fed into an *input port* and extracted from an *output port*. The modeling and analysis of transistor-based amplifiers as well as feedback systems<sup>1</sup> is greatly simplified through the use of two-port network principles.

<sup>1</sup>The interconnection of two-port networks as used in the analysis of feedback amplifiers will be discussed in Chapter 8 (Book 2).

The items of interest in an electronic two-port network are the relationships between input port and output port voltages and currents. There are a few restrictions, upon which two-port analysis techniques are based, that must be identified:

- The network must be linear and time invariant.

- External connections may be made only to port terminals: no external connections can be made to any node internal to the port.

- All current entering one terminal of a port must exit the other terminal of that port.

- Sources and loads must be connected directly across the two terminals of a port.

Given the highly non-linear behavior of transistors, it may seem unusual to attempt to use two-port network analysis to describe transistor systems. It is possible, under small-signal conditions, however, to adequately model non-linear systems as *incrementally* linear. Electronic circuits previously discussed in this text have shown, along with non-linear operation, regions of linear operation. It is within these regions of linear operation that two-port analysis proves a particularly useful technique for the modeling of electronic systems.

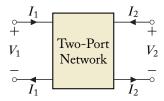

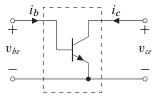

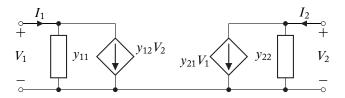

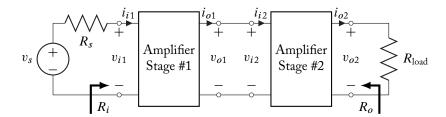

As with all electronic systems, it is important to define sign conventions: Figure 5.1 is a representation of a two-port network with appropriate voltage and current polarity definitions. As is standard in electronic systems, the voltage and current at each port obey the passive sign convention. Typically, the input port is identified as port #1 and the output port as port #2.<sup>2</sup>

Three-terminal devices, such as transistors, can also be modeled using two-port techniques. One terminal is selected as a common terminal: that terminal is extended to both of the ports and becomes the reference (negative) terminal to each port.

Figure 5.1: Two-port network sign conventions.

There are six basic sets of equivalent descriptive parameters for every two-port network:

1. Impedance parameters (z-parameters)—port voltages in terms of port currents.

<sup>&</sup>lt;sup>2</sup>The numbering of ports is not universal in acceptance. It does, however, allow for simple notation in the description of the parameters relating currents and voltages. In some electronic two-port descriptions of systems, the numbering system is replaced by a more descriptive identification of parameters. One common example of descriptive notation occurs in *b*-parameter modeling of Bipolar Junction Transistors as presented in Section 5.2.

- 2. Admittance parameters (y-parameters)—port currents in terms of port voltages.

- 3. Hybrid parameters (*h*-parameters)—input voltage and output current in terms of input current and output voltage.

- 4. Hybrid parameters (*g*-parameters)—input current and output voltage in terms of input voltage and output current.

- 5. Transmission parameters (*ABCD*-parameters)—input current and voltage in terms of output current and voltage.

- 6. Transmission parameters (*ABCD*-parameters)—output current and voltage in terms of input current and voltage.

The first four of these sets are of particular interest in the study of electronic feedback systems, set numbers three and four (hybrid parameters) are often used in the description of transistor properties, and the last two sets of parameters are particularly useful in the study of communication transmission systems. A short description of the first four two-port parameter set descriptions follows.

Impedance parameters (z-parameters) The independent variables for this set of parameters are the port currents and the dependent variables are the port voltages: voltage as a function of current is an impedance. It is most common to write the equations in matrix form:

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} z_{11} & z_{12} \\ z_{21} & z_{22} \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}. \tag{5.1}$$

The parameters  $\{z_{ij}\}$  are called the impedance (or z-) parameters of the network. For a linear, time-invariant network, the z-parameters can be obtained by performing simple tests on the network:

$$z_{ij} = \frac{V_i}{I_i} \big|_{I_{k \neq j} = 0} \ . \tag{5.2}$$

For a non-linear system that is operating in a region of linearity, a similar definition holds:

$$z_{ij} = \frac{\partial V_i}{\partial I_j} \Big|_{I_{k \neq j} = \text{Constant}} , \qquad (5.3)$$

where the constant value of  $I_k$  is taken near the midpoint of the region of linearity. If a quiescent (zero-input) point exists, the constant value of  $I_k$  is chosen as its quiescent value.

#### Example 5.1

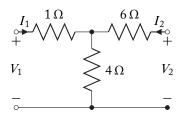

Determine the *z*-parameters for the given two-port network.

#### **Solution:**

The z-parameters are defined for this linear system as open-circuit parameters: one of the currents is always set to zero. Zero current implies an open circuit in the appropriate path. Thus:

$$z_{11}=1+4=5\,\Omega$$

(zero current in the 6  $\Omega$  resistor)

$z_{12}=4\,\Omega$  (no voltage drop across the 1  $\Omega$  resistor)

$z_{21}=4\,\Omega$  (no voltage drop across the 6  $\Omega$  resistor)

$z_{22}=6+4=10\,\Omega$  (zero current in the 1  $\Omega$  resistor)

Admittance parameters (y-parameters) Admittance parameters are defined with the independent variables are the port voltages and the dependent variables are the port currents: current as a function of voltage carries the units of admittance. The y-parameter equations are:

$$\begin{bmatrix} I_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} y_{11} & y_{12} \\ y_{21} & y_{22} \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}. \tag{5.4}$$

The parameters can be determined by performing the tests:

$$y_{ij} = \frac{I_i}{V_i} \left| V_{k \neq j} = 0 \right. \tag{5.5}$$

or

$$y_{ij} = \frac{\partial I_i}{\partial V_i} \left| V_{k \neq j} = \text{Constant} \right. \tag{5.6}$$

In a linear system the test for finding *y*-parameters indicates that a voltage must be set to zero: thus, the parameters are often called *short-circuit* admittance parameters.

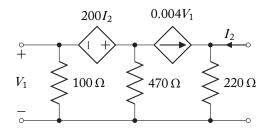

#### Example 5.2

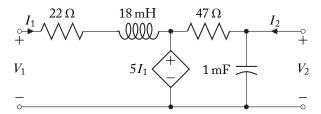

Determine the *y*-parameters for the network shown using standard phasor techniques, that is, find Y(s).

#### **Solution:**

It can be seen that this network is a linear system. Both two-port and phasor techniques are appropriate for such a system. The phasor equivalent impedance of the inductor and the capacitor are:

$$Z_L = 0.018 \,\mathrm{s}$$

$Z_C = 1000/\mathrm{s}$ .

The y-parameter tests for a linear system are given by Equation (5.5):

$$y_{ij} = \frac{I_i}{V_j} \left| V_{k \neq j} = 0 \right|.$$

In order to solve for  $y_{11}$  and  $y_{21}$ , the output terminals are short-circuited ( $V_2 = 0$ ). A loop equation can then be written around the remaining left loop:

$$V_1 - 22I_1 - 0.018 \,\mathrm{s}\, I_1 - 5I_1 = 0.$$

Which leads to:

$$y_{11} = \frac{I_1}{V_1} \bigg|_{V_2 = 0} = \frac{1}{27 + 0.018 \,\mathrm{s}}.$$

Since the capacitor has been shorted out by setting  $V_2 = 0$ , a loop equation can be written around the remaining right loop:

$$5I_1 + 47I_2 = 0 \implies I_2 = -0.1064I_1$$

and

$$y_{21} = \frac{I_2}{V_1} \bigg|_{V_2 = 0} = \frac{1}{253 + 0.1692 \,\mathrm{s}}.$$

The other two parameters,  $y_{12}$  and  $y_{22}$ , are obtained by shorting the input terminal ( $V_1 = 0$ ). A loop equation around the left loop of this configuration yields:

$$22I_1 + 0.018 \,\mathrm{s} I_1 - 5I_1 = 0 \quad \Rightarrow \quad I_1 = 0.$$

Obviously

$$y_{12} = \left. \frac{I_1}{V_2} \right|_{V_1 = 0} = 0.$$

With  $I_1 = 0$ , the current  $I_2$  is the sum of the currents in the 47  $\Omega$  resistor and the capacitor (the dependent voltage source has zero value):

$$y_{22} = \frac{I_2}{V_2}\Big|_{V_1 = 0} = y_{47\Omega} + y_{1 \text{ mF}} = 0.02128 + 0.001 \text{ s}.$$

The  $\gamma$ -parameter matrix is then given by:

$$Y(s) = \begin{bmatrix} \frac{1}{27 + 0.018 \,\mathrm{s}} & 0\\ \frac{1}{253 + 0.1692 \,\mathrm{s}} & 0.02128 + 0.001 \,\mathrm{s} \end{bmatrix}.$$

Hybrid parameters (h-parameters) The independent variables are the input voltage and output current; the dependent variables are the input current and output voltage.

$$\begin{bmatrix} V_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} h_{11} & h_{12} \\ h_{21} & h_{22} \end{bmatrix} \begin{bmatrix} I_1 \\ V_2 \end{bmatrix}. \tag{5.7}$$

Notice that these parameters, unlike the z- and y-parameters, do not all have the same dimensions. Each is different:  $h_{11}$  is the input port impedance;  $h_{12}$  is a dimensionless (input over output) voltage ratio;  $h_{21}$  is a dimensionless (output over input) current ratio; and  $h_{22}$  is output port admittance.

The parameters can be determined by performing the tests:

$$h_{11} = \frac{V_1}{I_1} \Big|_{V_2 = 0} \qquad h_{12} = \frac{V_1}{V_2} \Big|_{I_1 = 0}$$

$$h_{21} = \frac{I_2}{I_1} \Big|_{V_2 = 0} \qquad h_{22} = \frac{I_2}{V_2} \Big|_{I_1 = 0}$$

(5.8)

or

$$h_{11} = \frac{\partial V_1}{\partial I_1} \Big|_{V_2 = \text{Constant}} \qquad h_{12} = \frac{\partial V_1}{\partial V_2} \Big|_{I_1 = \text{Constant}}$$

$$h_{21} = \frac{\partial I_2}{\partial I_1} \Big|_{V_2 = \text{Constant}} \qquad h_{22} = \frac{\partial I_2}{\partial V_2} \Big|_{I_1 = \text{Constant}}.$$

$$(5.9)$$

Hybrid parameters (g-parameters) The independent variables are the input current and output voltage; the dependent variables are the input voltage and output current.

$$\begin{bmatrix} I_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} g_{11} & g_{12} \\ g_{21} & g_{22} \end{bmatrix} \begin{bmatrix} V_1 \\ I_2 \end{bmatrix}. \tag{5.10}$$

Notice that these parameters, like the b-parameters, do not all have the same dimensions. Each is different:  $g_{11}$  is the input port admittance;  $g_{12}$  is a dimensionless (input over output) current ratio;  $g_{21}$  is a dimensionless (output over input) voltage ratio; and  $g_{22}$  is output port impedance.

The parameters can be determined by performing the tests:

$$g_{11} = \frac{I_1}{V_1} \Big|_{I_2=0} \qquad g_{12} = \frac{I_1}{I_2} \Big|_{V_1=0}$$

$$g_{21} = \frac{V_2}{V_1} \Big|_{I_2=0} \qquad g_{22} = \frac{V_2}{I_2} \Big|_{V_1=0}$$

(5.11)

or

$$g_{11} = \frac{\partial I_1}{\partial V_1} \Big|_{I_2 = \text{Constant}} \qquad g_{12} = \frac{\partial I_1}{\partial I_2} \Big|_{V_1 = \text{Constant}}$$

$$g_{21} = \frac{\partial V_2}{\partial V_1} \Big|_{I_2 = \text{Constant}} \qquad g_{22} = \frac{\partial V_2}{\partial I_2} \Big|_{V_1 = \text{Constant}}.$$

(5.12)

#### CIRCUIT REPRESENTATION OF A TWO-PORT NETWORK 5.1.1

It is often important to create a simple equivalent circuit for a two-port network where the network parameters are known. While there are several techniques for the creation of these equivalent networks, the most useful in electronic applications involves Thévenin and Norton input and output realizations. In general, network parameters are replaced by simple circuit elements as shown in Table 5.1. Relationships between currents and voltages at the same port are treated as impedances or admittances, while relationships at different ports are treated as dependent sources.

**Table 5.1:** Two-port network replacement circuit elements for network parameters

| Network Parameter | Replacement Circuit Element |                                   |  |

|-------------------|-----------------------------|-----------------------------------|--|

|                   | Same Port                   | Opposite Port                     |  |

| impedance         | impedance                   | current-controlled voltage source |  |

| admittance        | admittance                  | voltage-controlled current source |  |

| current ratio     | (not applicable)            | current-controlled current source |  |

| voltage ratio     | (not applicable)            | voltage-controlled voltage source |  |

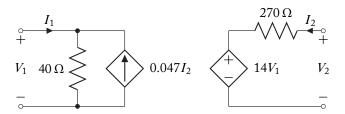

#### Example 5.3

A two-port network has been found to have the following *g*-parameters:

$$g_{11} = 0.025 \,\mathrm{S}$$

$g_{12} = 47 \,\mathrm{mA/A}$

$g_{21} = 14 \,\mathrm{V/V}$   $g_{22} = 270 \,\Omega$ .

Determine an equivalent circuit representation of the two-port network.

#### **Solution:**

The matrix equation for the *g*-parameter representation of a two-port network can be written as two separate equations:

$$I_1 = g_{11}V_1 + g_{21}I_2$$

and  $V_2 = g_{21}V_1 + g_{22}I_2$ .

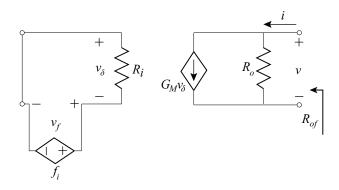

The equation for  $I_1$  reveals that two currents must be added together to make the input port current. Referring to Table 5.1, one finds that the currents emanate from an admittance and a current-controlled current source: they must be connected as a Norton source. The equation for  $V_2$  implies that two voltages must be added together. Table 5.1 shows the elements are an impedance and a voltage-controlled voltage source: they are connected in Thévenin fashion. The equivalent circuit representation is shown in Figure 5.2 (Note: for clarity,  $g_{11}$  is shown as a resistance rather than a conductance).

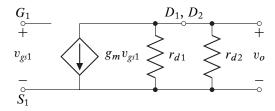

**Figure 5.2:** Two-port realization of Example 5.3.

#### 5.2 BJT LOW-FREQUENCY MODELS

In previous sections it has been shown that the Ebers-Moll model is an effective model in all regions of Bipolar Junction Transistor operation. It has also been shown that for large-signal behavior, a simplified set of models can bring additional insight into the operation of an electronic circuit. These models are first-order approximations to BJT operation, and exhibit some degree of error. When a BJT is operating in the forward-active region, it is appropriate to improve the modeling of its operation with a second-order approximation. As in most series approximations to behavior, second-order effects are a linearization, about the first-order (in this case, the quiescent) behavior, and are therefore added to the first-order behavior.

In the case of BJT operation, small-signal (often called AC) variations are linearized approximates to the operation of a transistor about its large-signal (often called DC or quiescent) behavior. Previous discussions of Bipolar Junction Transistors<sup>3</sup> have shown that the forward-active region (and, similarly, the inverse-active region) of BJT operation are approximately linear

<sup>&</sup>lt;sup>3</sup>See Section 3.5 (Book 1)—Digital Applications. In particular, discussions of the transfer relationship for the logic inverter and ECL logic OR gate showed a linear transition region between the two logic levels. These transition regions occurred when the BJT was operating in the forward-active region in transition between the cut-off and saturation regions.

in nature. It is therefore quite reasonable to assume that small-signal approximations have great validity in the modeling of BJT operation. The small-signal approximations are made in the form of approximate models that take the form of two-port networks. Two-port network characterizations are valid for non-linear systems that have regions of linearity: the BJT operating in either of its active regions is such a system.

The first obvious problem in modeling a BJT as a two-port is that there are only three terminals rather than the four that seem to be necessary. This obstacle is overcome by assigning one BJT terminal common to both ports. Practice has made two possibilities for this common terminal standard: either the emitter or the base are chosen to be the common terminal. In Figure 5.3, an *npn* BJT is shown as a two-port network with the emitter terminal chosen as common. In Chapter 3 (Book 1), it was shown that the major controlling port of a BJT is the base-emitter junction. Thus, the port containing the base-emitter junction is considered the input port and the remaining port (which contains the collector terminal and the common terminal), the output port. Since the terminal voltages and currents for BJTs have previously been identified with subscripts that are descriptive rather than the general numerical form of Section 5.1, the descriptive subscripts will be continued in the BJT two-port representation.

Figure 5.3: A bipolar junction transistor as a two-port network (emitter as common terminal).

The modeling process for transistor circuit performance is:

- 1. Model the BJT with an appropriate DC model.

- 2. Determine the circuit quiescent (DC) conditions—verify BJT active region.

- 3. Determine the BJT AC model parameters from the quiescent conditions.

- 4. Create an AC equivalent circuit.

- 5. Determine the circuit AC performance by:

- (a) replacing the BJT by its AC model, or

- (b) using previously derived results for the circuit topology.

- 6. Add the results of the DC and AC analysis to obtain total circuit performance.

Techniques for the DC modeling of BJTs and the determination of quiescent conditions have been discussed thoroughly in Chapter 3 (Book 1): discussions of AC modeling follow. The steps relating to circuit performance are discussed in later sections of this chapter.

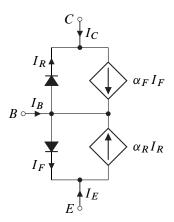

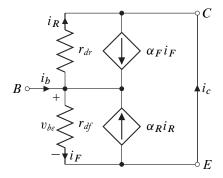

The choice of which set of two-port parameters will be most helpful in the modeling of a BJT is important. One good starting point is the Ebers-Moll model. The Ebers-Moll model for an *npn* BJT is shown in Figure 5.4.

**Figure 5.4:** The Ebers-Moll model of an *npn* BJT.

In the forward-active region of operation, the base-emitter junction is forward-biased and the base-collector junction is reverse biased. Approximate models<sup>4</sup> for forward-biased and reverse-biased diodes lead to the base-collector junction diode taking on the appearance of a very large resistance, while the base-emitter junction diode can be linearized about the quiescent point to a much smaller resistance. The forward current source (described by  $\alpha_F$ ) remains significant while the reverse current source supplies very little current. This small-signal model is shown in Figure 5.5, with the two junction dynamic resistances defined as:

$r_{df}$  = base-emitter diode forward dynamic resistance,

$r_{dr}$  = base-collector diode dynamic reverse resistance.

The dynamic resistance of a junction was derived in Chapter 2 (Book 1) to be:

$$r_d = \frac{\partial V}{\partial I} = \frac{\eta V_t}{I_s + I} = \frac{\eta V_t}{I_s} e^{-\frac{V}{\eta V_t}}.$$

(5.13)

The forward-biased value of this dynamic resistance is strongly dependent on the quiescent conditions, while the reverse-biased value is, in an active-region BJT, not. Thus,  $r_{df}$  is strongly de-

<sup>&</sup>lt;sup>4</sup>Models of a diode were derived in Chapter 2 (Book 1). The forward-biased biased model also includes a DC voltage source. The presence of that DC voltage source only affects quiescent behavior and not small signal (AC) behavior. For that reason it is eliminated in these discussions.

pendent on the quiescent conditions while  $r_{dr}$ , a much larger value, is not. While the derivation of this small-signal model was based on the Ebers-Moll model of an npn BJT, the small-signal model itself is valid for both npn and pnp BJTs. Reversing the direction of the junctions only changes quiescent conditions, it does not change the expressions for dynamic resistance.

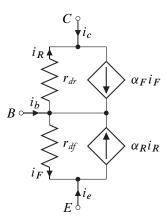

The analysis of electronic systems could be implemented using the model of Figure 5.5, however two-port techniques simplify many aspects of analysis. The two-port realization of

**Figure 5.5:** A forward-active small-signal model of a BJT.

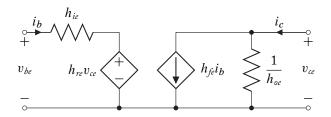

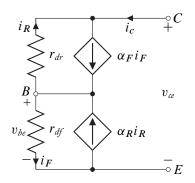

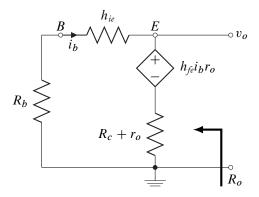

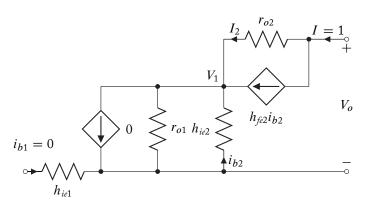

such a system would most effectively be accomplished by an *b*-parameter representation. This h-parameter realization is a common representation for small-signal, low-frequency BJT operation.<sup>5</sup> Figure 5.6 shows the *h*-parameter realization of a small-signal model of a BJT.

**Figure 5.6:** The common-emitter h-parameter model for a BJT.

$<sup>^5</sup>$ Other possible models include the T-model and the hybrid- $\pi$  model. The h-parameter model is chosen as an introductory small-signal model for its simplicity. The hybrid-π model will be introduced in Chapter 10 (Book 3) where its added complexity is necessary to adequately describe frequency-dependent effects.

The governing equations<sup>6</sup> for the *b*-parameter model are:

$$v_{be} = h_{ie}i_b + h_{re}v_{ce} \tag{5.14a}$$

and

$$i_c = h_{fe}i_b + h_{oe}v_{ce} \tag{5.14b}$$

where descriptive subscripts have been chosen for the subscripts of the *h*-parameters. The second subscript defines which terminal is chosen as common (either the base or the emitter), and the first subscript identifies the function of the parameter:

$h_{ie}$  = input impedance—emitter as common terminal

$h_{re}$  = reverse voltage gain—emitter as common terminal

$h_{fe} =$ forward current gain—emitter as common terminal

$h_{oe}$  = output admittance—emitter as common terminal.

The parameters<sup>7</sup> can be found as:

$$h_{ie} = \frac{\partial V_{BE}}{\partial I_b} \bigg|_{V_{CE} = V_{CEq}} \qquad h_{re} = \frac{\partial V_{BE}}{\partial V_{CE}} \bigg|_{I_B = I_{Bq}}$$

$$h_{fe} = \frac{\partial I_C}{\partial I_B} \bigg|_{V_{CE} = V_{CEq}} \qquad h_{oe} = \frac{\partial I_C}{\partial V_{CE}} \bigg|_{I_B = I_{Bq}}.$$

(5.15)

Equations (5.15) can be revised using AC voltages and currents. Realizing that AC signals are variations about the quiescent point and that constant values have zero AC component, the h-parameters can also be defined as:

$$h_{ie} = \frac{v_{be}}{i_b} \Big|_{v_{ce} = 0} \qquad h_{re} = \frac{v_{be}}{v_{ce}} \Big|_{i_b = 0}$$

$$h_{fe} = \frac{i_c}{i_b} \Big|_{v_{ce} = 0} \qquad h_{oe} = \frac{i_c}{v_{ce}} \Big|_{i_b = 0}.$$

(5.16)

All the signals in Equation (5.16) are AC signals. Setting an AC signal (i.e.,  $i_b$  or  $v_{ce}$ ) to zero holds the AC variation of that signal to zero, it does not change the quiescent conditions of the BIT.

Determination of the small-signal BJT h-parameters is accomplished by applying Equations (5.16) to the circuit of Figure 5.5.

<sup>&</sup>lt;sup>6</sup>Small letters with small subscripts indicate that these parameters are AC (or small-signal) parameters. They are a linearization of the transistor characteristics about a quiescent point and therefore depend on that quiescent point.

<sup>&</sup>lt;sup>7</sup>The final subscript "q" indicates the quiescent value of the circuit parameter. Thus,  $I_{Bq}$  and  $V_{CEq}$  are the quiescent (DC) values of the base current and the collector-emitter voltage for the transistor.

#### **5.2.1 DETERMINATION OF** $h_{ie}$ **AND** $h_{fe}$

The determination of these two parameters necessitates that the collector and emitter terminals be shorted, according to the requirements of Equation (5.16), in an AC sense. A DC quiescent current flows the quiescent collector-emitter voltage is greater than  $V_{CE(sat)}$  and the BJT is in the forward-active region.

The small-signal ratios can be obtained by applying Kirchhoff's current law applied at the base node:

$$i_b = i_F (1 - \alpha_F) + i_R (1 - \alpha_R),$$

(5.17)

where

$$i_F = \frac{v_{be}}{r_{df}}$$

and  $i_R = \frac{v_{be}}{r_{dr}}$ . (5.18)

The relationships of (5.18) inserted into Equation (5.17) yield:

$$i_b = \frac{v_{be}}{r_{df}} (1 - \alpha_F) + \frac{v_{be}}{r_{dr}} (1 - \alpha_R).$$

(5.19)

Equation (5.19) directly leads to the first of the *b*-parameters. The relative size of the forward and reverse dynamic resistances of the junctions,  $r_{dr} \gg r_{df}$ , leads to a simplified expression for  $h_{ie}$ :

$$h_{ie} = \frac{v_{be}}{i_b} = \left(\frac{r_{df}}{1 - \alpha_F}\right) / / \left(\frac{r_{dr}}{1 - \alpha_R}\right) \approx \frac{r_{df}}{1 - \alpha_F} = (\beta_F + 1) r_{df}. \tag{5.20}$$

The value for  $h_{ie}$  is dependent on  $r_{df}$ , a quantity that strongly depends on the quiescent conditions:  $h_{ie}$  must also strongly depend on quiescent conditions. Equation (5.13) can be used to obtain and expression for  $h_{ie}$  in terms of the quiescent collector current and  $\eta V_t \approx 26 \,\mathrm{mV}$ :

$$h_{ie} \approx (\beta_F + 1) \frac{\eta V_t}{I + I_S} \approx (\beta_F + 1) \frac{\eta V_t}{|I_C|}.$$

(5.21)

An additional equation must be written to find  $h_{fe}$ . At the collector node Kirchhoff's Current Law gives:

$$i_c = \alpha_F i_F - i_R = \alpha_F \frac{v_{be}}{r_{df}} - \frac{v_{be}}{r_{dr}},$$

(5.22)

which, noting the relative dynamic resistance sizes, can be reduced to

$$\frac{v_{be}}{i_c} = \left(\frac{r_{df}}{\alpha_F} / / r_{dr}\right) \approx \frac{r_{df}}{\alpha_F}.$$

(5.23)

The required current ratio for  $h_{fe}$  is found using Equations (5.20) and (5.23):

$$h_{fe} = \frac{i_c}{i_b} \approx \frac{\frac{\alpha_F}{r_{df}}}{\frac{(1 - \alpha_F)}{r_{df}}} = \beta_F.$$

(5.24)

#### **5.2.2 DETERMINATION OF** $h_{re}$ **AND** $h_{oe}$

The tests for these two *b*-parameters (as seen in Equation (5.16)) require that the small-signal base current be set to zero. Again, remember that there is still a quiescent (DC) current flowing and the BJT is in the forward-active region. Kirchhoff's Current Law applied at the base node yields:

$$i_F(1 - \alpha_F) + i_R(1 - \alpha_R) = 0,$$

(5.25)

where,

$$i_F = \frac{v_{be}}{r_{df}}$$

and  $i_R = \frac{v_{be} - v_{ce}}{r_{dr}}$ . (5.26)

Then inserting (5.26) into (5.25) yields

$$\frac{v_{be}}{r_{df}}(1 - \alpha_F) + \frac{v_{be} - v_{ce}}{r_{dr}}(1 - \alpha_R) = 0, \tag{5.27}$$

or

$$v_{be}\left(\frac{1-\alpha_F}{r_{df}} + \frac{1-\alpha_R}{r_{dr}}\right) = v_{ce}\left(\frac{1-\alpha_R}{r_{dr}}\right). \tag{5.28}$$

The required voltage ratio can now be determined as:

$$h_{re} = \frac{v_{be}}{v_{ce}} = \frac{\left(\frac{r_{df}}{1 - \alpha_F} / / \frac{r_{dr}}{1 - \alpha_R}\right)}{\frac{r_{dr}}{1 - \alpha_R}} \approx \frac{r_{df}}{r_{dr}} \left(\frac{1 - \alpha_R}{1 - \alpha_F}\right) = \frac{r_{df}}{r_{dr}} \left(\frac{1 + \beta_F}{1 + \beta_R}\right). \tag{5.29}$$

The value for  $h_{re}$  is seen to be a *very* small quantity and can safely be assumed to be zero in the modeling of a BJT in either active region. In order to solve for  $h_{oe}$ , Kirchhoff's Current Law is applied at the emitter node:

$$i_c = i_F - \alpha_R i_R = \frac{v_{be}}{r_{df}} - \alpha_F \frac{v_{be} - v_{ce}}{r_{dr}} = v_{be} \left( \frac{1}{r_{df}} - \frac{\alpha_F}{r_{dr}} \right) + \frac{v_{ce}}{r_{dr}}.$$

(5.30)

Again using the property that  $r_{df} \ll r_{dr}$ , a simplification can be made

$$i_c \approx \frac{v_{be}}{r_{df}} + \frac{v_{ce}}{r_{dr}}. ag{5.31}$$

Equation (5.29) can be used to eliminate  $v_{be}$  from Equation (5.31):

$$i_c \approx \frac{v_{ce}}{r_{df}} \frac{r_{df}}{r_{dr}} \left( \frac{1 - \alpha_R}{1 - \alpha_F} \right) + \frac{v_{ce}}{r_{dr}} = \frac{v_{ce}}{r_{dr}} \left( \frac{1 + \beta_F}{1 + \beta_R} + 1 \right).$$

(5.32)

The relationship for  $h_{oe}$  is obtained from Equation (5.32):

$$h_{oe} = \frac{i_c}{v_{ce}} \approx \frac{1}{r_{dr}} \left( \frac{1 + \beta_F}{1 + \beta_R} + 1 \right).$$

(5.33)

This is a very small output conductance (the equivalent of a very large output resistance). The simplified expression of Equation (5.33) does not adequately model all the resistances contributing to output resistance for a real BJT. The actual output resistance is much smaller that is predicted by the Ebers-Moll model. A more accurate predictor of the output resistance,  $r_o$ , is defined in terms of another quantity, the early voltage,  $V_A$ .

$$\frac{1}{h_{oe}} = r_o = \left| \frac{V_A}{I_C} \right|. \tag{5.34}$$

<sup>&</sup>lt;sup>8</sup>The early voltage is a parameter that describes the change in the width of the base region of a BJT which results from a change in base-collector junction voltage. A basic description of the effect can be found in most solid state electronics texts, but is beyond the scope of this text.

The early voltage for a BJT is usually determined experimentally by observing the slope of the  $I_C$  vs.  $V_{CE}$  curves for a BJT in the forward-active region. It typically has a value of 100 V or more and is defined as:

$$V_A = \frac{I_C}{\frac{\partial I_C}{\partial V_{CE}}}. (5.35)$$

This output resistance is often large compared to the resistances connected to the collector-emitter port of the BJT and  $h_{oe}$  can, in that case, be assumed approximately equal to zero. When the external resistances are not small compared to the output resistance it is necessary to include  $h_{oe}$  in the model for the BJT.

The *h*-parameters for a BJT are summarized in Table 5.2. Only one parameter,  $h_{fe}$ , is essentially independent of quiescent conditions, while the other three parameters depend to varying degrees on the bias conditions, specifically on the quiescent collector current,  $I_C$ .

**Table 5.2:** BJT h-parameter summary

| h-Parameter  | Value                                                                                    |

|--------------|------------------------------------------------------------------------------------------|

| $h_{\it ie}$ | $\approx (\beta_F + 1) \frac{\eta V_t}{ I_C }$                                           |

| $h_{fe}$     | $pprox eta_F$                                                                            |

| $h_{re}$     | $\approx \frac{r_{df}}{r_{dr}} \left( \frac{1 + \beta_F}{1 + \beta_R} \right) \approx 0$ |

| $h_{oe}$     | $= \left  \frac{I_C}{V_A} \right  \approx 0$                                             |

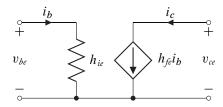

The extremely small values of  $h_{re}$  and  $h_{oe}$  lead to a simplified b-parameter model of a BJT where these two parameters are assumed to be approximately zero, as shown in Figure 5.7. When large resistances are connected to the collector-emitter port of the BJT it is important to reintroduce  $h_{oe}$  into the b-parameter model as a conductance shunting the dependent current source. In typical BJT applications,  $h_{re}$  is not significant.

**Figure 5.7:** Simplified small-signal *h*-parameter model for a BJT.

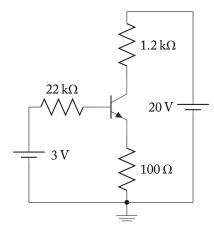

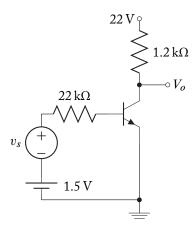

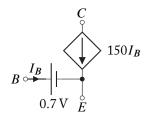

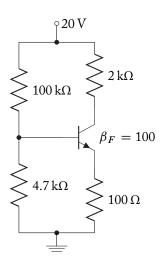

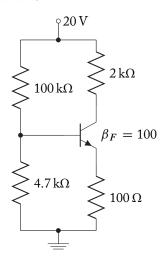

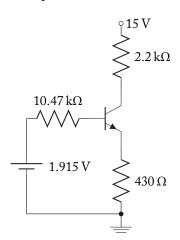

#### Example 5.4

Given a Silicon *npn* BJT with parameters:

$$\beta_F = 150$$

$V_A = 350 \,\text{V},$

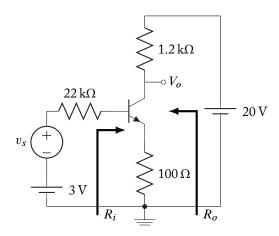

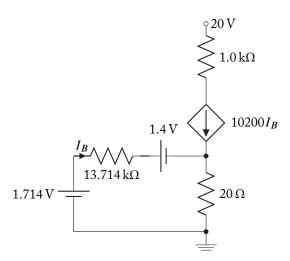

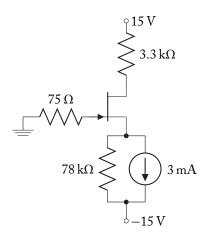

operating in the given circuit at room temperature. Determine an appropriate small-signal bparameter model for the BJT.

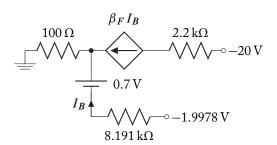

#### **Solution:**

The quiescent conditions must first be obtained: KCL taken around the base-emitter loop yields

$$3 - 22 kI_B - 0.7 - 100(151I_B) = 0$$

$I_B = 62.0 \,\mu\text{A}$  and  $I_C = 150I_B = 9.30 \,\text{mA}$ .

Checking to see if the BJT is in the forward-active region by using KCL around the collectoremitter loop yields:

$$V_{CE} = 20 - 1.2 \,\mathrm{k}I_C - 100 \left(\frac{151}{150}I_C\right) = 7.90 \,\mathrm{V}.$$

This value is greater than  $V_{CE(sat)}$ , which implies that the BJT is in the forward-active region and the *h*-parameter model parameters itemized in Table 5.2 may be used.

$$h_{fe} \approx \beta_F = 150$$

$$h_{ie} \approx (\beta_F + 1) \frac{\eta V_t}{|I_C|} = (151) \frac{26 \text{ mV}}{|9.30 \text{ mA}|} = 422 \Omega$$

$$h_{oe} = \left| \frac{I_C}{V_A} \right| = \left| \frac{9.30 \text{ mA}}{350 \text{ V}} \right| = 26.6 \,\mu\text{S} \approx 0$$

$$h_{re} \approx 0.$$

It is necessary to check to see if  $h_{oe}$  can be approximated as zero value. It is equivalent to a resistance,  $r_o$ , of 37.6 k $\Omega$  (the resistance is the inverse of  $h_{oe}$ ), which is large with respect to the 1.2 k $\Omega$  and 100  $\Omega$  resistors connected to the collector-emitter port of the BJT:  $h_{oe}$  can be assumed in this application to be approximately zero in value.

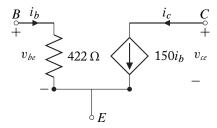

The approximate small-signal model of this BJT operating in this circuit is therefore found to be:

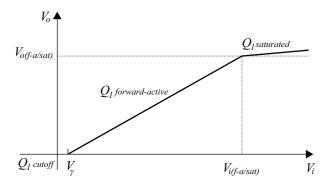

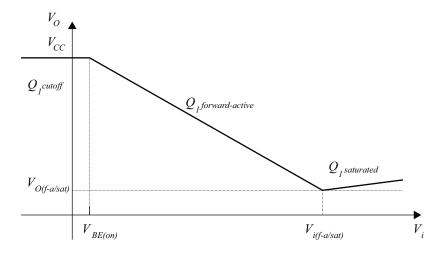

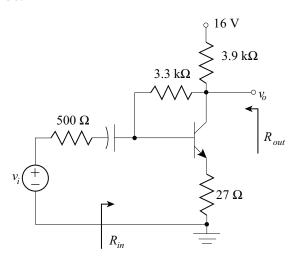

# 5.3 COMMON-EMITTER AMPLIFIERS

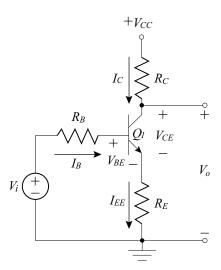

A description of the general performance of a common-emitter amplifier can be derived directly from the voltage transfer relationship of a BJT logic inverter. The BJT logic inverter, discussed in Section 3.5 (Book 1), has two distinct regions where the voltage output is relatively constant: when the BJT is in either the saturation or in cut-off region. Between these two regions lies a linear region where the variation in the output voltage about the quiescent point is directly proportional to the variation in the input voltage. This linear-region proportionality constant for the logic inverter was seen in Example 3.5-1 to be negative and greater than 1 in magnitude: the input signal variations were amplified and inverted. The discussions of Section 3.5 (Book 1) were based on coarse, first-order approximations of the operation of a BJT in each of its regions of operation. This section develops the characteristics of this type of amplifier (and its close relatives) using the second-order *b*-parameter approximations developed earlier in this chapter.

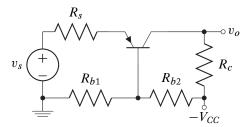

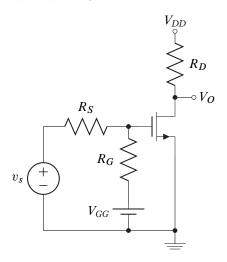

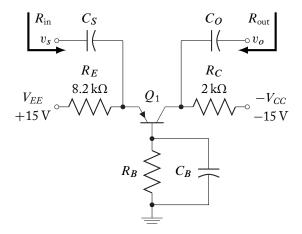

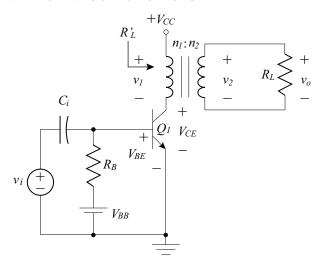

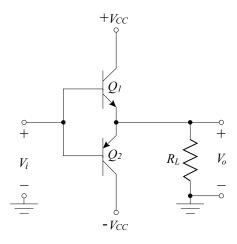

Common-emitter amplifiers have the same general circuit topology as the logic inverter:

- the input signal enters the BJT at the base,

- the output signal exits the BJT at the collector, and

- the emitter is connected to a constant voltage, often the ground (common) terminal, sometimes with an intervening resistor.

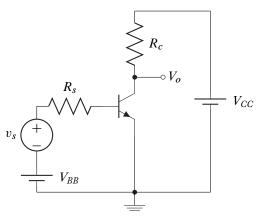

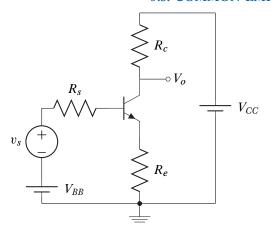

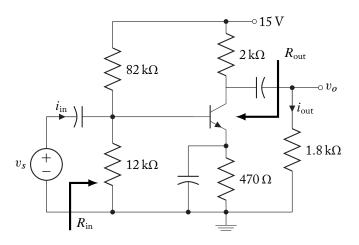

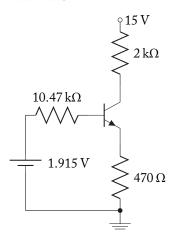

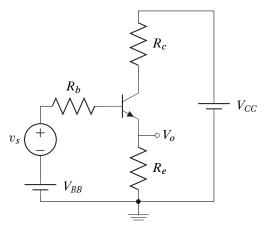

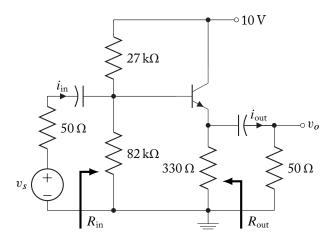

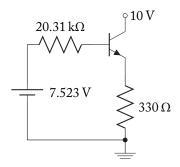

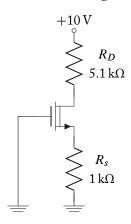

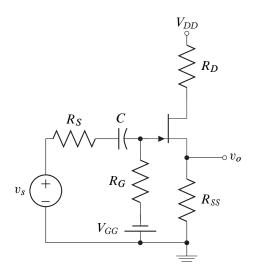

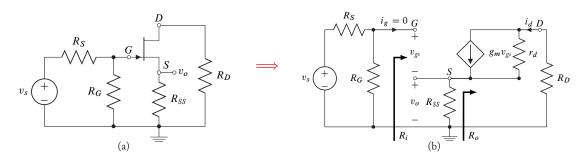

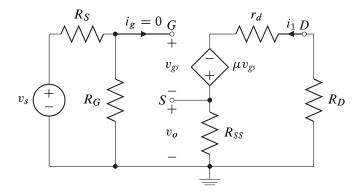

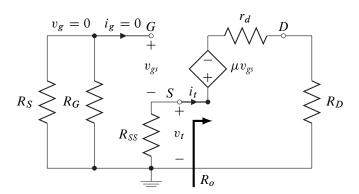

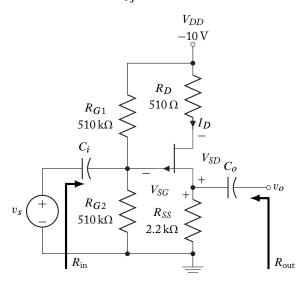

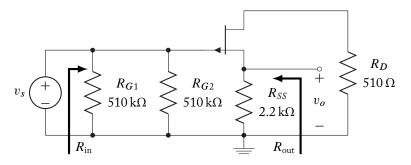

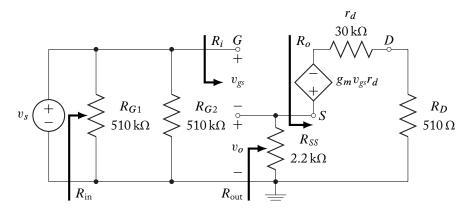

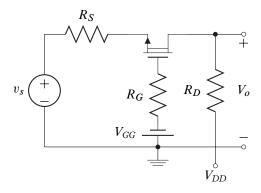

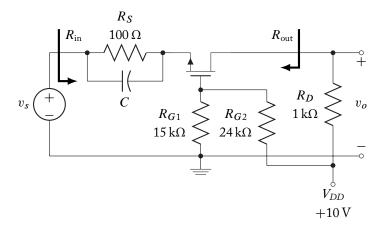

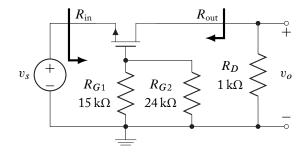

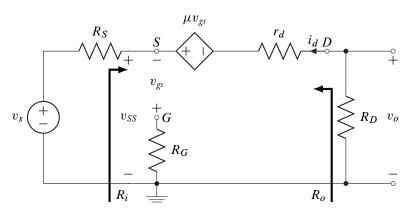

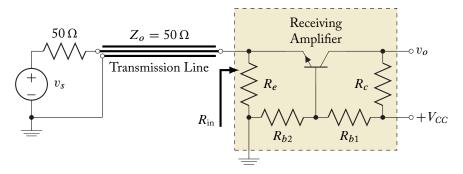

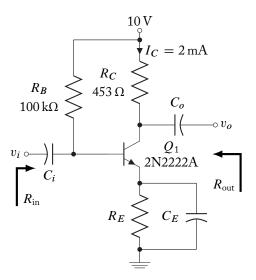

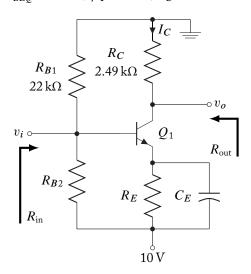

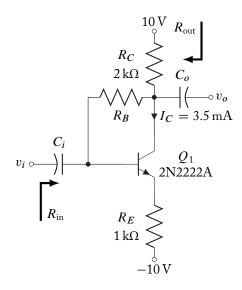

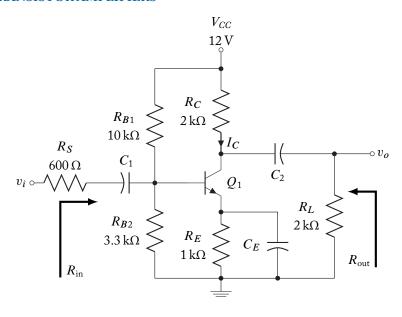

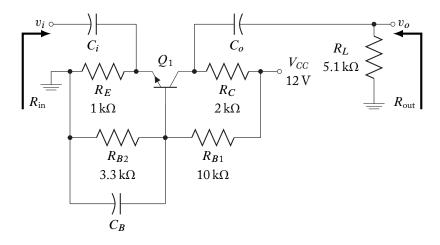

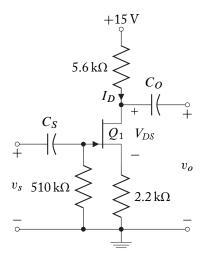

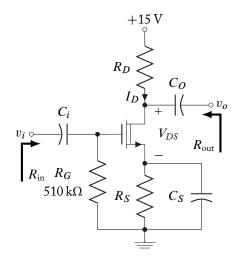

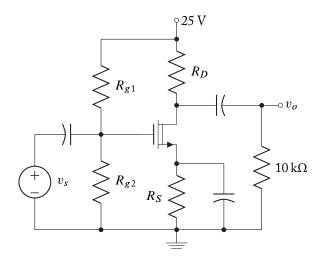

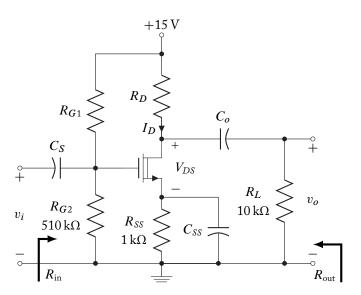

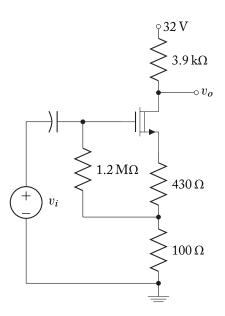

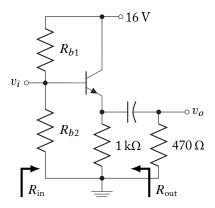

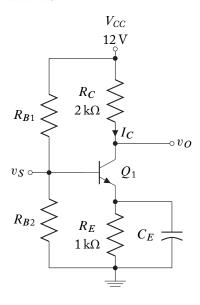

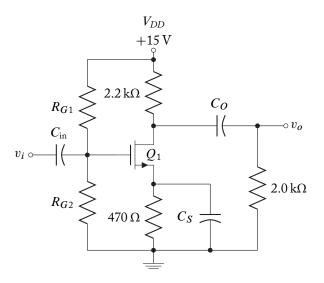

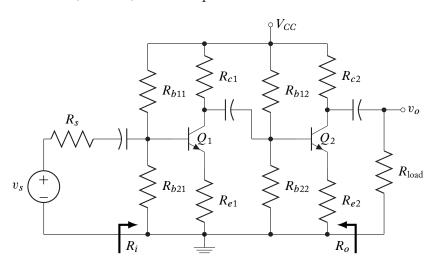

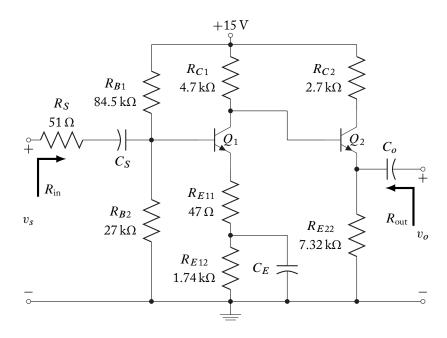

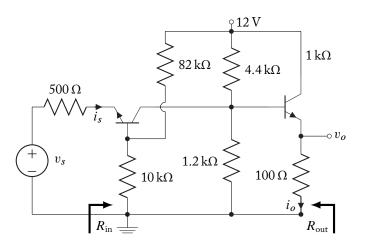

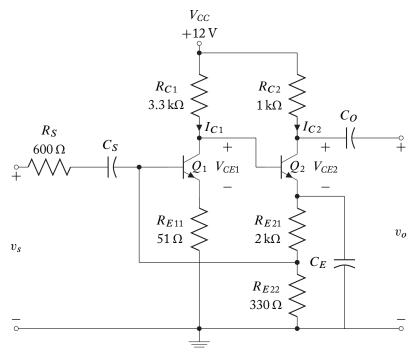

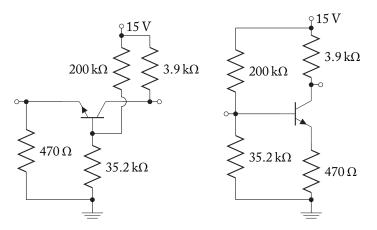

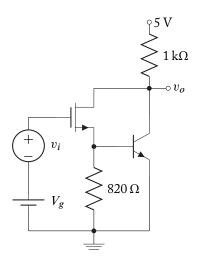

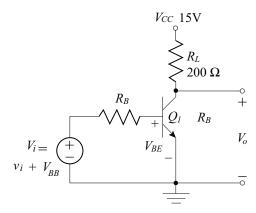

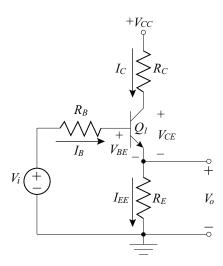

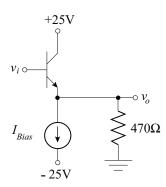

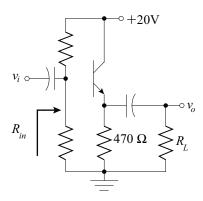

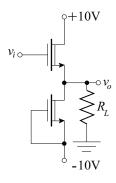

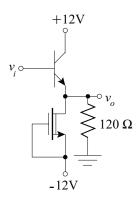

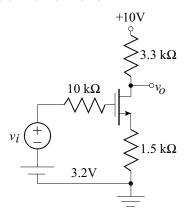

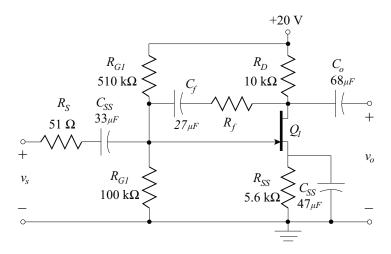

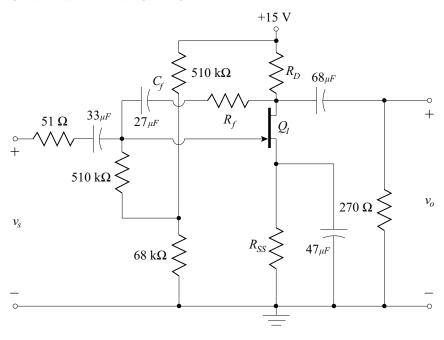

A simple common-emitter amplifier is shown in Figure 5.8. It is necessary that the quiescent point of the BJT be set with the circuitry external to the transistor so that it is in the forward-active region. The values of the resistors,  $R_c$  and  $R_s$ , and the DC voltage sources,  $V_{CC}$

Figure 5.8: A simple common-emitter amplifier.

and  $V_{BB}$ , have therefore been chosen so that the BJT is in the forward-active region and the circuit will operate as an amplifier. The voltage source,  $v_s$ , is a small-signal AC source.

Once the circuit quiescent ( $v_s = 0$ ) conditions have been calculated and it has been determined that the BJT is in the forward-active region of operation, the significant h-parameters can be calculated to form the small-signal model of the transistor:

$$h_{fe} = \beta_F$$

$h_{oe} = \frac{I_c}{V_A} \approx 0.$

$$h_{ie} = (\beta_F + 1) \left| \frac{\eta V_t}{I_C} \right|.$$

(5.36)

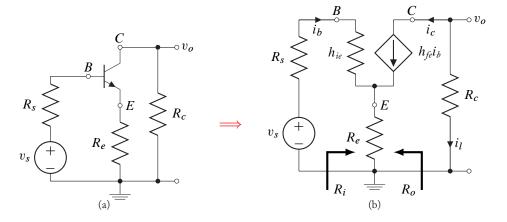

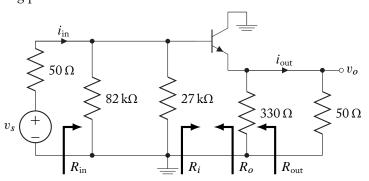

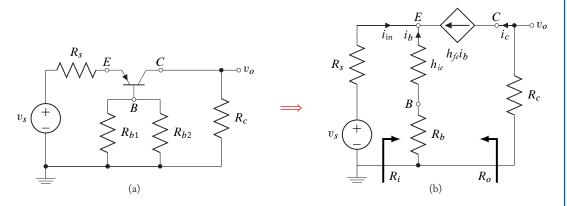

The small-signal (often called AC) circuit performance can now be calculated. Total circuit performance is the sum of quiescent and small-signal performance: the process is basically a superposition of the zero-frequency solution with the low-frequency AC solution. In each case, solutions are formed by setting the independent sources at all other frequencies to zero. AC circuit performance is obtained through analysis of a circuit obtained by setting the original circuit DC sources to zero, and then replacing the BJT with its *b*-parameter two-port model. This circuit reconfiguration process, applied to Figure 5.8, is shown in Figure 5.9.

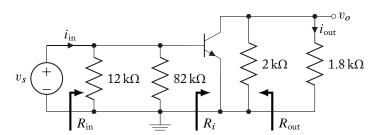

The small-signal performance characteristics<sup>10</sup> that are of interest in any amplifier are: the current gain, the input resistance, the voltage gain, and the output resistance. For the simple commonemitter amplifier under consideration, these characteristics can be obtained from analysis of the circuit of Figure 5.9b. Definitions for these quantities often vary due to differing definition of the exact location of the point of measurement. Care must always be taken to ensure that measurement points are clearly understood before any analysis begins.

<sup>&</sup>lt;sup>9</sup>At high frequencies the BJT performance characteristics change. See Book 3.

<sup>&</sup>lt;sup>10</sup>It should be remembered that the quantities discussed in this section and following sections are small-signal (or AC) quantities. The ratios considered here are the ratios of AC quantities not the ratios of total currents and/or voltages.

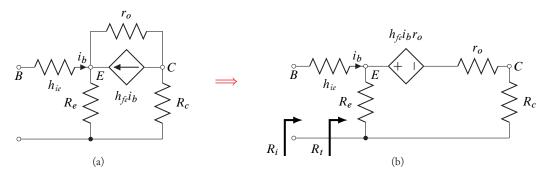

**Figure 5.9:** AC modelling of a simple common-emitter amplifier. (a) The small-signal circuit: DC sources set to zero; (b) BJT replaced by *h*-parameter model.

#### **Current Gain**

For this simple transistor amplifier, the current gain is defined as the ratio of load current to input current, that is:

$$A_I \equiv \frac{i_l}{i_b} = \frac{-i_c}{i_b}.\tag{5.37}$$

From the circuit of Figure 5.9b, it can easily be determined that the collector and base currents are related through the dependent current source by the constant  $h_{fe}$ . The current gain is dependent only on the BJT characteristics and independent of any other circuit element values. Its value is given by:

$$A_I = -h_{fe}, (5.38)$$

where the negative sign implies that the small-signal current input is inverted as well as amplified. If the resistor  $R_c$  is large then the output resistance of the BJT must be considered in calculating the current gain. Including  $h_{oe}$  in the BJT b-parameter model divides the output current between the output resistance,  $r_o = 1/h_{oe}$  and the collector resistance:

$$A_I = -h_{fe} \frac{r_o}{r_o + R_c}. (5.39)$$

#### **Input Resistance**

Input resistance is measure of the AC input current as a function of the input voltage. If the AC input voltage,  $v_b$ , is taken at the input terminal of the BJT (the base), the input resistance (shown if Figure 5.9b with the bold arrow and labeled as  $R_i$ ) is given by:

$$R_i \equiv \frac{v_b}{i_b} = h_{ie}. \tag{5.40}$$

The input resistance is unaffected by finite  $r_o$ .

#### Voltage Gain

The voltage gain is the ratio of output voltage to input voltage. If the input voltage is again taken to be the voltage at the input to the transistor,  $v_b$ , the voltage gain is defined as:

$$A_V \equiv \frac{v_o}{v_h}.\tag{5.41}$$

One of the best methods for obtaining this ratio is through the use of quantities already calculated or otherwise easily obtained:

$$A_V = \frac{v_o}{v_b} = \left(\frac{v_o}{i_l}\right) \left(\frac{i_l}{i_b}\right) \left(\frac{i_b}{v_b}\right). \tag{5.42}$$

The expressions for each quantity, when substituted into Equation (5.42), yield:

$$A_V = (R_c)(A_I)\left(\frac{1}{R_i}\right) = \frac{-h_{fe}R_c}{h_{ie}}.$$

(5.43)

Again, the small-signal output voltage is an inverted, amplified replica of the input voltage. The voltage gain can be very large in magnitude. Equation (5.43) indicates it is limited only by the BJT parameter  $h_{fe}$  and the external resistance  $R_c$ . That conclusion is based, however, on the assumption that  $R_c$  is small with respect to  $r_o$ . If  $R_c$  approaches the magnitude of  $r_o$ , the gain becomes limited by the output resistance of the amplifier, and  $R_c$  must be replaced by  $R_c//r_o$  in Equation (5.43).

Often the voltage gain from the source to the load is of interest as well. This overall voltage gain can be defined as:

$$A_{VS} \equiv \frac{v_o}{v_s}. (5.44)$$

This ratio can be directly derived from the simple voltage gain,  $A_V$ , with a voltage division using the amplifier input resistance and the source resistance:

$$A_{VS} = \frac{v_o}{v_s} = \left(\frac{v_o}{v_b}\right) \left(\frac{v_b}{v_s}\right) = A_V \left(\frac{R_i}{R_i + R_s}\right),\tag{5.45}$$

or

$$A_{VS} = \left(\frac{-h_{fe}R_c}{h_{ie}}\right) \left(\frac{h_{ie}}{h_{ie} + R_s}\right) = \frac{-h_{fe}R_c}{h_{ie} + R_s}.$$

(5.46)

Since  $A_{VS}$  is dependent on  $A_V$  it is also limited in magnitude by finite  $r_o$ . To include the effect of finite  $r_o$ ,  $R_c$  must be replaced by  $R_c//r_o$  in Equation (5.46).

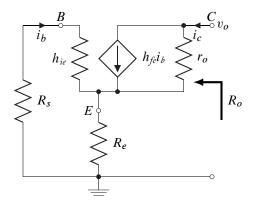

### **Output Resistance**

The output resistance is defined as the Thévenin resistance at the output of the amplifier (in this case the BJT collector) looking back into the amplifier. As in the case of voltage gain, the exact

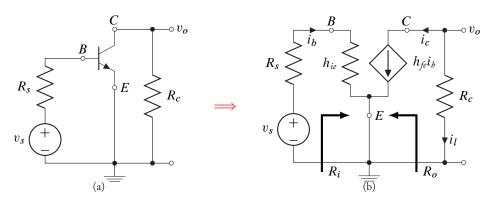

point of measurement is not always clear. The arrow in circuit diagram of Figure 5.9 indicates that  $R_o$  is to be measured without considering  $R_c$ : it is also possible to define an output resistance,  $R_{ol}$ , that includes the effects of collector resistance,  $R_c$ . The AC equivalent circuit used to calculate the output resistance is shown in Figure 5.10a. The input independent source is set to zero and the Thévenin resistance is calculated looking into the output. It can easily be seen that  $i_b = 0$  in this circuit. Kirchhoff's Voltage Law taken around the base loop gives:

$$i_b (h_{ie} + R_s) = 0 \qquad \Rightarrow \qquad i_b = 0.$$

**Figure 5.10:** Circuit for calculation of output resistance. (a) Small-signal output circuit: AC source set to zero; (b) More accurate BJT *h*-parameter model.

Zero base current implies that the dependent current source is also zero-valued and the output resistance becomes:

$$R_o \approx \infty.$$

(5.47)

While the output resistance is certainly large, a more revealing result could be obtained with a better model of the BJT. A more accurate h-parameter model of a BJT includes  $h_{oe}$  (as derived in Section 5.2). When this model is used to determine the output resistance of a simple common-emitter amplifier (see Figure 5.10b), the output resistance is given by:

$$R_o = r_o = \frac{1}{h_{oe}} = \left| \frac{V_A}{I_C} \right|. \tag{5.48}$$

The output resistance is therefore a large value which is dependent strongly on the quiescent conditions of the transistor.

As mentioned above, it is also possible to define output resistance of a common-emitter amplifier to include the collector resistor,  $R_c$ :

$$R_{ol} = R_o / / R_c \approx R_c. \tag{5.49}$$

The common-emitter amplifier has been shown to have:

- moderate input resistance,

- high output resistance,

- · high current gain, and

- · moderate to high voltage gain, depending on the presence and size of any resistance connected to the collector terminal.

A Summary of the common-emitter amplifier performance characteristics is found in Subsection 5.3.4.

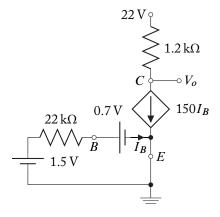

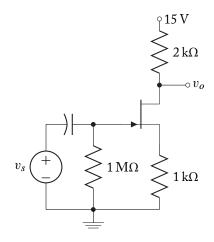

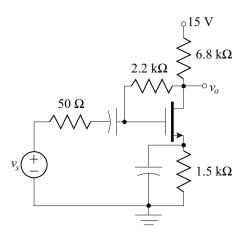

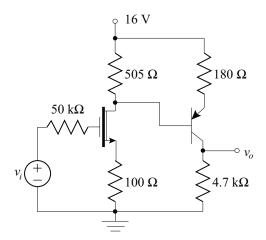

# Example 5.5

Given a Silicon *npn* BJT with parameters:

$$\beta_F = 150$$

$V_A = 350 \,\text{V},$

operating in the given circuit at room temperature.

Determine the amplifier small-signal performance characteristics.

### **Solution:**

The modeling process for transistor circuit performance was described in Section 5.2 to contain the following steps:

- 1. Model the BJT with an appropriate DC model.

- 2. Determine the circuit quiescent (DC) conditions—verify BJT active region.

- 3. Determine the BJT AC model parameters from the quiescent conditions.

- 4. Create an AC equivalent circuit.

- 5. Determine the circuit AC performance by:

- (a) replacing the BJT by its AC model, or

- (b) using previously derived results for the circuit topology.

- 6. Add the results of the DC and AC analysis to obtain total circuit performance.

Step #1 Model the BJT with an appropriate DC model. Hopefully, the BJT will be found to be in the forward-active region so that the circuit can operate as an amplifier. The DC forward-active model of the BJT is derived in Section 3.4 (Book 1), and shown below. The appropriate transistor quantities that must be used in this case are  $\beta_F = 150$  and  $V_{\gamma} = 0.7$  (Silicon BJT).

Step #2 Determine the circuit quiescent (DC) conditions—verify BJT active region.

The BJT model of step #1 replaces the BJT as shown. Quiescent conditions are then calculated. Around the base-emitter loop, Kirchhoff's Current Law yields:

$$1.5 - 22 k(I_B) - 0.7 = 0.$$

So that

$$I_B = 36.36 \,\mu\text{A}$$

and

$$I_C = 150I_B = 5.45 \,\mathrm{mA}.$$

Both currents are positive: only  $V_{CE}$  must be checked to see if it is larger than  $V_{CE(sat)} = 0.2 \text{ V}$ . Kirchhoff's Current Law applied to the collector-emitter loop yields:

$$V_{CE} = 22 - 1.2 \,\mathrm{k}(I_C) = 15.46 \,\mathrm{V}.$$

The transistor is in the forward-active region: the circuit will operate as an amplifier.

Step #3 Determine the BJT AC model parameters from the quiescent conditions. The relevant *b*-parameters are:

$$h_{fe} \approx \beta_F = 150$$

$h_{ie} \approx (\beta_F + 1) \frac{\eta V_t}{|I_C|} = (151) \frac{26 \text{ mV}}{|5.45 \text{ mA}|} = 720 \Omega$

$$h_{re} = 0$$

$h_{oe} = \left| \frac{I_C}{V_A} \right| = \left| \frac{5.45 \text{ mA}}{350 \text{ V}} \right| = 15.6 \,\mu\text{S} \approx 0.$

Step #4 Create an AC equivalent circuit.

The DC sources are set to zero and the output voltage becomes a small-signal quantity.

Step #5 Determine the circuit AC performance by:

- 1. replacing the BJT by its AC model, or

- 2. using previously derived results for the circuit topology.

In this case, it appears easiest to use previously derived results. The input resistance at the base of the BJT is given by:

$$R_i = h_{ie} = 720 \,\Omega$$

.

If the input resistance is measured to the left of the  $22 \text{ k}\Omega$  resistor then:

$$R_i' = 22 \,\mathrm{k}\Omega + 720 \,\Omega = 22.7 \,\mathrm{k}\Omega.$$

The current gain is given by:

$$A_I = -h_{fe} = -150.$$

The voltage gain from the base of the BJT is given by:

$$A_V = \frac{-h_{fe}R_c}{h_{ie}} = \frac{-150(1.2 \,\mathrm{k})}{720} = -250.$$

The voltage gain from the source is given by:

$$A_{VS} = \frac{-h_{fe}R_c}{h_{ie} + R_s} = \frac{-150(1.2 \text{ k})}{720 + 22 \text{ k}} = -7.92.$$

The output resistance is given by:

$$R_o = \frac{1}{h_{os}} = 64.17 \,\mathrm{k}\Omega.$$

If the collector resistance is included in the output resistance,

$$R_{ol} = R_o / / R_c = \frac{(64.17 \,\mathrm{k})(1.2 \,\mathrm{k})}{64.17 \,\mathrm{k} + 1.2 \,\mathrm{k}} = 1.18 \,\mathrm{k}\Omega.$$

Step #6 is beyond the requirements of this problem, but all the data is present to add the quiescent solution to the small-signal solution for total circuit response.

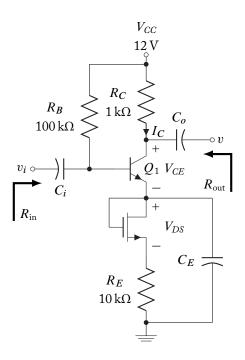

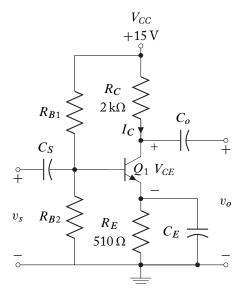

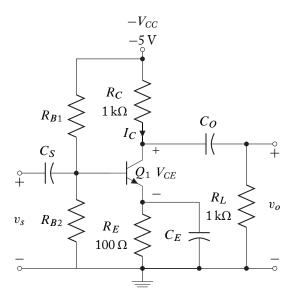

# 5.3.1 COMMON-EMITTER AMPLIFIERS WITH NON-ZERO EMITTER RESISTANCE

Several of the characteristics of a common-emitter amplifier can be altered through the addition of a resistor connected between the emitter and ground.

It has previously been shown in Section 3.7 (Book 1) that the addition of such a resistor greatly improves bias stability due to BJT variations. The addition of an emitter resistor has the following effects on common-emitter amplifiers:

- increased input resistance,

- increased output resistance,

- · decreased voltage gain, and

- · unchanged current gain.

Derivation of these effects follows the process described in Section 5.2.

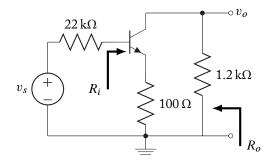

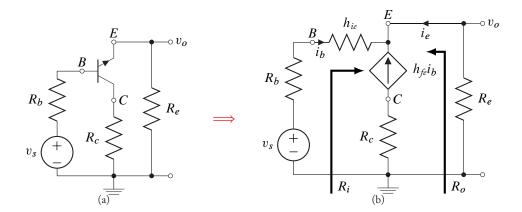

In order to determine the AC performance of this amplifier, the quiescent conditions must first be obtained. If the BJT is operating in the forward-active region, an AC equivalent model of the circuit can be obtained (Figure 5.12a) and the BJT can be replaced by its *h*-parameter model<sup>11</sup> (based on the quiescent conditions) in the AC equivalent circuit (Figure 5.12b). Circuit performance parameters can now be obtained from this equivalent circuit.

<sup>&</sup>lt;sup>11</sup>The initial calculations assume that  $h_{oe}$  is small and can be ignored. Calculations to determine the effect of non-zero  $h_{oe}$  follow in Subsection 5.3.2.

Figure 5.11: A common-emitter amplifier with an emitter resistor.

Figure 5.12: AC modeling of a common-emitter amplifier with an emitter resistor. (a) The smallsignal circuit: DC sources set to zero; (b) BJT replaced by h-parameter model.

# **Current Gain**

The current gain is defined as the ratio of load current to input current, that is:

$$A_I \equiv \frac{i_l}{i_b} = \frac{-i_c}{i_b}.\tag{5.50}$$

The ratio of collector to base current remains unchanged from the simple common-emitter amplifier. The current gain is dependent only on the BJT characteristics and independent of any

other circuit element values. Its value is given by:

$$A_I = -h_{fe}. (5.51)$$

### **Input Resistance**

The input resistance (shown in Figure 5.12b) is given by:

$$R_i \equiv \frac{v_b}{i_b} = \frac{h_{ie}i_b + R_e(i_b + h_{fe}i_b)}{i_b} = h_{ie} + (h_{fe} + 1)R_e.$$

(5.52)

The addition of an emitter resistor has greatly increased the input resistance of the amplifier. From the input of the BJT, the emitter resistor appears to act as a resistor in series with  $h_{ie}$  that is  $(h_{fe} + 1)$  times its true value.

### Voltage Gain

The voltage gain is the ratio of output voltage to input voltage. If the input voltage is again taken to be the voltage at the input to the transistor,  $v_b$ :

$$A_V \equiv \frac{v_o}{v_b}.\tag{5.53}$$

Using methods similar to those of the simple common-emitter amplifier to calculate the voltage gain yields:

$$A_V = \frac{v_o}{v_b} = \left(\frac{v_o}{i_l}\right) \left(\frac{i_l}{i_b}\right) \left(\frac{i_b}{v_b}\right),\tag{5.54}$$

or

$$A_V = (R_c)(A_I)\left(\frac{1}{R_i}\right) = \frac{-h_{fe}R_c}{h_{ie} + (h_{fe} + 1)R_e}.$$

(5.55)

For large values of  $h_{fe}$ , the external resistors dominate the expression for voltage gain. A rough approximation, which somewhat over-estimates the magnitude of the gain, is:

$$A_V \approx -\frac{R_c}{R_e}. ag{5.56}$$

Often the voltage gain from the source to the load is of interest as well. This overall voltage gain can be defined as:

$$A_{VS} \equiv \frac{v_o}{v_s}.\tag{5.57}$$

This ratio can be directly derived from the voltage gain,  $A_V$ , and a voltage division between the source resistance,  $R_s$ , and the amplifier input resistance,  $R_i$ :

$$A_{VS} = \frac{v_o}{v_s} = \left(\frac{v_o}{v_b}\right) \left(\frac{v_b}{v_s}\right) = A_V \left(\frac{R_i}{R_i + R_s}\right),\tag{5.58}$$

or

$$A_{VS} = \left(\frac{-h_{fe}R_c}{R_i}\right) \left(\frac{R_i}{h_{ie} + (h_{fe} + 1)R_e + R_s}\right) = \frac{-h_{fe}R_c}{h_{ie} + (h_{fe} + 1)R_e + R_s}.$$

(5.59)

# **Output Resistance**

The output resistance is defined as the Thévenin resistance at the output of the amplifier looking back into the amplifier. As in the case of the simple common-emitter amplifier,  $R_o$  is measured without considering  $R_c$  (Figure 5.12). Once again, the resistance looking into the collector of the BJT is very large,  $R_o \approx \infty$ .

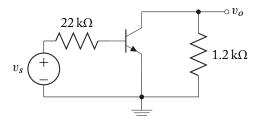

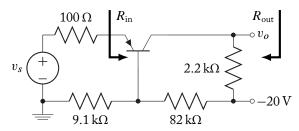

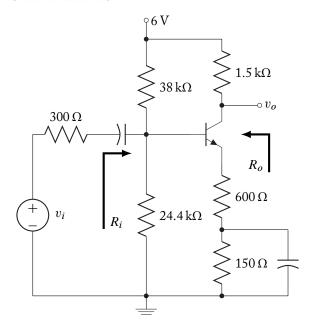

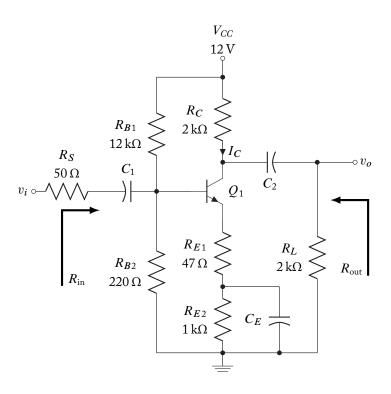

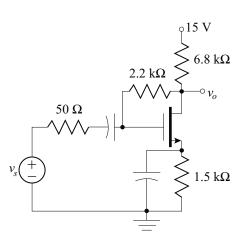

# Example 5.6

Given a Silicon *npn* BJT with parameters:

$$\beta_F = 150$$

$V_A = 350 \,\text{V},$

operating in the given circuit at room temperature.

Determine the small-signal characteristics:

Voltage Gain,  $v_o/v_s$ Input Resistance,  $R_i$ Output Resistance,  $R_o$ .

#### **Solution:**

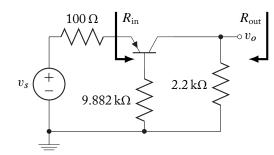

The modeling process begins with solving for the quiescent circuit conditions. In this particular circuit, the identical transistor was placed in the same quiescent circuit in Example 5.4. There is no need to repeat identical operations to find the small-signal model of the BJT. The

results of process steps 1 through 3 were:

$$\begin{split} I_B &= 62.0\,\mu\text{A} \quad I_C = 9.30\,\text{mA} \\ h_{fe} &= 150 \qquad \quad h_{ie} = 422\,\Omega \qquad r_o = 37.6\,\text{k}\Omega\,. \end{split}$$

The next step is to create an AC equivalent circuit and insert the BJT *h*-parameter model into the AC equivalent circuit or use previously derived results. The general topology of a common-emitter amplifier with an emitter resistor has previous results. The AC equivalent circuit is shown below

The voltage gain, as defined, is determined from Equation (5.59):

$$A_{VS} = \frac{-(150)(1200)}{422 + (151)(100) + 22,000} = -4.7972 \approx -4.80.$$

$R_i$ , as shown, is given by Equation (5.52):

$$R_i = 422 + (151)(100) = 15,522 \approx 15.5 \,\mathrm{k}\Omega$$

.

The output resistance,  $R_o$ , is given by the parallel combination of the output resistance of the amplifier and the collector resistor,  $R_c$ :

$$R_o \approx \infty//1.2 \,\mathrm{k}\Omega = 1.2 \,\mathrm{k}\Omega$$

.

# 5.3.2 THE EFFECT OF NON-ZERO $h_{oe}$ ON COMMON-EMITTER AMPLIFIERS WITH AN EMITTER RESISTOR

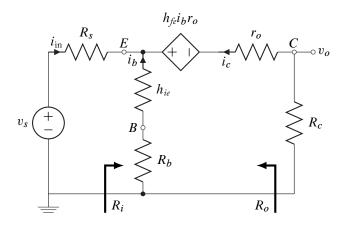

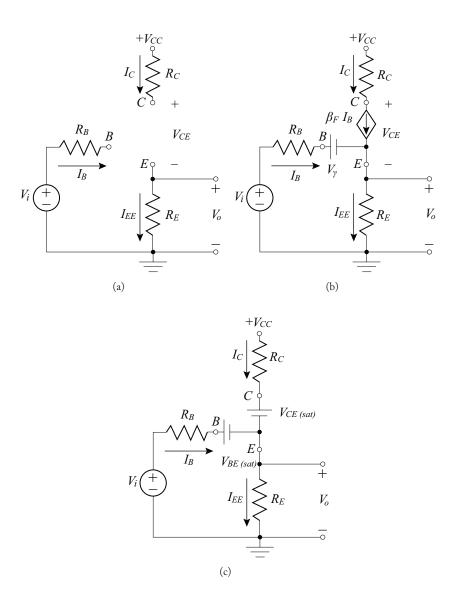

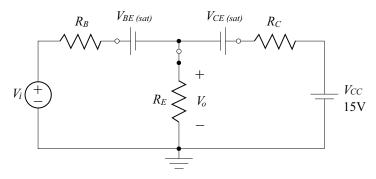

As with simple common-emitter amplifiers, the effects of non-zero  $h_{oe}$  can only be seen when the collector resistance becomes large: when  $R_c$  approaches or exceeds  $r_o$  in magnitude. With simple common-emitter amplifiers, the most noticeable effect of non-zero  $h_{oe}$  is on the output resistance of the amplifier. Input resistance is unaffected, while the current and voltage gain are limited if the external collector resistance,  $R_c$ , is large. Non-zero  $h_{oe}$  in the presence of an emitter resistor effects all the common-emitter amplifier characteristics in a complex fashion.

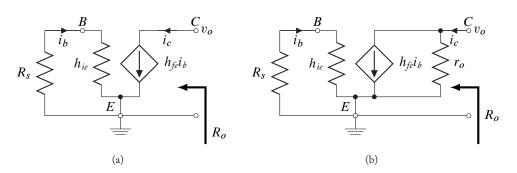

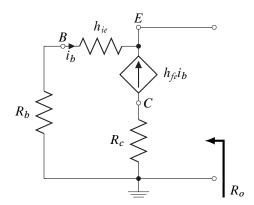

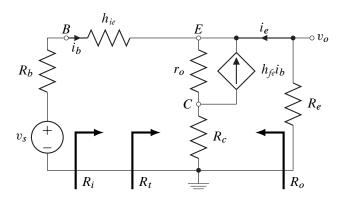

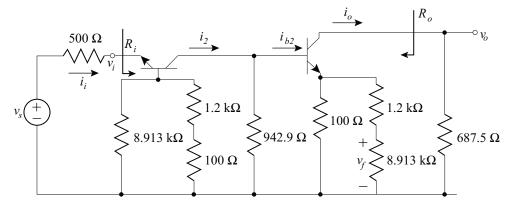

Expressions for the input resistance, voltage gain, and current gain are obtained using the AC equivalent circuits of Figure 5.13. Figure 5.13b is obtained from the more-traditional Figure 5.13a through a source transformation on the dependent current source and  $r_0$ . Symbolic manipulations of Kirchhoff's Laws are facilitated through this well-known transformation.

Figure 5.13: AC equivalent circuits—non-zero  $h_{oe}$ .

### **Input Resistance**

The input resistance can be determined by first finding  $R_t$  (as shown on Figure 5.13) and then adding the resistance,  $h_{ie}$ :

$$R_i = h_{ie} + R_t. ag{5.60}$$

In the usual Thévenin process, a voltage, v, is applied across  $R_e$ . The input current is then found to be:

$$i_b = \frac{v}{R_e} + \frac{v - h_{fe}i_b r_o}{r_o + R_c}. (5.61)$$

Collecting terms yields:

$$i_b \left\{ \frac{(1 + h_{fe})r_o}{r_o + R_c} \right\} = v \left\{ \frac{1}{R_e} + \frac{1}{r_o + R_c} \right\}. \tag{5.62}$$

Which leads to the Thévenin resistance,  $R_t$ :

$$R_t = \frac{v}{i_h} = (1 + h_{fe})R_e \left[ \frac{r_o}{r_o + R_c + R_e} \right]. \tag{5.63}$$

The desired input resistance is found using Equation (5.60):

$$R_i = h_{ie} + R_t = h_{ie} + (1 + h_{fe})R_e \left[ \frac{r_o}{r_o + R_c + R_e} \right].$$

(5.64)

An interesting result of these calculations is that large values of the collector resistor,  $R_c$ , will reduce the value of the amplifier input resistance!

#### Voltage Gain

The voltage gain can be calculated as follows by continuing with the circuit of Figure 5.13 and many of the calculations used in determining the input resistance. The output voltage for this circuit is taken across the collector resistor,  $R_c$ . It can be obtained through a simple voltage division from the voltage, v, (taken across  $R_e$ ):

$$v_o = \frac{R_c}{R_c + r_o} \left[ v - h_{fe} i_b r_o \right], \tag{5.65}$$

where, including the presence of  $h_{ie}$  in Figure 5.13,

$$v = v_s \left\lceil \frac{R_t}{h_{ie} + R_t} \right\rceil \quad \text{and} \quad i_b = \frac{v_s}{h_{ie} + R_t}. \tag{5.66}$$

Substitution of these two expressions into Equation (5.65) leads directly to the voltage gain:

$$A_V = \frac{v}{v_s} = -\frac{h_{fe}(R_c//r_o)}{R_i} + \frac{R_c}{R_c + r_o} \frac{R_t}{R_i} \approx -\frac{h_{fe}(R_c//r_o)}{R_i}.$$

(5.67)

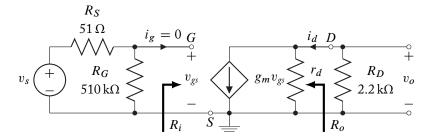

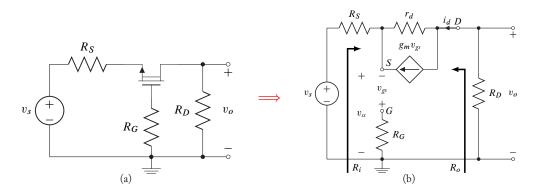

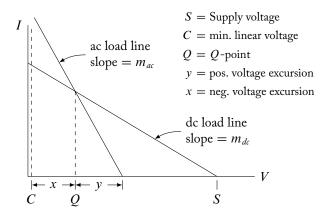

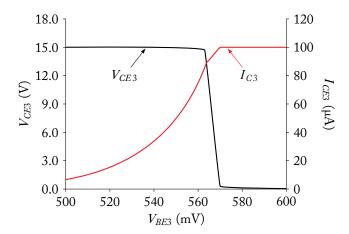

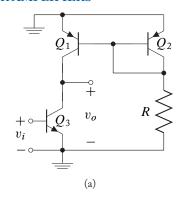

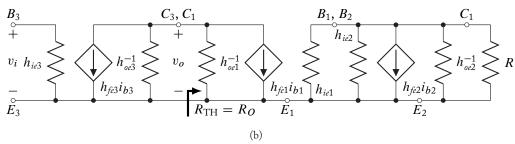

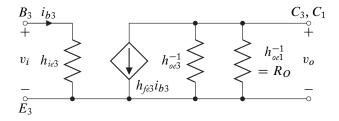

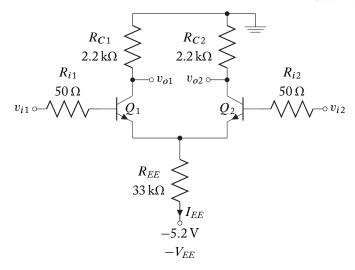

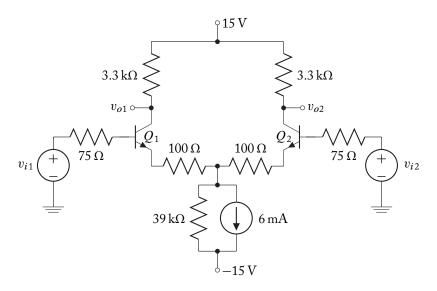

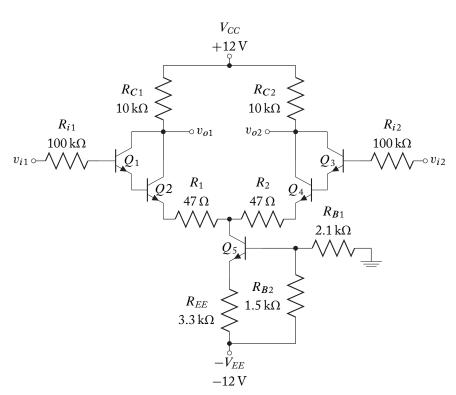

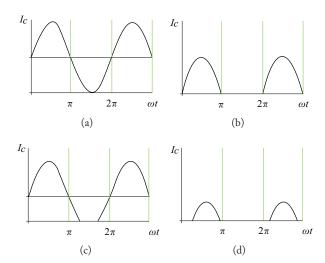

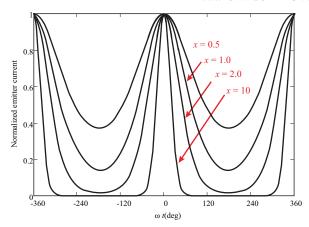

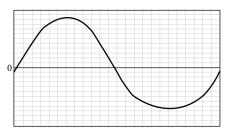

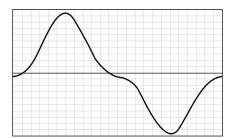

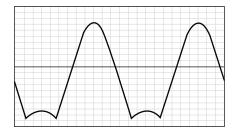

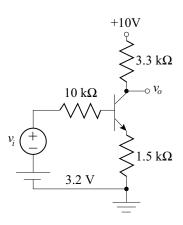

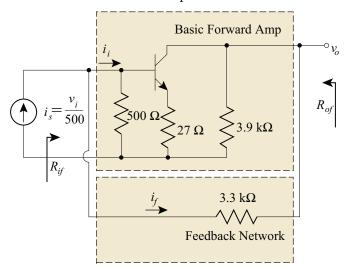

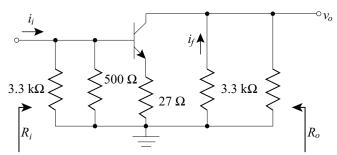

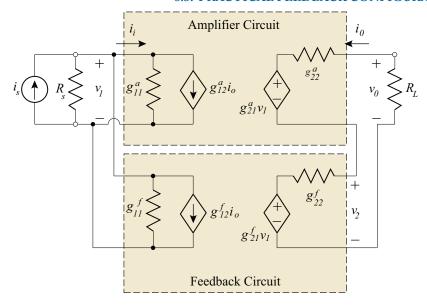

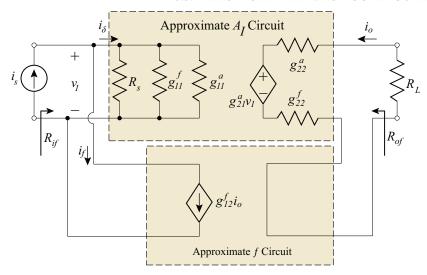

For the special case of significantly large  $R_e$ ,