# **Digital Electronics 1**

## **Combinational Logic Circuits**

**Tertulien Ndjountche**

Digital Electronics 1

Series Editor Robert Baptist

## **Digital Electronics 1**

Combinational Logic Circuits

Tertulien Ndjountche

First published 2016 in Great Britain and the United States by ISTE Ltd and John Wiley & Sons, Inc.

Apart from any fair dealing for the purposes of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act 1988, this publication may only be reproduced, stored or transmitted, in any form or by any means, with the prior permission in writing of the publishers, or in the case of reprographic reproduction in accordance with the terms and licenses issued by the CLA. Enquiries concerning reproduction outside these terms should be sent to the publishers at the undermentioned address:

ISTE Ltd 27-37 St George's Road London SW19 4EU UK

www.iste.co.uk

John Wiley & Sons, Inc. 111 River Street Hoboken, NJ 07030 USA

www.wiley.com

© ISTE Ltd 2016

The rights of Tertulien Ndjountche to be identified as the author of this work have been asserted by him in accordance with the Copyright, Designs and Patents Act 1988.

Library of Congress Control Number: 2016939642

British Library Cataloguing-in-Publication Data A CIP record for this book is available from the British Library ISBN 978-1-84821-984-7

## Contents

|                                                        | 1X |

|--------------------------------------------------------|----|

| Chapter 1. Number Systems                              | 1  |

| 1.1. Introduction                                      | 1  |

| 1.2. Decimal numbers                                   | 1  |

| 1.3. Binary numbers                                    | 2  |

| 1.4. Octal numbers                                     | 4  |

| 1.5. Hexadecimal numeration                            | 5  |

| 1.6. Representation in a radix B                       | 6  |

| 1.7. Binary-coded decimal numbers                      | 7  |

| 1.8. Representations of signed integers                | 8  |

| 1.8.1. Sign-magnitude representation                   | 9  |

| 1.8.2. Two's complement representation                 | 10 |

| 1.8.3. Excess-E representation                         | 12 |

| 1.9. Representation of the fractional part of a number | 13 |

| 1.10. Arithmetic operations on binary numbers          | 16 |

| 1.10.1. Addition                                       | 16 |

| 1.10.2. Subtraction                                    | 17 |

| 1.10.3. Multiplication                                 | 18 |

| 1.10.4. Division                                       | 19 |

| 1.11. Representation of real numbers                   | 20 |

| 1.11.1. Fixed-point representation                     | 20 |

| 1.11.2. Floating-point representation                  | 22 |

| 1.12. Data representation                              | 28 |

| 1.12.1. Gray code                                      | 28 |

| 1.12.2. p-out-of-n code                                | 29 |

| 1.12.3. ASCII code                                     | 31 |

| 1.12.4. Other codes                                    | 31 |

| 1.13. Codes to protect against errors                  | 31 |

|                                                        |    |

| 1.13.1. Parity bit                                                    | 31       |

|-----------------------------------------------------------------------|----------|

| 1.13.2. Error correcting codes                                        | 33       |

| 1.14. Exercises                                                       | 36       |

| 1.15. Solutions                                                       | 38       |

| Chapter 2. Logic Gates                                                | 49       |

| 2.1. Introduction                                                     | 49       |

|                                                                       | 49<br>50 |

| 2.2. Logic gates                                                      | 50<br>51 |

| 2.2.1. NOT gate                                                       | 51       |

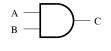

| 2.2.2. AND gate                                                       | 51       |

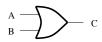

| 2.2.3. OR gate                                                        | 52<br>52 |

| 2.2.4. XOR gate                                                       |          |

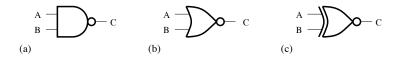

| 2.2.5. Complementary logic gates                                      | 53       |

| 2.3. Three-state buffer                                               | 54       |

| 2.4. Logic function                                                   | 54       |

| 2.5. The correspondence between a truth table and a logic function    | 55       |

| 2.6. Boolean algebra                                                  | 57       |

| 2.6.1. Boolean algebra theorems                                       | 59       |

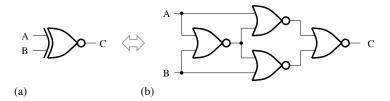

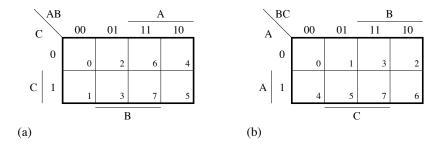

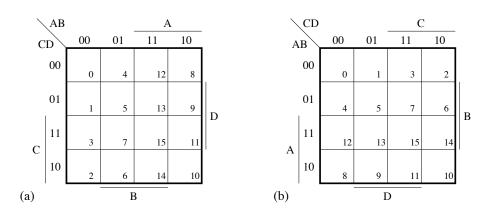

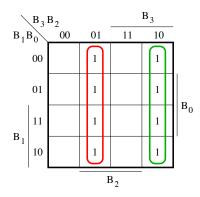

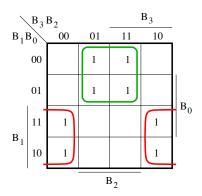

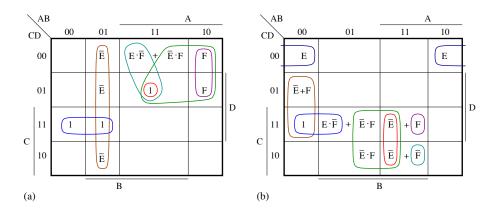

| 2.6.2. Karnaugh maps                                                  | 65       |

| 2.6.3. Simplification of logic functions with multiple outputs        | 73       |

| 2.6.4. Factorization of logic functions                               | 74       |

| 2.7. Multi-level logic circuit implementation                         | 76       |

| 2.7.1. Examples                                                       | 77       |

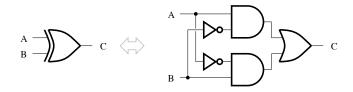

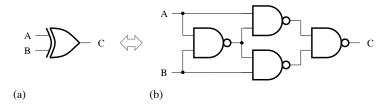

| 2.7.2. NAND gate logic circuit                                        | 78       |

| 2.7.3. NOR gate based logic circuit                                   | 80       |

| 2.7.4. Representation based on XOR and AND operators                  | 82       |

| 2.8. Practical considerations                                         | 89       |

| 2.8.1. Timing diagram for a logic circuit                             | 90       |

| 2.8.2. Static hazard                                                  | 90       |

| 2.8.3. Dynamic hazard                                                 | 92       |

| 2.9. Demonstration of some Boolean algebra identities                 | 93       |

| 2.10. Exercises                                                       | 97       |

| 2.11. Solutions                                                       | 101      |

| Chapter 3. Function Blocks of Combinational Logic                     | 115      |

| 3.1. Introduction                                                     | 115      |

| 3.2. Multiplexer                                                      | 115      |

| 3.3. Demultiplexer and decoder                                        | 121      |

| 3.4. Implementation of logic functions using multiplexers or decoders | 127      |

| 3.4.1. Multiplexer                                                    | 127      |

| 3.4.2. Decoder                                                        | 127      |

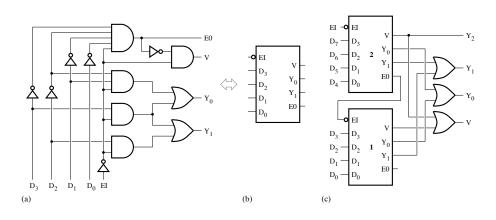

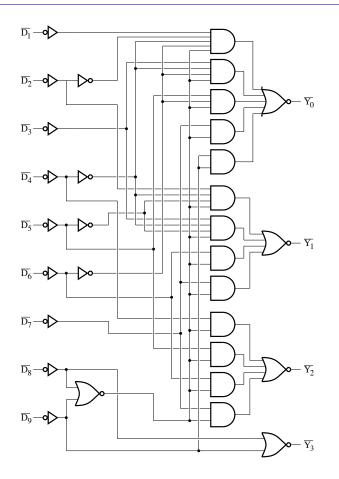

| 3.5. Encoders                                                         | 130      |

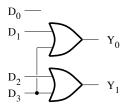

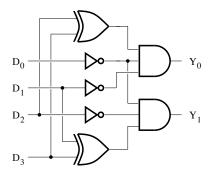

| 3.5.1. 4:2 encoder                                                    |          |

|                                                                       | 1.01     |

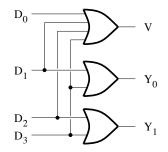

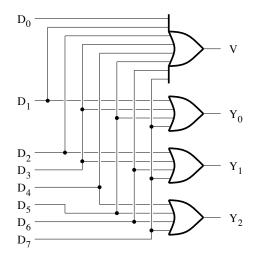

| 3.5.2. 8:3 encoder                                               | 34         |

|------------------------------------------------------------------|------------|

| 3.5.3. Priority encoder                                          | 36         |

| 3.6. Transcoders                                                 | 43         |

| 3.6.1. Binary code and Gray code                                 | 43         |

| 3.6.2. BCD and excess-3 code                                     | 49         |

| 3.7. Parity check generator                                      | 55         |

| 3.8. Barrel shifter                                              | 60         |

| 3.9. Exercises                                                   | 65         |

| 3.10. Solutions                                                  | 73         |

| Chapter 4. Systematic Methods for the Simplification of          |            |

|                                                                  | 203        |

| •                                                                |            |

|                                                                  | 203        |

|                                                                  | 203        |

|                                                                  | 204        |

|                                                                  | 204        |

|                                                                  | 205        |

|                                                                  | 205        |

|                                                                  | 207        |

| 8 I                                                              | 208<br>215 |

|                                                                  | 215<br>220 |

|                                                                  |            |

| 5 1                                                              | 220<br>221 |

| ·····                                                            | 221<br>224 |

|                                                                  | 224        |

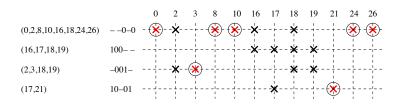

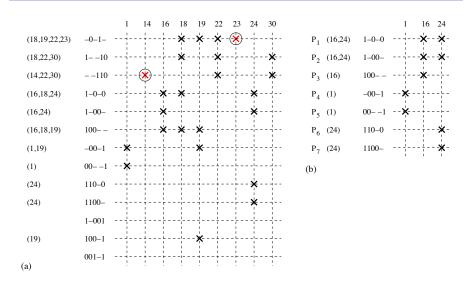

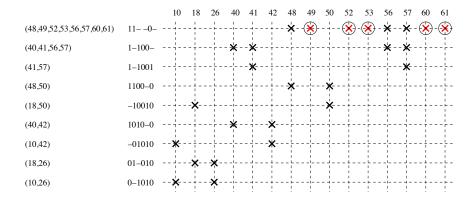

| 4.4.3. Quine–McCluskey technique: simplification of incompletely | 235        |

|                                                                  | 235<br>235 |

|                                                                  |            |

|                                                                  | 241<br>243 |

| 4.6. Solutions                                                   | :43        |

| Bibliography 2                                                   | 257        |

| Index                                                            | 259        |

### Preface

The omnipresence of electronic devices in everyday life is accompanied by the decreasing size and the ever-increasing complexity of digital circuits. This comprehensive and easy-to-understand work deals with the basic principles of digital electronics and allows the reader to grasp the subtleties of digital circuits, from logic gates to finite-state machines. It presents all the aspects related to combinational logic and sequential logic. It introduces techniques for simply and concisely establishing logic equations as well as methods for the analysis and design of digital circuits. Emphasis has been especially laid on design approaches that can be used to ensure a reliable operation of finite-state machines. Various programmable logic circuit structures and their applications have also been presented. Each chapter is completed by practical examples and well-designed exercises that are accompanied by worked solutions.

This book discusses all the different aspects of digital electronics, using a descriptive approach combined with a gradual, detailed and comprehensive presentation of basic concepts. The principles of combinational and sequential logic are presented, as well as the underlying techniques to the analysis and design of digital circuits. The analysis and design of digital circuits with increasing complexity is facilitated by the use of abstractions at the circuit and architecture levels. There are three volumes in this series devoted to the following subjects:

- 1) combinational logic circuits;

- 2) sequential and arithmetic logic circuits;

- 3) finite-state machines.

A progressive approach has been chosen and the chapters are relatively independent of each other. To help master the subject matter and put into practice the different concepts and techniques, the books are complemented by a selection of exercises and solutions.

#### 1. Summary

Volume 1 deals with combinational logic circuits. Logic gates are basic components in digital circuits. They implement Boolean logic functions and operations that are applied to binary-coded data. Combinational logic is used only for logic functions and operations whose outputs depend solely on the inputs. This first volume contains the following four chapters:

- 1) Number Systems;

- 2) Logic Gates;

- 3) Function Blocks of Combinational Logic;

- 4) Systematic Methods for the Simplification of Logic Functions.

#### 2. The reader

This book is an indispensable tool for all engineering students in bachelors or masters course who wish to acquire detailed and practical knowledge of digital electronics. It is detailed enough to serve as a reference for electronic, automation and computer engineers.

> Tertulien NDJOUNTCHE April 2016

### Number Systems

#### 1.1. Introduction

Digital systems are used to process data and to perform calculations in most instrumentation, monitoring and communication devices. As physical quantities and signals can only take discrete values in a digital system, the interpretation of real-world information requires the use of interface circuits such as data converters.

In general, numbers may be represented in different numeration systems. The decimal system is commonly used in routine transactions while the binary system is the basis for digital electronics. Every number (or numeration) system is defined by a base (or *radix*), which is a collection of distinct symbols. The representation of a number in a numeration system may be considered as a change in base. In a positional number system, a value of a number depends on the place occupied by each of its digits in the representation.

#### 1.2. Decimal numbers

The decimal number system uses the following 10 numbers or symbols: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. The radix is thus 10.

EXAMPLE 1.1.– Decompose the numbers 734 and 12345 into powers of 10.

The decomposition of the number 734 takes the form:

$$734 = (7 \times 10^2) + (3 \times 10^1) + (4 \times 10^0)$$

= 734<sub>10</sub>

For the number 12345, we have:

$$12\ 345 = (1 \times 10^4) + (2 \times 10^3) + (3 \times 10^2) + (4 \times 10^1) + (5 \times 10^0) \\ = 12\ 345_{10}$$

Depending on its position, each number is multiplied by the appropriate power of 10. The right-most digit represents the unit digit.

#### 1.3. Binary numbers

Binary number system is based on two-level logic, conventionally noted as 0 (low level) and 1 (high level). It is a system with a radix of two.

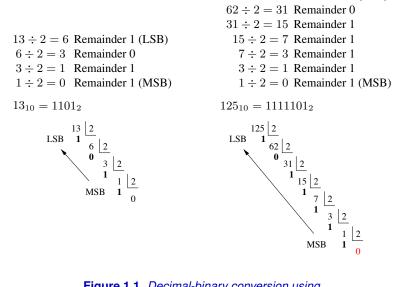

EXAMPLE 1.2.- Convert the decimal numbers 13 and 125 into binary numbers.

The decomposition of the number 13 in powers of 2 is written as:

$$13_{10} = (1 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0)$$

= 1101<sub>2</sub>

For the number 125, we have:

$$125_{10} = (1 \times 2^6) + (1 \times 2^5) + (1 \times 2^4) + (1 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0) = 1111101_2$$

The binary code that is then obtained for a positive number is called a natural binary code.

The coefficients or numbers (0 or 1) used in the binary representation of a number are called bits.

The right-most bit is called the *least significant bit* (LSB), while the left-most bit is called the *most significant bit* (MSB).

In practice, the conversion of a decimal number to a binary number can be carried out by reading, from last to first, the remainders of a series of integer divisions as illustrated by Figure 1.1.

The arithmetic and logic unit of a microprocessor manipulates binary numbers or *words* with a fixed number of bits.

$125 \div 2 = 62$  Remainder 1 (LSB)

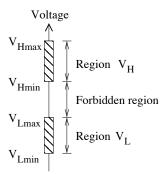

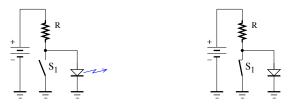

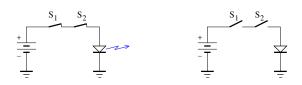

Figure 1.2. Representation of logic voltage levels

A byte is an 8-bit word.

In practice, the bits 0 and 1 are represented by voltage or current levels. Figure 1.2 shows the representation of logic voltage levels. The two regions  $V_H$  and  $V_B$  are separated by a forbidden region where the logical level is undefined.

Logical states may be assigned to regions based on positive logic or negative logic. In the case of positive logic, the region  $V_H$  corresponds to 1 (or the high level), and the region  $V_B$  corresponds to 0 (or the low level); and in the case of negative logic, the region  $V_H$  corresponds to 0 (or low level), and the region  $V_B$  corresponds to 1 (or high level).

#### 1.4. Octal numbers

The octal number system or a representation with radix eight consists of the following symbols: 0, 1, 2, 3, 4, 5, 6, 7.

EXAMPLE 1.3.- Convert the decimal numbers 250 and 777 to octal numbers.

In radix 8 representation, the number 250 takes the form:

$$250_{10} = (3 \times 8^2) + (7 \times 8^1) + (2 \times 8^0) = 372_8$$

In the case of the number 777, we have:

$$777_{10} = (1 \times 8^3) + (4 \times 8^2) + (1 \times 8^1) + (1 \times 8^0)$$

= 1 411<sub>8</sub>

The right-most digit is called the *least significant digit* (LSD), while the left-most digit is called the *most significant digit* (MSD).

A practical approach to converting a decimal number to an octal number consists of carrying out a series of integer divisions as illustrated in Figure 1.3.

Figure 1.3. Decimal-octal conversion using the successive division method

Octal numeration may be deduced from binary numeration by grouping, beginning from the right, consecutive bits in triplets or, conversely, by replacing each octal number by its three corresponding bits.

EXAMPLE 1.4.– Determine the radix 8 representation for the decimal numbers 85 and 129.

Radix 8 representations are obtained by replacing each group of three bits by the equivalent octal number. We can therefore write:

$$85_{10} = 1010101_2 = \underbrace{001}_{1} \underbrace{010}_{2} \underbrace{101}_{5} = 125_8$$

Similarly,

$$129_{10} = 10000001_2 = \underbrace{010}_2 \underbrace{000}_0 \underbrace{001}_1 = 201_8$$

#### 1.5. Hexadecimal numeration

The hexadecimal number system or a representation with a radix 16 consists of the following symbols: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F.

EXAMPLE 1.5.- Convert the decimal numbers 291 and 1000 to hexadecimal.

The number 291 is represented in radix 16 by:

$$291_{10} = (1 \times 16^2) + (2 \times 16^1) + (3 \times 16^0) = 123_{16}$$

For the number 1000, we obtain:

$$1\ 000_{10} = (3 \times 16^2) + (14 \times 16^1) + (8 \times 16^0)$$

= 3E8<sub>16</sub>

In practice, a series of integer divisions makes it possible to convert a decimal number to a hexadecimal number. The different remainders constitute the results of the conversion, beginning with the last, which is the MSD, to the first, which represents the LSD. We thus have:

| $291 \div 16 = 18$ Remainder 3 (LSD) | $1000 \div 16 = 62$ Remainder 8 (LSD) |

|--------------------------------------|---------------------------------------|

| $18 \div 16 = 1$ Remainder 2         | $62 \div 16 = 3$ Remainder 14         |

| $1 \div 16 = 0$ Remainder 1 (MSD)    | $3 \div 16 = 0$ Remainder 3 (MSD)     |

| $291_{10} = 123_{16}$                | $1000_{10} = 3E8_{16}$                |

Figure 1.4. Decimal-hexadecimal conversion using the successive division method

We can also proceed as demonstrated in Figure 1.4, the result of each conversion being made up of the successive remainders of the divisions.

Binary to hexadecimal conversion is done by grouping the bits representing the binary four by four and beginning from the right, conversely, replacing each hexadecimal digit by its four corresponding bits.

EXAMPLE 1.6.- Convert the decimal numbers 31 and 2,988 into hexadecimal.

To obtain the equivalent hexadecimal from the binary representation, each group of four bits is replaced by the corresponding hexadecimal digit. We therefore have:

$$31_{10} = 11111_2 = \underbrace{0001}_{1} \underbrace{1111}_{15=F} = 1F_{16}$$

Similarly,

$$2\ 988_{10} = 101110101100_2 = \underbrace{1011}_{11=B} \underbrace{1010}_{10=A} \underbrace{1100}_{12=C} = BAC_{16}$$

It is generally more convenient to represent the value of an octet using two hexadecimal digits as it is more compact.

#### 1.6. Representation in a radix B

In general, in radix B representation, a decimal number N may be decomposed as follows:

$$N_{10} = b_{n-1}B^{n-1} + \dots + b_2B^2 + b_1B^1 + b_0B^0$$

[1.1]

$$=\sum_{i=0}^{n-1} b_i B^i$$

[1.2]

where  $B \ge 2$ . Thus, the decimal number N is represented in radix B with n digits,  $b_{n-1} \cdots b_2 b_1 b_0$ .

Using n digits in a radix B numeration, we can code the decimal numbers from 0 to  $B^n - 1$ .

For an integer represented by n digits with a radix B, the formulas for conversion are as follows:

$$(b_{n-1}b_{n-2}\cdots b_2b_1b_0)_B = \sum_{i=0}^{n-1} b_i B^i$$

=  $b_{n-1}B^{n-1} + b_{n-2}B^{n-2} + \dots + b_2B^2 + b_1B^1 + b_0B^0$

=  $b_0 + B(b_1 + B(b_2 + B(\dots + B(b_{n-2} + Bb_{n-1})\dots)))$

=  $N_{10}$  [1.3]

EXAMPLE 1.7.– Convert the binary number  $110101_2$ , the octal number  $5671_8$  and the hexadecimal number  $5CAD_{16}$  to decimal.

In decimal form, the number  $110101_2$  is written as:

$$110111_{2} = \mathbf{1} \times 2^{5} + \mathbf{1} \times 2^{4} + \mathbf{0} \times 2^{3} + \mathbf{1} \times 2^{2} + \mathbf{1} \times 2^{1} + \mathbf{1} \times 2^{0}$$

=  $\mathbf{1} + 2(\mathbf{1} + 2(\mathbf{1} + 2(\mathbf{0} + 2(\mathbf{1} + 2 \times \mathbf{1}))))$

=  $55_{10}$

For the number  $5671_8$ , we get:

$$5671_8 = \mathbf{5} \times 8^3 + \mathbf{6} \times 8^2 + \mathbf{7} \times 8^1 + \mathbf{1} \times 8^0$$

=  $\mathbf{1} + 8(\mathbf{7} + 8(\mathbf{6} + 8 \times \mathbf{5}))$

=  $3001_{10}$

The conversion of the number  $5CAD_{16}$  to decimal is effected by:

$$5CAD_{16} = \mathbf{5} \times 16^3 + \mathbf{12} \times 16^2 + \mathbf{10} \times 16^1 + \mathbf{13} \times 16^0$$

=  $\mathbf{13} + 16(\mathbf{10} + 16(\mathbf{12} + 16 \times \mathbf{5}))$

=  $23725_{10}$

#### 1.7. Binary-coded decimal numbers

To represent a 8421-type *binary-coded decimal* (BCD) number, each digit must be replaced by its equivalent 4-bit binary.

EXAMPLE 1.8.- Give the BCD representation for the decimal numbers 90 and 873.

The BCD representation of the number 90 is written as follows:

$90_{10} = 1001 \ 0000_{BCD}$

For the number 873, we have:

$873_{10} = 1000\ 0111\ 0011_{BCD}$

Table 1.1 gives the hexadecimal, octal, binary and BCD representations of numbers from 0 to 15.

| Decimal | Representation |       |      |           |

|---------|----------------|-------|------|-----------|

| number  | Hexadecimal    | Octal | BCD  |           |

| 0       | 0              | 0     | 0000 | 0000      |

| 1       | 1              | 1     | 0001 | 0001      |

| 2       | 2              | 2     | 0010 | 0010      |

| 3       | 3              | 3     | 0011 | 0011      |

| 4       | 4              | 4     | 0100 | 0100      |

| 5       | 5              | 5     | 0101 | 0101      |

| 6       | 6              | 6     | 0110 | 0110      |

| 7       | 7              | 7     | 0111 | 0111      |

| 8       | 8              | 10    | 1000 | 1000      |

| 9       | 9              | 11    | 1001 | 1001      |

| 10      | А              | 12    | 1010 | 0001 0000 |

| 11      | В              | 13    | 1011 | 0001 0001 |

| 12      | C              | 14    | 1100 | 0001 0010 |

| 13      | D              | 15    | 1101 | 0001 0011 |

| 14      | Е              | 16    | 1110 | 0001 0100 |

| 15      | F              | 17    | 1111 | 0001 0101 |

Table 1.1. Conversion tables for 0 numbers to 15

It must be noted that with n bits, we can represent the decimal numbers between 0 and  $10^{n/4} - 1$ . In addition to the 8421 BCD code, there are other types of BCD codes.

#### 1.8. Representations of signed integers

Several approaches may be adopted to represent signed integers in digital systems: the *sign-magnitude* (*SM*) *representation*, *two's complement* (2*C*) *representation*, and *excess-E* (XSE) *representation*. Each of these approaches assumes the use of a format (or number of bits) fixed beforehand.

#### 1.8.1. Sign-magnitude representation

The simplest approach allowing for the representation of a signed integer consists of reserving the MSB for the number sign and the remaining bits for the number magnitude. If the sign bit is set to 0, the number is positive, and if the sign bit is set to 1, the number is negative.

EXAMPLE 1.9.– Using 8 bits, determine the sign-magnitude representation for each of the decimal numbers 55, -60, and 0.

We have:

$$55_{10} = 00110111_2$$

and  $55_{10} = 00110111_{SM}$

$60_{10} = 00111100_2$  and  $-60_{10} = 10111100_{SM}$

In the case of 0, two representations are possible:

$+0_{10} = 0000000_{SM}$  and  $-0_{10} = 1000000_{SM}$

The value of a decimal number N having an sign-magnitude representation of the form  $b_{n-1}b_{n-2}\cdots b_0$  is given by:

$$N_{10} = (-1)^{b_{n-1}} \sum_{i=0}^{n-2} b_i 2^i$$

[1.4]

or

$$N_{10} = (1 - 2b_{n-1}) \sum_{i=0}^{n-2} b_i 2^i$$

[1.5]

In this way, it is possible to represent the numbers in the range from  $-(2^{n-1}-1)$  to  $2^{n-1}-1$ , using n bits.

However, the sign-magnitude representation presents two problems. The first is linked to the two representations, +0 and -0, of the number 0. The second problem arises from the fact that this representation is not appropriate for addition operations, especially when one of the numbers is negative. The two's complement representation allows us to remedy these two problems.

#### 1.8.2. Two's complement representation

Two's complement representation of a number with n bits actually corresponds to the complement with respect to  $2^n$  and is defined as the difference between  $2^n$  and this number in absolute value.

EXAMPLE 1.10.– Determine the 8-bit two's complement representation of the numbers 90 and -120.

As the number 90 is positive, the two's complement representation is identical to the natural binary representation:

$$90_{10} = 01011010_2 = 01011010_{2C}$$

The number -120 is negative and the two's complement representation is obtained as follows:

$2^8 - 120 = 136$  and  $136_{10} = 10001000_2$  from which  $-120_{10} = 10001000_{2C}$

Similarly, the two's complement representation of a number may be obtained by taking the one's complement and then adding 1 (ignoring the overflow), because the sum of a number and its one's complement is equal to a number having all bits at 1 (or high logic level).

NOTE 1.1.– Assuming that the binary representation using n bits, of a positive number N takes the form,  $b_{n-1}b_{n-2}\cdots b_1b_0$ , the two's complement representation of -N may be written as follows:

$$2^{n} - N = (2^{n} - 1) - N + 1$$

=  $\underbrace{111 \cdots 11}_{n \text{ bits}} 2 - b_{n-1}b_{n-2} \cdots b_{1}b_{0} + 1$  [1.6]

where

$$2^n - 1 = \underbrace{111\cdots 11}_{n \text{ bits}} 2$$

and the subtraction

$$\underbrace{111\cdots11}_{n \text{ bits}} {}_2 - b_{n-1}b_{n-2}\cdots b_1b_0 \tag{1.7}$$

allows for the inversion of each bit of N or for obtaining the one's complement of N.

EXAMPLE 1.11.– The application of the above-cited method to determine the two's complement of the decimal number -120 using 8 bits translates to:

01111000 Binary representation of the decimal number 120 10000111 One's complement obtained by inverting each bit + 1 Addition of 1 10001000 Two's complement

and

$-120_{10} = 10001000_{2C}$

The value of a decimal number N with two's complement representation taking the form,  $b_{n-1}b_{n-2}\cdots b_0$ , is given by:

$$N_{10} = -b_{n-1}2^{n-1} + \sum_{i=0}^{n-2} b_i 2^i$$

[1.8]

Using n bits, we can represent the numbers in the range from  $-2^{n-1}$  to  $2^{n-1} - 1$ .

In the case of 8-bit two's complement representation, the highest positive value is:

$$2^{8-1} - 1 = 127_{10} = 01111111_{2C}$$

and the smallest negative value is:

$-2^{8-1} = -128_{10} = 1000000_{2C}$

NOTE 1.2.– To obtain two's complement representation from the binary representation of the corresponding positive number, we must:

identify the first 1 bit beginning from the right;

- take the one's complement for each bit located before the identified bit.

Let us determine the 8-bit two's complement representation for each of the numbers  $-10_{10}$  and  $-119_{10}$ .

Applying the procedure given in the previous note, as illustrated in Figure 1.5, two's complement representations are given by:

$-10_{10} = 11110110_{2C}$  and  $-119_{10} = 01110111_{2C}$

| Binary representation of 10 :         | Take the<br>one's complement<br>Right-most 1<br>00001010 |

|---------------------------------------|----------------------------------------------------------|

| Two's complement representation :     | 11110110                                                 |

| (a)                                   | 11110110                                                 |

|                                       | Take the<br>one's complement<br>Right-most 1             |

| Binary representation of 119 :        | 01110111                                                 |

| Two's complement representation : (b) | 10001001                                                 |

**Figure 1.5.** Obtaining a two's complement from the binary representation: **a**)  $-10_{10}$  and **b**)  $-119_{10}$

#### 1.8.3. Excess-E representation

Some systems use the excess-E representation in order to be able to represent negative numbers.

In excess-E representations, a number with n bits, whose unsigned value is N, where  $0 \le N \le N_{\max} = 2^n - 1$ , represents the signed integer N - E, where E is the offset of the code. We can, thus, represent signed numbers in the range from -E to  $N_{\max} - E$ . The value of the offset is, most often, of the form  $E = 2^{n-1}$  or  $E = 2^{n-1} - 1$ .

#### 1.8.3.1. Case where $E = 2^{n-1}$

Using an excess- $2^{n-1}$  code, any number N in the range from  $-2^{n-1}$  to  $2^{n-1} - 1$  is represented by the *n*-bit binary number,  $N + 2^{n-1}$ , which is always positive and less than  $2^n$ .

EXAMPLE 1.12.– Assuming that  $E = 2^{n-1}$ , where n = 4, determine the excess-E' representation of the decimal numbers 3 and -6.

The excess-8 code for the number 3 is obtained by determining the binary code for the result of the operation 3 + 8 = 11, that is:  $11_2 = 1011_2$ . Thus:

$$3_{10} = 1011_{XS8}$$

For the number -6, we have -6 + 8 = 2 and  $2_{10} = 0010_2$ . As a result:

$-6_{10} = 0010_{XS8}$

The excess- $2^{n-1}$  code corresponds to a two's complement representation where the sign bit is complemented (1 is replaced by 0 and vice versa).

#### 1.8.3.2. Case where $E = 2^{n-1} - 1$

With an excess  $2^{n-1} - 1$  code, we can represent the numbers N in the range from  $-(2^{n-1} - 1)$  to  $2^{n-1}$ .

A code similar to the excess  $2^{n-1} - 1$  code is adopted in the standard IEEE-754 used for the representation of the exponents of floating-point numbers.

EXAMPLE 1.13.- Represent the decimal numbers 27 and -43 using the excess- $2^{n-1} - 1$  code, where n = 8.

When n = 8, the value of the offset is  $E = 2^{8-1} - 1 = 2^7 - 1 = 127$ .

The excess-127 code for the number 27 is obtained by adding 127 to 27, and then converting the result to binary. That is:

27 + 127 = 154  $154_{10} = 10011010_2$  and  $27_{10} = 10011010_{XS127}$

For the excess-127 of the number -43, we have:

-43 + 127 = 84  $84_{10} = 01010100_2$  and  $-43_{10} = 01010100_{XS127}$

Table 1.2 gives the representations of unsigned and signed 3-bit integers. It must be noted that in sign-magnitude representations, the decimal number 0 has two codes,  $+0_{10} = 000_{SM}$  and  $-0_{10} = 100_{SM}$ . Using 3 bits, the two's complement representation allows for the coding of numbers from 3 to -4, while for the excess-3 representation, the numbers are in the range from 4 to -3.

#### 1.9. Representation of the fractional part of a number

A number is usually made up of an integer part and a fractional part, whose value is lower than 1. The fractional part of a number may be expressed as the sum of the negative powers of the radix of the numeration system.

The number 0.59375 is written in decimal representation as follows:

$$0.59375_{10} = (5 \times 10^{-1}) + (9 \times 10^{-2}) + (3 \times 10^{-3}) + (7 \times 10^{-4}) + (5 \times 10^{-5})$$

| Decimal | Representation |     |     |     |

|---------|----------------|-----|-----|-----|

| number  | Binary         | SM  | 2C  | XS3 |

| 7       | 111            |     |     |     |

| 6       | 110            |     |     |     |

| 5       | 101            |     |     |     |

| 4       | 100            |     |     | 111 |

| 3       | 011            | 011 | 011 | 110 |

| 2       | 010            | 010 | 010 | 101 |

| 1       | 001            | 001 | 001 | 100 |

| 0       | 000            | 000 | 000 | 011 |

| 0       | 000            | 100 | 000 | 011 |

| -1      |                | 101 | 111 | 010 |

| -2      |                | 110 | 110 | 001 |

| -3      |                | 111 | 101 | 000 |

| -4      |                |     | 100 |     |

Table 1.2. Representations of unsigned and signed 3-bit integers

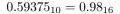

It can be converted into binary, octal and hexadecimal, as given below:

$$\begin{array}{l} 0.59375_{10} = (1 \times 2^{-1}) + (0 \times 2^{-2}) + (0 \times 2^{-3}) + (1 \times 2^{-4}) + (1 \times 2^{-5}) \\ = 0.10011_2 \\ = 0.\underbrace{100}_{4} \underbrace{110}_{6} = 0.46_8 \\ = 0.\underbrace{1001}_{9} \underbrace{1000}_{8} = 0.98_{16} \end{array}$$

The practical method to convert the fractional part of a number consists of carrying out a series of multiplications while extracting the integer part each time.

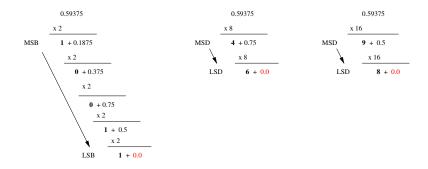

The different operations needed to convert the decimal number 0.59375 are shown in Figure 1.6:

- conversion to binary:

$\begin{array}{ll} 0.59375 \times 2 = 1.1875 & \text{Integer part 1 (MSB)} \\ 0.1875 \times 2 = 0.375 & \text{Integer part 0} \\ 0.375 \times 2 = 0.75 & \text{Integer part 0} \\ 0.75 \times 2 = 1.5 & \text{Integer part 1} \\ 0.5 \times 2 = 1.0 & \text{Integer part 1 (LSB)} \\ 0.59375_{10} = 0.10011_2 \end{array}$

- conversion to octal:

$0.59375 \times 8 = 4.75$  Integer part 4 (MSD)  $0.75 \times 8 = 6.0$  Integer part 6 (LSD)  $0.59375_{10} = 0.46_8$

- conversion to hexadecimal:

$\begin{array}{ll} 0.59375 \times 16 = 9.5 & \mbox{Integer part 9 (MSD)} \\ 0.50 \times 16 = 8.0 & \mbox{Integer part 8 (LSD)} \end{array}$

Figure 1.6. Conversion of the decimal number 0.59375 using the successive multiplication method

NOTE 1.3.– Converting certain fractional numbers produces an infinite sequence of bits.

Convert the decimal number 0.45 to binary. Successively multiplying by 2 and retaining the integer part of the result each time, we obtain:

$\begin{array}{ll} 0.45\times2=0.9 & \text{Integer part 0 (MSB)}\\ 0.9\times2=1.8 & \text{Integer part 1}\\ 0.8\times2=1.6 & \text{Integer part 1}\\ 0.6\times2=1.2 & \text{Integer part 1}\\ 0.2\times2=0.4 & \text{Integer part 0}\\ 0.4\times2=0.8 & \text{Integer part 0} \end{array}$

$0.8 \times 2 = 1.6$  Integer part 1  $0.6 \times 2 = 1.2$  Integer part 1  $0.2 \times 2 = 0.4$  Integer part 0  $0.4 \times 2 = 0.8$  Integer part 0 ...  $0.45_{10} = 0.01$  1100 1100 ... 1100<sub>2</sub>

When the binary representation corresponds to an infinite sequence, one criterion to determine the number of bits needed may be the precision that must be equivalent in both numeration systems. In the above example, if the absolute error (in decimal) is  $\pm 5 \times 10^{-3}$ , the expansion in powers of  $2^{-n}$  will then stop at the *n*th term for which the following condition is verified to be true:

$$2^{-n} < 5 \times 10^{-3} \tag{1.9}$$

Similarly, we have:

$$2^{n} \ge 200$$

$$n \ge \frac{\log(200)}{\log(2)} = 7.64 \simeq 8$$

We can thus stop at the eighth row. Thus:

$$0.45_{10} = 0.01110011_2$$

#### 1.10. Arithmetic operations on binary numbers

Arithmetic operations on binary numbers may be executed in the same way as for decimal numbers.

The addition is the most executed arithmetic operation in digital systems. The subtraction operation is essentially a variant of the addition operation, while multiplication and division operations may be carried out by combining logical functions (AND, OR, shift, etc.) and addition.

#### 1.10.1. Addition

In binary representation, we begin by adding bits of lower weight, and the carry that may be obtained when the sum of bits of the same weight exceeds the highest value that can be represented with one bit, that is 1, is transferred, each time, to the next MSB.

In binary representation, addition is carried out according to the following rules:

0 + 0 = 0 0 + 1 = 1 + 0 = 1 1 + 1 = 0 Carry 1 1 + 1 + 1 = 1 Carry 1

EXAMPLE 1.14.– Add the numbers 1010 and 1011.

Carrying out the addition operation in binary and decimal, we have:

$$\begin{array}{cccc} 1011 & & 11 \\ + & 0011 & & + & 3 \\ \hline 1110 & & & 14 \end{array}$$

The sum is obtained by adding the numbers, each of which is called the *addend*.

In practice, more than two numbers can be added in a digital system by initially determining the sum of the first two numbers, then adding this sum to the third number and so on.

#### 1.10.2. Subtraction

In binary representation, the execution of a subtraction operation takes place from the LSBs to the MSBs with the assumption that the number to be subtracted (or the subtrahend) is the smaller of the two operands. The difference is the result obtained upon subtracting the subtrahend from the minuend.

Before subtracting a number (bit at the logic level 1) from another number of lower value (bit at the logic level 0), we add the value of the radix (that is 2) to the latter and a borrow of 1 is then carried over to the next highest bit to be subtracted. The rules governing binary subtraction are:

0 - 0 = 0 0 - 1 = 1 Borrow 1 1 - 0 = 11 - 1 = 0

EXAMPLE 1.15.– Subtract the number 101 from the number 1010.

The subtraction may be carried out in binary representation and in decimal representation as follows:

| 1010   | 10  | Minuend    |

|--------|-----|------------|

| - 0101 | - 5 | Subtrahend |

| 0101   | 5   | Difference |

The difference is obtained by deducting the *subtrahend* from the *minuend*.

In practice, subtraction may be carried out like addition by using 2C representation, which allows for the coding of positive and negative numbers.

#### 1.10.3. Multiplication

Multiplication is carried out by forming a partial product for each bit of the multiplier and then adding all the partial products to generate the result. It must be noted that each partial product is shifted one position to the left with respect to the preceding one and the product of two *n*-bit numbers may possess up to 2n bits.

The multiplication table in binary representation can be summarized as follows:

$\begin{array}{l} 0\times 0 = 0\\ 0\times 1 = 0\\ 1\times 0 = 0\\ 1\times 1 = 1 \end{array}$

EXAMPLE 1.16.– Multiply the number 1101 by 1001.

Executing multiplication in binary representation translates to:

|          | 1101    | Multiplicand           |

|----------|---------|------------------------|

| $\times$ | 1001    | Multiplier             |

| -        | 1101    | First partial product  |

|          | 0000    | Second partial product |

|          | 0000    | Third partial product  |

| +        | 1101    | Fourth partial product |

|          | 1110101 | Product                |

This operation is the equivalent of  $13 \times 9 = 117$  in decimal.

By convention, the first factor in a multiplication operation is called the multiplicand and the second is called the multiplier. This distinction is of absolutely no consequence as the multiplication operation is commutative. The product is defined as the result of a multiplication.

Multiplication may be carried out like a succession of addition and shift operations.

#### 1.10.4. Division

Division of a binary number (the dividend) by another (the divisor) is carried out by repeatedly deducting the divisor from the dividend until you obtain a difference that is either equal to zero or inferior to the divisor and that represents the remainder. The quotient corresponds to the number of times the divisor is contained in the dividend.

When the dividend is a 2n-bit number and the divisor is an n-bit number, the quotient may be represented as an n-bit number. Division is executed by comparing the n bits of the divisor with the n LSBs of the dividend. If the divisor is greater than the dividend, no subtraction is performed, the corresponding quotient bit is set to 0, and the divisor is then compared to the n + 1 LSBs of the dividend. If, on the other hand, the divisor is less than or equal to the considered dividend bits, a subtraction is carried out and the corresponding quotient bit is set to 1. The comparison process of the divisor continues with the number obtained by lowering the next MSB of the dividend to the right of the previously obtained difference.

EXAMPLE 1.17.– Divide the number 10000100 by 1101.

In binary representation, the division is carried out as follows:

| Dividend  | 10000100      | 1101 | Divisor  |

|-----------|---------------|------|----------|

| _         | 1101          | 1010 | Quotient |

|           | 0111          | •    |          |

|           | 0111 <b>0</b> |      |          |

| _         | 1101          |      |          |

| Remainder | 010           | •    |          |

In decimal, we similarly have  $132 \div 13 = 10$  and the remainder is 2.

An integer number is divisible by another when the quotient is an integer number and the remainder is equal to zero.

#### 1.11. Representation of real numbers

Real numbers are useful in digital systems as they allow for a variety of calculations. They may be represented with a fixed point or floating point. Fixed-point representation allows for coding a fixed range of numbers and rapid calculation, while coding numbers of very different orders of magnitude is easier with floating-point representation.

#### 1.11.1. Fixed-point representation

In fixed-point representation, a number may be expressed in the form:

$$b_{q-1}b_{q-2}\cdots b_0, b_{-1}b_{-2}\cdots b_{-p}$$

[1.10]

The sign-bit  $b_{q-1}$  is either equal to 0, for a positive number, or 1, for a negative number. The first q numbers represent the integer part while the last p numbers constitute the fractional part.

According to the SM notation, the value of a decimal number represented in the radix B is given by:

$$N_{10} = (-1)^{b_{q-1}} \sum_{i=-p}^{q-2} b_i B^i$$

[1.11]

By setting p + q = n, we have:

$$N_{10} = (-1)^{b_{q-1}} \sum_{i=0}^{p+q-2} b_{i-p} B^{i-p}$$

[1.12]

$$= \left( (-1)^{b_{n-p-1}} \sum_{i=0}^{n-2} b_{i-p} B^i \right) B^{-p}$$

[1.13]

where n is the total number of bits. Fixed-point representation may thus be considered as representing an integer whose bits are shifted according to a factor, the scale of which depends on the radix. The maximum (minimum) value in a fixed-point representation is obtained by multiplying by a scaling factor the greatest (smallest) integer that can be represented with the same number of bits. Hence, the values that can be represented are of the form:

$$-(B^{n-1}-1)B^{-p} \le N_{10} \le (B^{n-1}-1)B^{-p}$$

[1.14]

EXAMPLE 1.18.- In fixed-point representation, we may obtain the following conversions:

$$124.37_{10} = (1 \times 10^2) + (2 \times 10^1) + (4 \times 10^0) + (3 \times 10^{-1}) + (7 \times 10^{-2})$$

$$11.625_{10} = (1 \times 2^3) + (0 \times 2^2) + (1 \times 2^1) + (1 \times 2^0) + (1 \times 2^{-1}) + (0 \times 2^{-2}) + (1 \times 2^{-3}) = 1011.101_2$$

$$20.75_{10} = (2 \times 8^1) + (4 \times 8^0) + (6 \times 8^{-1}) = 24.6_8$$

$$30.5_{10} = (1 \times 16^1) + (14 \times 16^0) + (8 \times 16^{-1}) = 1E.8_{16}$$

In 2C representation, the decimal value of a number can be expressed as:

$$N_{10} = \left(-b_{n-p-1} \cdot 2^{n-1} + \sum_{i=0}^{n-2} b_{i-p} 2^i\right) 2^{-p}$$

[1.15]

Using n bits, the range of numbers that may be represented is given by:

$$-2^{n-1}2^{-p} \le N \le (2^{n-1} - 1)2^{-p}$$

[1.16]

where the number of bits for the fractional part is equal to *p*.

EXAMPLE 1.19.– Give the 8-bit representation of the decimal numbers 6.25 and -8.4375.

We have:

$$\begin{aligned} 6.25_{10} &= (0 \times 2^3) + (1 \times 2^2) + (1 \times 2^1) + (0 \times 2^0) + (0 \times 2^{-1}) + (1 \times 2^{-2}) \\ &= 0110.0100_2 = 0110.0100_{2C} \\ -8.4375_{10} &= -(1 \times 2^3) + (0 \times 2^2) + (0 \times 2^1) + (0 \times 2^0) \\ &+ (0 \times 2^{-1}) + (1 \times 2^{-2}) + (1 \times 2^{-3}) + (1 \times 2^{-4}) \\ &= 1000.0111_{2C} \end{aligned}$$

The result obtained upon multiplying two n bit numbers must be stored in 2n bits. The size of the data may continually increase following the execution of other multiplication operations. As the product of the numbers in the range from -1 to 1 always stays in the same interval, the solution adopted in digital systems consists of using a representation (q = 1 and n = p + 1) in which the numbers are normalized and can only vary between -1 and 1.

#### 1.11.2. Floating-point representation

Floating-point representation may be considered as a scientific notation for digital systems. A certain number of floating-point representations have been proposed in order to satisfy the requirements of a variety of applications.

A decimal number N can be quantified and expressed in floating-point form as follows:

$$N_{10} = (-1)^S M \cdot B^E$$

[1.17]

where S is the sign-bit, M is the mantissa, B is the base or radix and E is the exponent. The mantissa is generally normalized and corresponds to a number beginning with a non-zero digit, as is the case with the following number representations:

$-1234.57_{10}$  is written as  $-1.23457 \times 10^3$ ; 0.0000071539<sub>10</sub> is written as  $+7.1539 \times 10^{-6}$ ; 100010100<sub>2</sub> is written as 1.00010100 × 2<sup>8</sup>.

As a result of the normalization of the mantissa, M, the number 0 cannot be represented directly from the expression [1.17]. To arrive at this, we must use a particular symbol. Indefinite numbers, such as the result of a division by 0 or the square root of a negative integer, are also represented using special characters.

#### 1.11.2.1. IEEE-754 standard

Norms or standards have been proposed in order to make the different representations of floating-point numbers uniform.

In the IEEE<sup>1</sup>-754 norm, the mantissa M and the exponent E must satisfy the following inequalities:

$$1 \le M < 2 \tag{1.18}$$

and

$$2 - 2^{k-1} \le E \le 2^{k-1} - 1 \tag{[1.19]}$$

1 IEEE: Institute of Electrical and Electronics Engineers.

The binary equivalent of the mantissa M is thus normalized, and the exponent E is written in biased form before being coded as a k-bit word. The values that can be represented for a number N are such that:

$$N_{\min} = 2^{2-2^{k-1}} \le |N| \le N_{\max} = (2-2^{-l})2^{2^{k-1}-1}$$

[1.20]

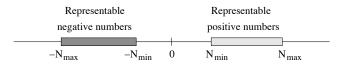

The parameter l is defined as being the number of bits of the mantissa. Figure 1.7 shows the range of numbers that can be represented in a floating-point format.

Figure 1.7. Range of numbers that can be represented in floating-point format

NOTE 1.4.– As the first digit of the mantissa is always 1, it can be taken as implied. This gives us an additional bit position that can be exploited to increase the range of representable numbers.

The relative difference between two adjacent numbers is of the order  $2^{l-l}$ . It is, therefore, necessary to round off some numbers before representing them.

| Precision | Normalized representation                        | Denormalized representation                         |

|-----------|--------------------------------------------------|-----------------------------------------------------|

| Single    | $\pm 2^{-126}$ to $(2-2^{-23}) \times 2^{127}$   | $\pm 2^{-149}$ to $(1 - 2^{-23}) \times 2^{-126}$   |

| Double    | $\pm 2^{-1022}$ to $(2-2^{-52}) \times 2^{1023}$ | $\pm 2^{-1074}$ to $(1 - 2^{-52}) \times 2^{-1022}$ |

Table 1.3. Range of numbers that can be represented with the IEEE-754 standard

The majority of numbers in IEEE-754 floating-point representation are normalized and have a mantissa of the form:

$$M = 1.\underbrace{f_1 f_2 \cdots f_l}_{f}$$

where the fractional part (or fraction) f is represented with l bits, and  $1 \le M < 2$ .

As shown in Table 1.4, the IEEE-754 standard defines two formats for number representation: single precision (or 32 bits, composed of 1 sign bit, 8 exponent bits

and 23 mantissa bits) and double precision (or 64 bits, composed of 1 sign-bit, 11 exponent bits and 52 mantissa bits).

|                          | Sign  | Biased   | Mantissa |

|--------------------------|-------|----------|----------|

|                          | bit   | exponent | fraction |

| 32 bit single precision  | 1 bit | 8 bits   | 23 bits  |

| 64 bits double precision | 1 bit | 11 bits  | 52 bits  |

Table 1.4. Number format based on the IEEE-754 standard

In addition to the single and double precisions, the IEEE-754 standard supports quadruple-precision representation (or 128 bits, composed of 1 sign bit, 15 exponent bits and 112 mantissa bits), which is chiefly used in some software.

When an arithmetic operation involving two numbers gives a result that has an exponent that is too small to be accurately represented, an underflow is produced. The IEEE-754 standard, through the use of denormalized representation, offers a means of gradually taking into account underflows.

A denormalized number is characterized by a biased exponent equal to 0 and a mantissa of the form:

$$M = 0.\underbrace{f_1 f_2 \cdots f_l}_{f}$$

The mantissa bits are shifted one position to the right to insert the first bit (implied in normalized representation), which now has the value 0. To compensate for the shift effect, the exponent is increased by 1.

Table 1.3 gives the range of numbers that can be represented using the IEEE-754 standard.

The exponent E is a signed k-bit integer such that  $E_{\min} \leq E \leq E_{\max}$ . Its representation corresponds to the representation of the biased value E + b, where b is the bias of the form  $2^{k-1} - 1$ . Furthermore,  $E_{\min} = -b + 1$  and  $E_{\max} = b$ . The exponents  $E_{\min} - 1$  and  $E_{\max} + 1$  (0 and  $2^k - 1$ , respectively, in the biased representation) are reserved for zero, denormalized numbers and special values.

To facilitate the coding of positive and negative values of the exponent, a bias, b, is added to the real value of the exponent, E, as follows:

$$E_b = \begin{cases} E+b, & \text{if the number is normalized} \\ E+b-1, & \text{if the number is denormalized} \end{cases}$$

[1.21]

Thus, in the IEEE-754 standard, the exponent corresponds to the binary representation of  $E_b$ .

EXAMPLE 1.20.– Represent the decimal numbers 79.625 and -1000.2 in IEEE-754 single precision.

In the IEEE-754 standard, a number is represented by a sign bit, a mantissa and an exponent. The normalized form of the binary equivalent of the number to be converted allows for the identification of the mantissa and the exponent.

The decimal number 79.625 can also be written as follows:

$79.625_{10} = 1001111.101_2 = 1.001111101_2 \times 2^6$

- sign bit: S = 0;

- biased exponent (8 bits):  $E_b = 6_{10} + 127_{10} = 133_{10} = 10000101_2$ ;

- fractional part of the mantissa (23 bits):

from which:

$79.625_{10} = 0\ 10000101\ 00111110100000000000000_{IEE754}$

The decimal number -1000.2 is represented in binary in the form:

$1000.2_{10} = 1111101000.0011001100110011_2$

The fractional part corresponds to a continually repeating binary sequence. The closest number to 1000.2 that may be represented is:

$$\begin{split} 1000.20001220703125_{10} &= 1111101000.00110011001101_2 \\ &= 1.11110100000110011001101_2 \times 2^9 \end{split}$$

- sign bit: S = 1;

- biased exponent (8 bits):  $E_b = 9_{10} + 127_{10} = 136_{10} = 10001000_2$ ;

- fractional part of the mantissa (23 bits):

$f = 11110100000110011001101_2$

and finally:

$-1000.2_{10} = 1\ 10001000\ 11110100000110011001101_{IEE754}$

In the above-cited single-precision IEEE-754 representations, the first bit indicates the sign, the next eight bits allow for the coding of the exponent and the last 23 bits correspond to the fractional part of the mantissa.

The different values taken by the numbers in IEEE-754 representations are recorded in Table 1.5. The IEEE-754 standard uses special symbols (NaN, infinity) to indicate numbers that have an exponent composed entirely of bits set to 0 or 1. The NaN or *not a number* value is used to represent a value that does not correspond to a real number.

|              | Exponent                    | Fraction  | Value                          |

|--------------|-----------------------------|-----------|--------------------------------|

| Normalized   | $E_{min} \le E \le E_{max}$ | $f \ge 0$ | $\pm (1.f) \times 2^E$         |

| Denormalized | $E = E_{min} - 1$           | f > 0     | $\pm (0.f) \times 2^{E_{min}}$ |

| Zero         | $E = E_{min} - 1$           | f = 0     | $\pm 0$                        |

| Infinite     | $E = E_{max} + 1$           | f = 0     | $\pm\infty$                    |

| Not a Number | $E = E_{max} + 1$           | f > 0     | NaN                            |

Table 1.5. Values of numbers in IEEE-754 representations

EXAMPLE 1.21.– Find the decimal number corresponding to the following singleprecision IEEE-754 representation:

$1 \ 10000111 \ 110000000000000000000100001_{IEE754}$

We have:

- sign bit: S = 1;

- biased exponent (8 bits):  $E_b = 10000111_2 = 135_{10}$ ;

- fractional part of the mantissa (23 bits):

Applying the formula to the expression of real numbers by starting from the IEEE-754 representation, that is:

$$N_{10} = (-1)^S (1.f) \times 2^{(E_b - 127)}$$

we find:

$$N_{10} = (-1)^{1} (1.1100000000000000000100001_{2}) \times 2^{(135-127)}$$

= (-1)(111000000.00000000000000000\_{2})

= (-1)(2^{8} + 2^{7} + 2^{6} + 2^{-10} + 2^{-15})

= -448.00100708\_{10}

from which:

1 10000111 110000000000000000000001\_{IEE754} = -448.001\_{10}

# 1.11.2.2. Arithmetic operations on floating-point numbers

Let  $x = M_x \cdot B^{E_x}$  and  $y = M_y \cdot B^{E_y}$  be two positive numbers (sign-bit S = 0).

Supposing that  $E_x \ge E_y$ ,  $y = M_Y \cdot B^{E_x}$  and  $M_Y = M_y B^{(E_x - E_y)}$ , we have:

$$x + y = (M_x + M_Y) \cdot B^{E_x}$$

[1.22]

and

$$x - y = (M_x - M_Y) \cdot B^{E_x}$$

[1.23]

In a floating-point representation, the numbers to be added or subtracted must, thus, have the same exponent, such as:

$$\begin{split} 145.500_{10} &= 10010001.100_2 = 0.10010001100 \times 2^8 \\ 27.625_{10} &= 00011000.101_2 = 0.00011011101 \times 2^8 \end{split}$$

In the case of multiplication and division, the results are obtained as follows:

$$x \times y = (M_x \times M_y) \cdot B^{(E_x + E_y)}$$

[1.24]

and

$$x/y = (M_x/M_y) \cdot B^{(E_x - E_y)}$$

[1.25]

It must be noted that because of the overflow effect or round-off errors, the arithmetic operations in a floating-point representation do not have exactly the same properties (associativity, distributivity) as with real numbers.

#### 1.12. Data representation

As the arithmetic unit of a digital system recognizes only the binary states 0 and 1, a code is necessary to manipulate and transfer alphanumeric data (numbers, letters, special characters) between a digital system and its peripheral devices.

### 1.12.1. Gray code

Gray code (or reflected binary code) is a non-weighted code, as it does not ascribe a specific weight to each bit position. It is not used for arithmetic calculations.

An interesting feature presented by Gray code representation is related to the fact that only a single bit changes value during the transition from one code to the next. Table 1.6 gives the binary and Gray code representation of decimal numbers from 0 to 15.

The conversion of a binary number to Gray code is carried out by making use of the following observations:

- the most significant Gray code bit, situated to the extreme left, is the same as the corresponding MSB for the binary number;

- starting from the left, add, without taking into account the carry-out bit, each pair of adjacent bits to obtain the next bit in Gray code.

EXAMPLE 1.22.– Convert the binary number  $11001_2$  to Gray code.

| Binary number | 1 - | + 1 -        | +0           | +0           | + 1          |

|---------------|-----|--------------|--------------|--------------|--------------|

|               | ₽~  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Gray code     | 1   | 0            | 1            | 0            | 1            |

For the binary number  $11001_2$ , the corresponding Gray code is 10101.

To convert Gray code to a binary number:

- the MSB of the binary number, located at the extreme left, is identical to the corresponding Gray code bit;

- starting from the left, add each new bit of the binary code to the next bit of the Gray code, without taking into account any carry-out bit, to obtain the next bit of the binary code.

| Decimal | Binary | Gray | Decimal | Binary | Gray |

|---------|--------|------|---------|--------|------|

| number  | number | code | number  | number | code |

| 0       | 0000   | 0000 | 8       | 1000   | 1100 |

| 1       | 0001   | 0001 | 9       | 1001   | 1101 |

| 2       | 0010   | 0011 | 10      | 1010   | 1111 |

| 3       | 0011   | 0010 | 11      | 1011   | 1110 |

| 4       | 0100   | 0110 | 12      | 1100   | 1010 |

| 5       | 0101   | 0111 | 13      | 1101   | 1011 |

| 6       | 0110   | 0101 | 14      | 1110   | 1001 |

| 7       | 0111   | 0100 | 15      | 1111   | 1000 |

**Table 1.6.** Binary and Gray code representation of<br/>decimal numbers from 0 to 15

EXAMPLE 1.23.- Convert the Gray code 10111 to a binary number.

| Gray code     | 1 | 0  | 1  | 1  | 1 |

|---------------|---|----|----|----|---|

|               |   | +} | +} | +} | + |

| Binary number | 1 | 1  | 0  | 1  | 0 |

The binary number corresponding to Gray code 10111 is  $11010_2$ .

Gray code is used in Karnaugh maps and in the design of logic circuits. They also find application in rotary encoders, where the predisposition to errors increases with the number of bits that change logical states between two consecutive positions.

### 1.12.2. p-out-of-n code

A *p*-out-of-*n* code is an *n*-bit representation that allows only combinations made up of *p* bits at 1 and (n - p) bits at 0. The number of valid combinations for a *p*-out-of-*n* code is n!/[(n - p)!p!].

The p-out-of-n code allows for the detection of errors based on the verification of the number of 1s and 0s at the time of reading of each code combination.

Some barcodes use p-out-of-n encoding, such as 2-out-of-5 encoding. Table 1.7 offers some examples of 2-out-of-5 code. These two codes are weighted only for numbers different from zero and the list of weights appears in each of the denominations.

The 2-out-of-5 code allows for the detection of all errors relating to a single bit, but does not allow for the correction of these errors. As the smallest Hamming

distance (or the minimum number of bits that change logic states between two consecutive combinations) is 2, it does not allow for the detection of errors caused by the modification of 2 bits.

|   | 2-out-of-5 code |   |   |   |   |   | 2-out | -of-5 | cod | e |

|---|-----------------|---|---|---|---|---|-------|-------|-----|---|

|   | 0               | 1 | 2 | 3 | 6 | 7 | 4     | 2     | 1   | 0 |

| 0 | 0               | 1 | 1 | 0 | 0 | 1 | 1     | 0     | 0   | 0 |

| 1 | 1               | 1 | 0 | 0 | 0 | 0 | 0     | 0     | 1   | 1 |

| 2 | 1               | 0 | 1 | 0 | 0 | 0 | 0     | 1     | 0   | 1 |

| 3 | 1               | 0 | 0 | 1 | 0 | 0 | 0     | 1     | 1   | 0 |

| 4 | 0               | 1 | 0 | 1 | 0 | 0 | 1     | 0     | 0   | 1 |

| 5 | 0               | 0 | 1 | 1 | 0 | 0 | 1     | 0     | 1   | 0 |

| 6 | 1               | 0 | 0 | 0 | 1 | 0 | 1     | 1     | 0   | 0 |

| 7 | 0               | 1 | 0 | 0 | 1 | 1 | 0     | 0     | 0   | 1 |

| 8 | 0               | 0 | 1 | 0 | 1 | 1 | 0     | 0     | 1   | 0 |

| 9 | 0               | 0 | 0 | 1 | 1 | 1 | 0     | 1     | 0   | 0 |

Table 1.7. Examples of 2-out-of-5 code

Barcodes used to sort out letters are represented as shown in Figure 1.8(a), by a series of parallel lines of variable size. The 0 bit corresponds to a small line and the 1 bit to a large line. Figure 1.8(b) shows another barcode that is used to identify parts and that is composed of parallel lines of variable thickness. The 0 bit is represented by a fine line and the 1 bit by a thick line.

Figure 1.8. Barcodes corresponding to the binary representation 01100

A more compact form of the barcode is obtained by using interleaved 2-out-of-5 encoding. The first code is represented by the black lines (three fine lines and two thick lines) of variable thickness, and the second code by the spacing between the black lines (three narrow spaces and two wide spaces). The code shown in Figure 1.9(a) is a representation of the combination 01100 (black lines) followed by 11000 (spaces between the back lines). In general, the odd combinations are represented by black lines and the even combinations are represented by spaces between the black lines. Figure 1.9(b) shows the barcode corresponding to the sequence 01100, 11000, 10001 and 00110.

An appropriate optical reader is necessary to read each kind of barcode.

Figure 1.9. Barcodes based on an interleaved 2-out-of-5 encoding

# 1.12.3. ASCII code

ASCII code (or American standard code for information interchange) has seven bits allowing for the representation of  $2^7 = 128$  symbols.

Table 1.8 gives the correspondence between certain characters and the decimal and hexadecimal numbers of the ASCII code. The letter N, for example, is represented in ASCII code by the number 78 in decimal and by 4E in hexadecimal. The ASCII code contains 34 characters used to define the format of information and the space between data and to control the transmission and reception of symbols.

# 1.12.4. Other codes

Given the ever-increasing number of characters, other systems of data representation were developed based on the ASCII code:

- EBCDIC (or *extended binary coded decimal interchange code*) is an eight bit code;

- ANSI (or *American national standard institute*) allows for the representation of alphabetical letters from many languages;

– using eight bit words (for UTF-8), 16 bit words (for UTF-16) and 32 bit words (for UTF-32), the universal code, named Unicode (or *Universal code*) represents each character in a unique way by a number. It covers symbols used in most languages.

### 1.13. Codes to protect against errors

There are different types of codes used to detect and correct errors that come up in digital information during transmission or during storage.

# 1.13.1. Parity bit

To facilitate the detection of errors, a supplementary bit or parity bit is often added at the end of a binary word with a fixed number of bits. It allows for the allocation of an odd or even parity depending on whether the total number of 1 bits in the code is odd or even.

VT

FF

CR

SO

SI

SP

Vertical tab

Form feed

Shift out

Shift in

Space

Carriage return

| Dec | Hex | Char    | Dec       | Hex   | Char | Dec | Hex | Char        | Dec    | Hex     | Char |

|-----|-----|---------|-----------|-------|------|-----|-----|-------------|--------|---------|------|

| 0   | 0   | NUL     | 32        | 20    | SP   | 64  | 40  | @           | 96     | 60      | 4    |

| 1   | 1   | SOH     | 33        | 20    | 1    | 65  | 41  | A           | 97     | 61      | а    |

| 2   | 2   | STX     | 34        | 22    |      | 66  | 42  | В           | 98     | 62      | b    |

| 3   | 3   | ETX     | 35        | 23    | #    | 67  | 43  | C           | 99     | 63      | c    |

| 4   | 4   | EOT     | 36        | 24    | \$   | 68  | 44  | D           | 100    | 64      | d    |

| 5   | 5   | ENO     | 37        | 25    | %    | 69  | 45  | E           | 101    | 65      | e    |

| 6   | 6   | ACK     | 38        | 26    | &    | 70  | 46  | F           | 102    | 66      | f    |

| 7   | 7   | BEL     | 39        | 27    | ,    | 71  | 47  | G           | 103    | 67      | g    |

| 8   | 8   | BS      | 40        | 28    | (    | 72  | 48  | Н           | 104    | 68      | h    |

| 9   | 9   | TAB     | 41        | 29    | )    | 73  | 49  | Ι           | 105    | 69      | i    |

| 10  | Â   | LF      | 42        | 2A    | *    | 74  | 4A  | J           | 106    | 6A      | j    |

| 11  | В   | VT      | 43        | 2B    | +    | 75  | 4B  | K           | 107    | 6B      | k    |

| 12  | C   | NP      | 44        | 2C    | ,    | 76  | 4C  | L           | 108    | 6C      | 1    |

| 13  | D   | CR      | 45        | 2D    | -    | 77  | 4D  | М           | 109    | 6D      | m    |

| 14  | E   | SO      | 46        | 2E    |      | 78  | 4E  | N           | 110    | 6E      | n    |

| 15  | F   | SI      | 47        | 2F    | 1    | 79  | 4F  | 0           | 111    | 6F      | 0    |

| 16  | 10  | DLE     | 48        | 30    | 0    | 80  | 50  | P           | 112    | 70      | р    |

| 17  | 11  | DC1     | 49        | 31    | 1    | 81  | 51  | Q           | 113    | 71      | q    |

| 18  | 12  | DC2     | 50        | 32    | 2    | 82  | 52  | R           | 114    | 72      | r    |

| 19  | 13  | DC3     | 51        | 33    | 3    | 83  | 53  | S           | 115    | 73      | s    |

| 20  | 14  | DC4     | 52        | 34    | 4    | 84  | 54  | Т           | 116    | 74      | ť    |

| 21  | 15  | NAK     | 53        | 35    | 5    | 85  | 55  | U           | 117    | 75      | u    |

| 22  | 16  | SYN     | 54        | 36    | 6    | 86  | 56  | v           | 118    | 76      | v    |

| 23  | 17  | ETB     | 55        | 37    | 7    | 87  | 57  | W           | 119    | 77      | w    |

| 24  | 18  | CAN     | 56        | 38    | 8    | 88  | 58  | X           | 120    | 78      | x    |

| 25  | 19  | EM      | 57        | 39    | 9    | 89  | 59  | Y           | 121    | 79      | у    |

| 26  | 1A  | SUB     | 58        | 3A    | :    | 90  | 5A  | Z           | 122    | 7A      | z    |

| 27  | 1B  | ESC     | 59        | 3B    | ;    | 91  | 5B  | [           | 123    | 7B      | {    |

| 28  | 1C  | FS      | 60        | 3C    | <    | 92  | 5C  | Ň           | 124    | 7C      | ì    |

| 29  | 1D  | GS      | 61        | 3D    | =    | 93  | 5D  | 1           | 125    | 7D      | }    |

| 30  | 1E  | RS      | 62        | 3E    | >    | 94  | 5E  | ^           | 126    | 7E      | ~    |

| 31  | 1F  | US      | 63        | 3F    | ?    | 95  | 5F  | -           | 127    | 7F      | DEL  |

|     | NUL | Null    |           |       |      | D   | LE  | Data link e | escape |         |      |

|     | SOH |         | f headin  | g     |      |     | C1  | Device con  | •      |         |      |

|     | STX | Start o |           |       |      |     | C2  | Device con  |        |         |      |

|     | ETX | End of  |           |       |      |     | C3  | Device con  |        |         |      |

|     | EOT |         | transmi   | ssion |      |     | C4  | Device con  |        |         |      |

|     | ENQ | Enquir  |           |       |      |     | AK  | Negative a  |        | dge     |      |

|     | ACK |         | wledge    |       |      |     | YN  | Synchrono   |        | -00     |      |

|     | BEL | Bell    |           |       |      |     | ГВ  | End of trai |        | n block |      |

|     | BS  | Backs   | nace      |       |      |     | AN  | Cancel      |        |         |      |

|     | HT  |         | ontal tab |       |      | EN  |     | End of me   | dium   |         |      |

|     | LF  | Line fe |           |       |      |     | JB  | Substitute  |        |         |      |

|     | 1.1 | Line R  | 1.1       |       |      | 50  |     | Substitute  |        |         |      |

Table 1.8. ASCII codes table

ESC

FS

GS

RS

US

DEL

Escape

Delete

File separator

Group separator

Unit separator

Record separator

EXAMPLE 1.24.- For the word 0101101, the parity bit is 0 (even parity: 4 bits at 1).

For the word 1010001, the parity bit is 1 (odd parity: 3 bits at 1).

Using a single parity bit allows for the detection of all errors that affect only one bit. However, it does not allow for the correction of these errors.

## 1.13.2. Error correcting codes

The reliability of data transmission is generally ensured by using more elaborate codes.

## 1.13.2.1. Block codes

In the block code approach, a certain number of control bits are appended to the message that is structured in blocks of fixed size. In this way, horizontal and vertical parity of data can be verified.

Hamming distance corresponds to the number of bits that vary between two successive words.

EXAMPLE 1.25.– There is a Hamming distance of 3 between the words 111011 and 101010. At least three errors are necessary to make these two words identical.

A possible way of increasing the Hamming distance of a code consists of using several control bits. In this case, a message comprises m bits of data and k control bits.

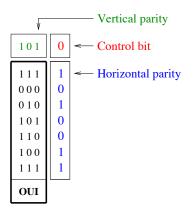

EXAMPLE 1.26.– Represent OUI in ASCII code with odd (horizontal and vertical) parity bits and a crossed parity bit allowing for the indication of the integrity of the (horizontal and vertical) parity bits.

The ASCII codes for the characters of the word OUI are as below:

$79_{10} = 4F_{16} = 1001111_2$  for O  $85_{10} = 55_{16} = 1010101_2$  for U  $73_{10} = 49_{16} = 1001001_2$  for I

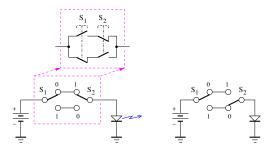

The choice of a two-dimension representation (or a block of bits), as shown in Figure 1.10, allows for the definition of parity bits following the horizontal and vertical direction.

Changing one single bit of the data may bring about a modification of the vertical parity bit, the horizontal parity bit and the crossed parity bit, that is four bits in total. The Hamming distance is, thus, equal to 4.

Figure 1.10. Example of block codes

Such a block code allows for the detection and correction of all errors affecting one single bit. It allows for the detection of all errors affecting 2 and 3 bits, but it presents the inconvenience of requiring the verification of a large number of bits.

# 1.13.2.2. Cyclic codes

Cyclic codes are based on the transcription of binary numbers in polynomial form and the division of polynomials.

EXAMPLE 1.27.– The binary code  $b_{n-1}b_{n-2} \dots b_1 b_0$  corresponds to the polynomial:

$$b_{n-1}x^{n-1} + b_{n-2}x^{n-2} + \dots + b_1x^1 + b_0x^0$$

Let I(x) be the polynomial associated with a message. Supposing that G(x) is an r generator polynomial, the message may be coded by carrying out the following operations:

- multiply I(x) by  $x^r$  (or add r zeros at the end of I(x));

- decompose  $I(x)x^r$  into the form:

$$\frac{I(x)x^{r}}{G(x)} = Q(x) + R(x)$$

[1.26]

- determine the cyclic polynomial T(x):

$$T(x) = I(x)x^r - R(x)$$

[1.27]

The polynomial T(x) is a multiple of G(x). It corresponds to a representation of data to which redundant bits have been appended.

Errors are detected by verifying the divisibility of T(x) by G(x).

NOTE 1.5.– Expressions used for the generator polynomials vary by application areas:

$$-$$

CRC<sup>2</sup>-3-GSM:  $G(x) = x^3 + x + 1;$

- CRC-4-ITU:

$$G(x) = x^4 + x + 1;$$

- CRC-8-CCITT:  $G(x) = x^8 + x^2 + x + 1;$

- CRC-16-CCITT:  $G(x) = x^{16} + x^{12} + x^5 + 1;$

– CRC-32-IEEE:  $G(x)=x^{32}+x^{26}+x^{23}+x^{22}+x^{16}+x^{12}+x^{11}+x^{10}+x^8+x^7+x^5+x^4+x^2+x+1;$

- CRC-64-ISO:

$$G(x) = x^{64} + x^4 + x^3 + x + 1$$

.

EXAMPLE 1.28.– Let us consider the initial information 101101, with which the polynomial  $I(x) = x^5 + x^3 + x^2 + 1$  can be associated. Using the polynomial generator of the form  $G(x) = x^3 + x + 1$  (r = 3), the form of the word to be transmitted, or the polynomial T(x), is determined by proceeding as per the steps:

- multiplication of I(x) by  $x^r$  gives the product  $I(x)x^r = 101101000$ ;

- the division of  $I(x)x^r$  by G(x) yields the quotient Q(x) = 100001 and the remainder R(x) = 011;

- the polynomial T(x) is finally obtained by appending the r bits of R(x) to the end of I(x), that is: T(x) = 101101011.

In the form T(x) + E(x), the information is assumed to be affected by the error E. With a code based on a polynomial generator G(x), we can detect:

- all the single errors (E = 10...0);

- all the double errors (E = 10...010...0) if G(x) has a factor with at least three terms;

- all the errors relating to an odd number of bits (*E* has an odd number of bits at 1) if x + 1 divides G(x);

- all the series of errors ( $E = 0 \dots 01 \dots 10 \dots 0$ ) of length smaller than the degree of R(x);

- most of the long series of errors.

<sup>2</sup> CRC: cyclic redundancy check.

# 1.14. Exercises

**EXERCISE 1.1.-** Conversions

1) Convert the following numbers to binary:

a)  $37_{10}$  b)  $15_{10}$  c)  $187_{10}$  d)  $2\ 014_{10}$  e)  $2\ 016_{10}$  f)  $2.75_{10}$ g)  $25.25_{10}$  h)  $243.3125_{10}$  i)  $0.0625_{10}$  j)  $62_8$  k)  $277_8$  l)  $12.6_8$ m)  $476.35_8$  n)  $92_{16}$  o)  $37FD_{16}$  p)  $7FF_{16}$  q)  $1A6_{16}$  r)  $2C0_{16}$ s)  $1F.C_{16}$  t)  $9.F_{16}$  u)  $A7.EC_{16}$

2) Convert the following numbers to decimal:

a)  $10110_2$  b)  $10001_2$  c)  $10001101_2$  d)  $100100001001_2$  e)  $1111010111_2$ f)  $1011.101_2$  g)  $10011011001.10110_2$  h)  $30_8$  i)  $115_8$  j)  $55.4_8$ k)  $270.54_8$  l)  $356_{16}$  m)  $2AF_{16}$  n)  $2C1_{16}$  o)  $10FF_{16}$ p)  $1FCFA_{16}$  q)  $DADA.C_{16}$  r)  $F.4_{16}$  s)  $EBA.C_{16}$

3) Convert the following numbers to hexadecimal:

a)  $320_{10}$  b)  $6\ 861_{10}$  c)  $65\ 535_{10}$  d)  $100_8$  e)  $62.4_8$  f)  $500.25_8$  g)  $10001101_2$  h)  $1001000110100011110_2$  i)  $10000.1_2$  j)  $100000.0000111_2$  k)  $10001100.01_2$

4) Convert the following BCD numbers to decimal:

a) 0001 1000  $0100_{BCD}$  b) 0100 1001  $0010_{BCD}$ c) 1001 0111 0101  $0010_{BCD}$  d) 0111 0111 0101\_{BCD}

5) How many bits are required for the binary representation of the decimal numbers from 0 to 511?

6) What is the largest number that can be represented in 16-bit binary numeration system?

7) a) Determine the binary representation of the decimal number 10.05 with an absolute error equal to 0.005.

b) Represent the decimal number 0.452 in binary numeration system with a relative error of 0.1%.

EXERCISE 1.2.- Representation of numbers and data

1) Let X be an unsigned n-bit integer. Verify that  $2^n - X$  represents the two's complement of -X.

2) Determine the 8-bit two's complement of the following numbers:  $-1_{10}$ ,  $-17_{10}$ ,  $-128_{10}$ .

Convert the following numbers to decimal:

$01111111_{2C}$ ,  $11001110_{2C}$ ,  $10001000_{2C}$ .

3) Determine the two's complement representations of the numbers  $-63A_{16}$  and  $-8AC_{16}$ .

4) Convert the following numbers to ASCII codes:

a)  $1_{10}$ , b)  $107_{10}$ , c)  $1000010_2$ .

5) Use ASCII code to translate the following expressions:

$X = \cos(.7)$  Y = 256 \* XPRINT "X=", X; "Y=", Y

6) a) Represent the following numbers in single-precision IEEE-754 standard:  $2.75_{10}$ ,  $-417680_{10}$ .

b) Find the decimal number corresponding to each of the following single-precision IEEE-754 representations:

EXERCISE 1.3.- Gray code/binary number conversion

1) Convert the following binary numbers to Gray code:

a) 11011<sub>2</sub> b) 101101<sub>2</sub> c) 11000110<sub>2</sub>

2) Convert each of the following Gray code to binary number:

a) 1010<sub>Gray</sub> b) 00010<sub>Gray</sub> c) 11000010001<sub>Gray</sub>

EXERCISE 1.4.- Correction code

1) Data are to be transmitted, coded by the CRC method, whose polynomial generator is:

$G(x) = x^3 + x + 1$

Determine the bits of the message to be transmitted if the initial message is 101101.

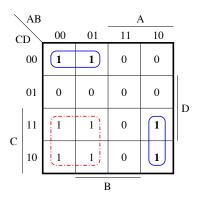

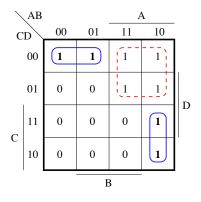

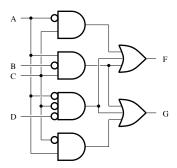

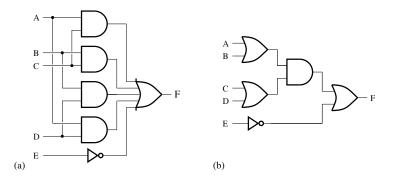

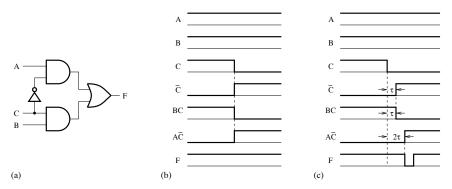

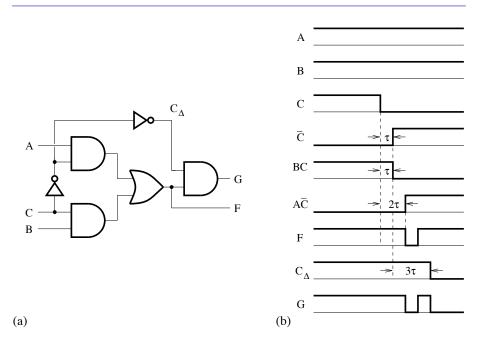

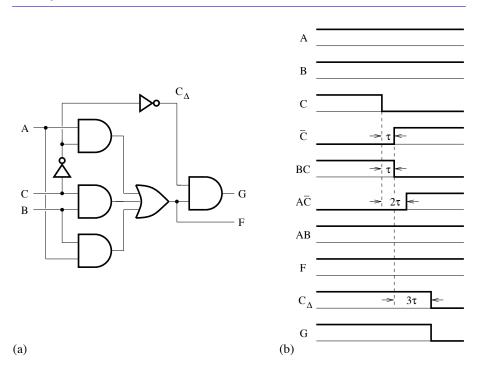

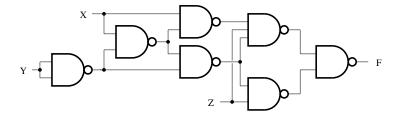

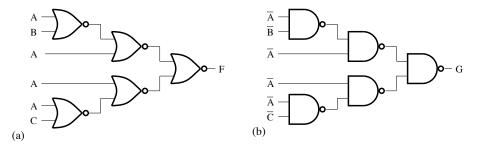

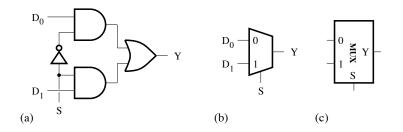

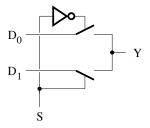

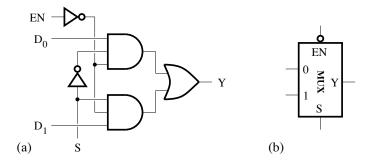

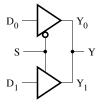

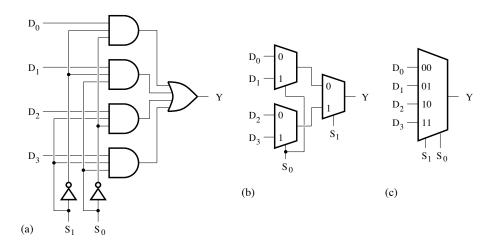

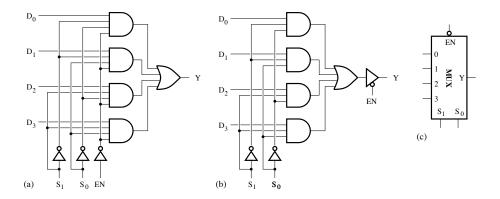

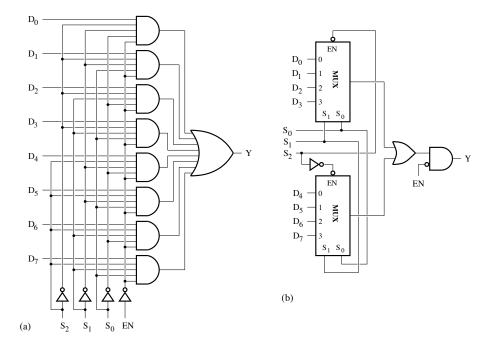

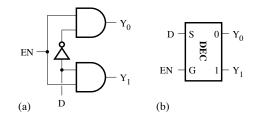

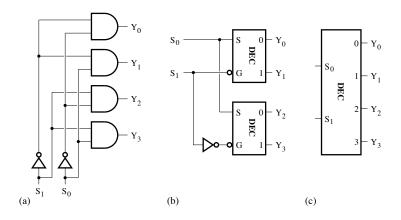

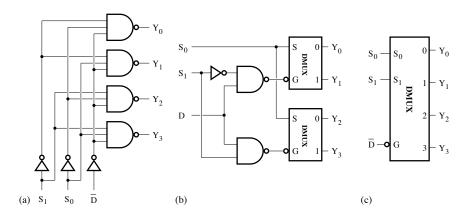

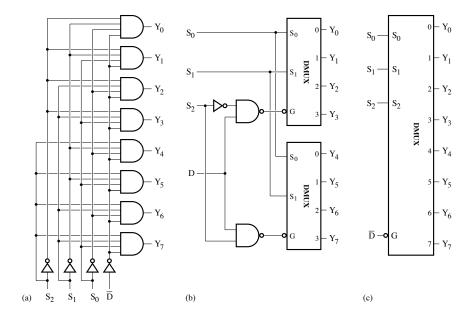

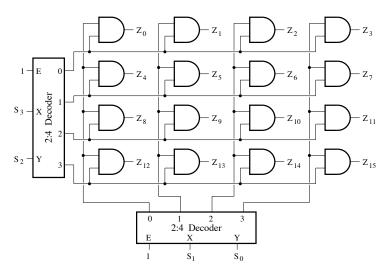

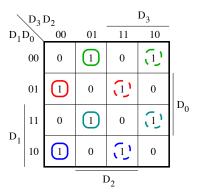

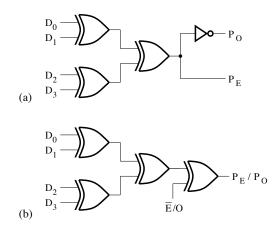

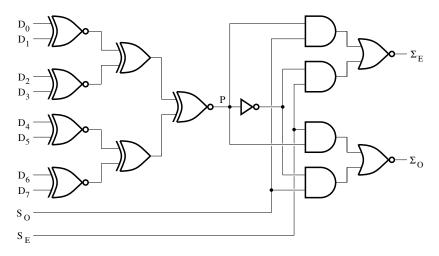

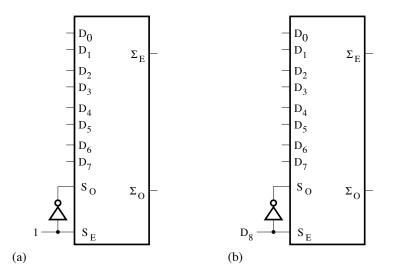

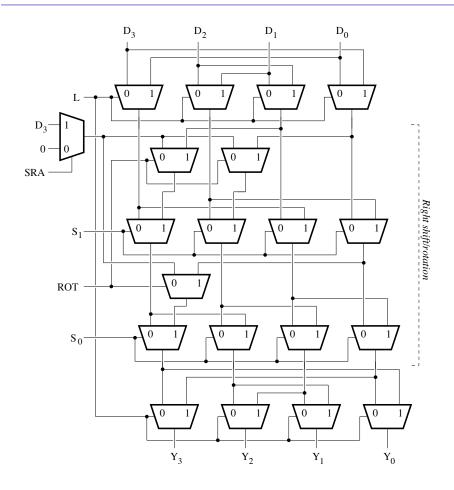

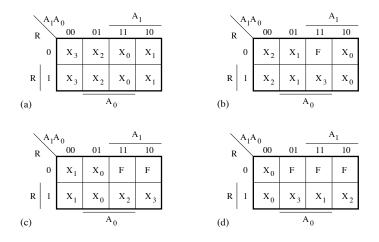

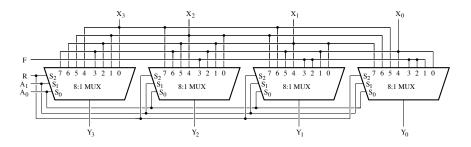

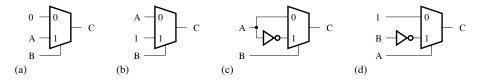

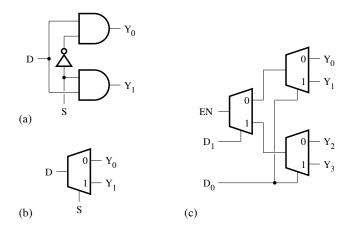

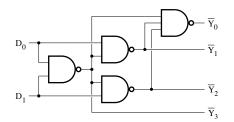

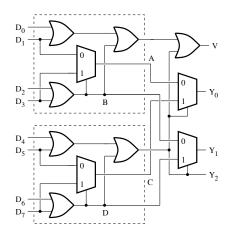

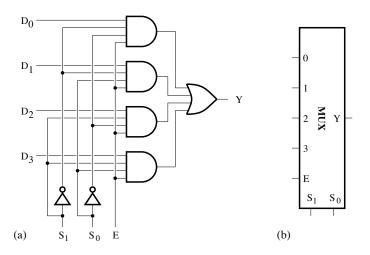

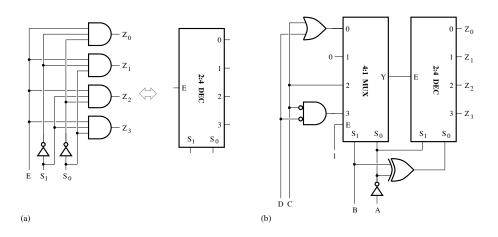

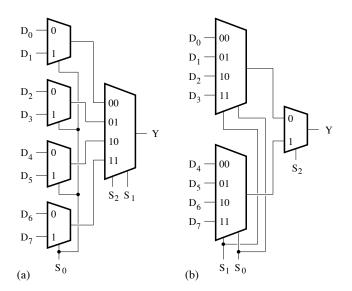

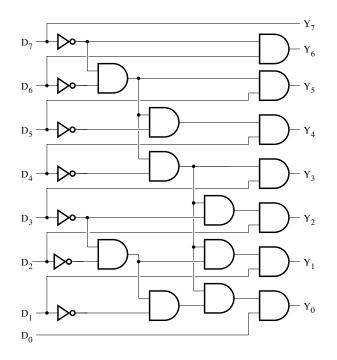

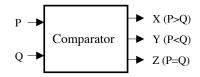

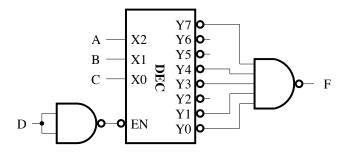

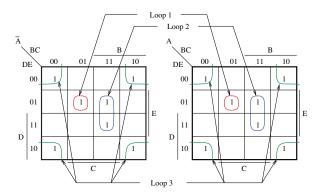

What can we say of the transmission if the received message is 100101 011?