## **ELECTRONICS**

A SYSTEMS APPROACH

At Pearson, we have a simple mission: to help people make more of their lives through learning.

We combine innovative learning technology with trusted content and educational expertise to provide engaging and effective learning experiences that serve people wherever and whenever they are learning.

From classroom to boardroom, our curriculum materials, digital learning tools and testing programmes help to educate millions of people worldwide – more than any other private enterprise.

Every day our work helps learning flourish, and wherever learning flourishes, so do people.

To learn more, please visit us at www.pearson.com/uk

**Neil Storey**

#### PEARSON EDUCATION LIMITED

Edinburgh Gate Harlow CM20 2JE United Kingdom

Tel: +44 (0)1279 623623 Web: www.pearson.com/uk

First published 1992 (print)

Second published 1998 (print)

Third published 2006 (print)

Fourth published 2009 (print)

Fifth published 2013 (print and electronic)

Sixth edition published 2017 (print and electronic)

- © Addison Wesley Publishers Limited 1992 (print)

- © Pearson Education Limited 1998, 2006, 2009 (print)

- © Pearson Education Limited 2013, 2017 (print and electronic)

The right of Neil Storey to be identified as author of this work has been asserted by him in accordance with the Copyright. Designs and Patents Act 1988.

The print publication is protected by copyright. Prior to any prohibited reproduction, storage in a retrieval system, distribution or transmission in any form or by any means, electronic, mechanical, recording or otherwise, permission should be obtained from the publisher or, where applicable, a licence permitting restricted copying in the United Kingdom should be obtained from the Copyright Licensing Agency Ltd, Barnard's Inn, 86 Fetter Lane, London EC4A 1EN.

The ePublication is protected by copyright and must not be copied, reproduced, transferred, distributed, leased, licensed or publicly performed or used in any way except as specifically permitted in writing by the publishers, as allowed under the terms and conditions under which it was purchased, or as strictly permitted by applicable copyright law. Any unauthorised distribution or use of this text may be a direct infringement of the author's and the publisher's rights and those responsible may be liable in law accordingly.

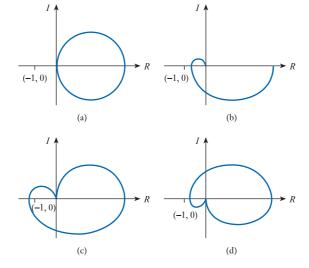

All trademarks used herein are the property of their respective owners. The use of any trademark in this text does not vest in the author or publisher any trademark ownership rights in such trademarks, nor does the use of such trademarks imply any affiliation with or endorsement of this book by such owners.

Pearson Education is not responsible for the content of third-party internet sites.

ISBN: 978-1-292-11406-4 (print) 978-1-292-11411-8 (PDF) 978-1-292-13341-6 (ePub)

#### **British Library Cataloguing-in-Publication Data**

A catalogue record for the print edition is available from the British Library

#### Library of Congress Cataloging-in-Publication Data

Names: Storev. Neil. author.

Title: Electronics: a systems approach / Neil Storey.

$\label{eq:Description: Sixth edition. | Harlow, England; New York: Pearson, 2017.$

Identifiers: LCCN 2016055942 ISBN 9781292114064 (print) | ISBN 9781292133416

(ePub) | ISBN 9781292114118 (PDF)

Subjects: LCSH: Electronic systems. | Electronic circuits.

Classification: LCC TK7870 .S857 2017 | DDC 621.381 – dc23

LC record available at https://lccn.loc.gov/2016055942

10 9 8 7 6 5 4 3 2 1 21 20 19 18 17

Print edition typeset in Ehrhardt MT Pro 10/11.5pt by iEnergizer Aptara®, Ltd. Printed and bound in Malaysia

NOTE THAT ANY PAGE CROSS REFERENCES REFER TO THE PRINT EDITION

## **Brief Contents**

| face                           | xiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16 Operational Amplifiers                          | 278                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| of videos                      | xvii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17 Semiconductors and Diodes                       | 309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| knowledgements                 | xix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18 Field-effect Transistors                        | 336                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <b>+ 1</b>                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19 Bipolar Junction Transistors                    | 385                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20 Power Electronics                               | 449                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21 Internal Circuitry of Operational               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | '                                                  | 475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ·                              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u> </u>                                           | 400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| · ·                            | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • •                                                | 488                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    | 512                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                                  | 527                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| •                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                                  | 586                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <del>-</del>                   | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    | 630                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| • •                            | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | · ·                                                | 688                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Frequency Characteristics of   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    | 753                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AC Circuits                    | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29 Communications                                  | 768                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Transient Behaviour            | 168                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30 System Design                                   | 796                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Electric Motors and Generators | 184                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ct 2                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Appendices                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| · • —                          | 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A Symbols                                          | 808                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Electronic Systems             | 201                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | B SI units and prefixes                            | 811                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| •                              | 209                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C Op-amp circuits                                  | 813                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

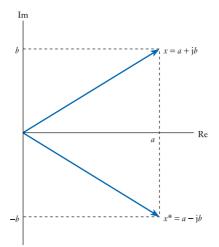

| Actuators                      | 230                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D Complex numbers                                  | 818                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

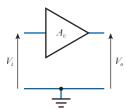

| Amplification                  | 241                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | E Answers to selected exercises                    | 823                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Control and Feedback           | 261                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Index                                              | 826                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                | face cof videos cnowledgements  rt 1  ECTRICAL CIRCUITS AND MPONENTS  Basic Electrical Circuits and Components Measurement of Voltages and Currents Resistance and DC Circuits Capacitance and Electric Fields Inductance and Magnetic Fields Alternating Voltages and Currents Power in AC Circuits Frequency Characteristics of AC Circuits Transient Behaviour Electric Motors and Generators  rt 2  ECTRONIC SYSTEMS  Electronic Systems Sensors Actuators Amplification Control and Feedback | cof videos xvii xix xix xix xix xix xix xix xix xi | xvii 17 Semiconductors and Diodes xiowledgements xix 18 Field-effect Transistors 19 Bipolar Junction Transistors 20 Power Electronics 21 Internal Circuitry of Operational Amplifiers 22 Noise and Electromagnetic Compatibility 23 Positive Feedback, Oscillators and Stability 24 Digital Systems 25 Sequential Logic 26 Digital Devices 27 Implementing Digital Systems 28 Data Acquisition and Conversion 29 Communications 30 System Design 29 Compatibility 21 Capacitance and Generators 20 Power in AC Circuits 21 Positive Feedback, Oscillators and Stability 24 Digital Systems 25 Sequential Logic 26 Digital Devices 27 Implementing Digital Systems 28 Data Acquisition and Conversion 29 Communications 30 System Design 29 Communications 30 System Design 29 Communications 30 System Design 201 Sensors 202 Cop-amp circuits 203 Cop-amp circuits 204 Digital Systems 205 Cop-amp circuits 205 Cop-amp circuits 206 Digital Systems 207 Cop-amp circuits 207 Complex numbers 208 Digital Systems 209 Complex numbers 209 Complex numbers 209 Complex numbers 201 E Answers to selected exercises |

## Contents

| Preface                                                                                      | xiii   | 3 Resistance and DC Circuits                    | 42  |

|----------------------------------------------------------------------------------------------|--------|-------------------------------------------------|-----|

| List of videos                                                                               | xvii   | 3.1 Introduction                                | 42  |

| Acknowledgements                                                                             | xix    | 3.2 Current and charge                          | 42  |

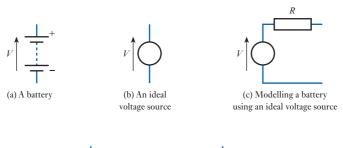

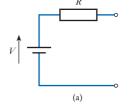

| 3                                                                                            |        | 3.3 Voltage sources                             | 43  |

|                                                                                              |        | 3.4 Current sources                             | 44  |

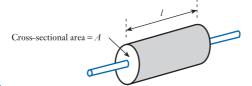

| Part 1                                                                                       |        | 3.5 Resistance and Ohm's law                    | 44  |

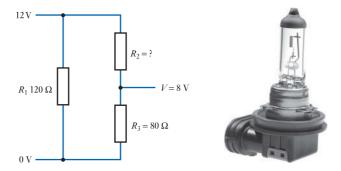

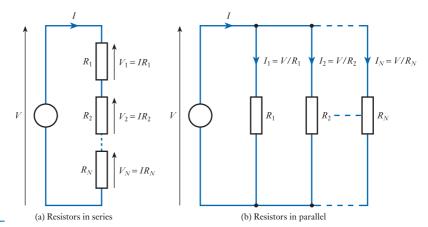

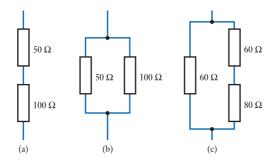

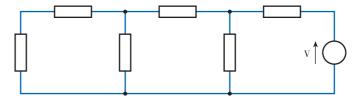

| ELECTRICAL CIRCUITS AND                                                                      |        | 3.6 Resistors in series and parallel            | 45  |

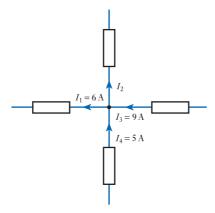

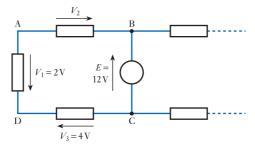

| COMPONENTS                                                                                   | 1      | 3.7 Kirchhoff's laws                            | 47  |

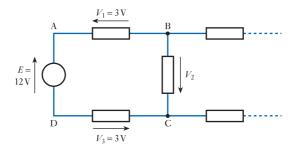

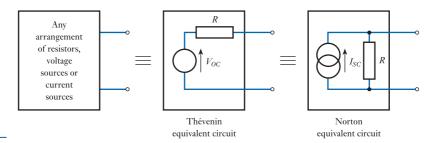

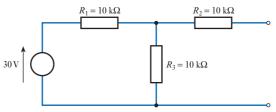

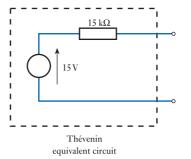

|                                                                                              |        | 3.8 Thévenin's theorem and Norton's             | 49  |

| 1 Basic Electrical Circuits and                                                              |        | theorem 3.9 Superposition                       | 53  |

|                                                                                              | 3      | 3.10 Nodal analysis                             | 56  |

| Components                                                                                   |        | 3.11 Mesh analysis                              | 58  |

| 1.1 Introduction                                                                             | 3      | 3.12 Solving simultaneous circuit equations     | 62  |

| 1.2 Système International units                                                              | 4      | 3.13 Choice of techniques                       | 62  |

| 1.3 Common prefixes                                                                          | 5      | Further study                                   | 63  |

| <ul><li>1.4 Electrical circuits</li><li>1.5 Direct current and alternating current</li></ul> | 5<br>8 | Key points                                      | 63  |

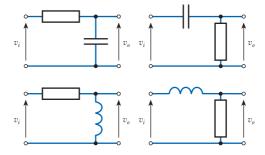

| 1.6 Resistors, capacitors and inductors                                                      | 8      | Exercises                                       | 64  |

| 1.7 Ohm's law                                                                                | 9      | 2,6161666                                       | 0 1 |

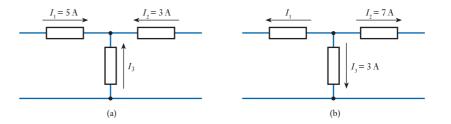

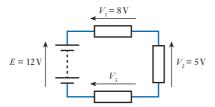

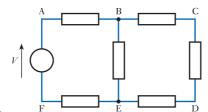

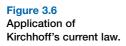

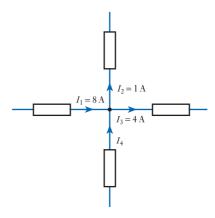

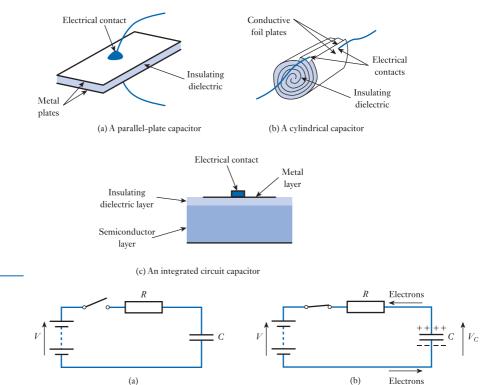

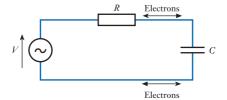

| 1.8 Kirchhoff's laws                                                                         | 10     | 4 Capacitance and Electric Fields               | 69  |

| 1.9 Power dissipation in resistors                                                           | 11     | 4.1 Introduction                                | 69  |

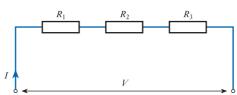

| 1.10 Resistors in series                                                                     | 12     | 4.1 Introduction 4.2 Capacitors and capacitance | 69  |

| 1.11 Resistors in parallel                                                                   | 12     | 4.3 Capacitors and alternating voltages and     | 09  |

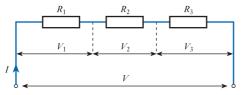

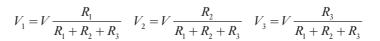

| 1.12 Resistive potential dividers                                                            | 13     | currents                                        | 71  |

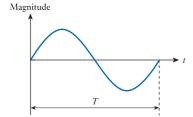

| 1.13 Sinusoidal quantities                                                                   | 15     | 4.4 The effect of a capacitor's dimensions      | , , |

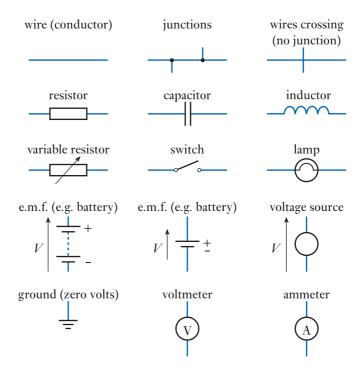

| 1.14 Circuit symbols                                                                         | 16     | on its capacitance                              | 72  |

| Further study                                                                                | 17     | 4.5 Electric field strength and electric flux   |     |

| Key points                                                                                   | 17     | density                                         | 73  |

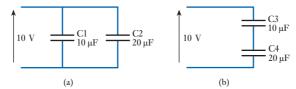

| Exercises                                                                                    | 18     | 4.6 Capacitors in series and in parallel        | 75  |

|                                                                                              |        | 4.7 Relationship between voltage and            |     |

| 2 Measurement of Voltages and                                                                |        | current in a capacitor                          | 77  |

| Currents                                                                                     | 20     | 4.8 Sinusoidal voltages and currents            | 78  |

| 2.1 Introduction                                                                             | 20     | 4.9 Energy stored in a charged capacitor        | 79  |

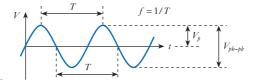

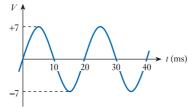

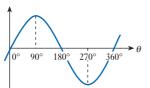

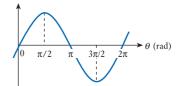

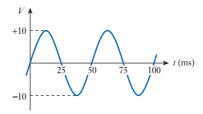

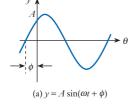

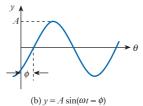

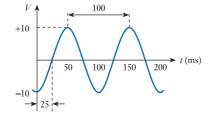

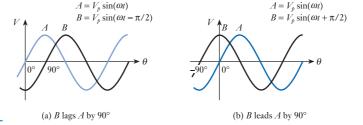

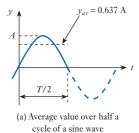

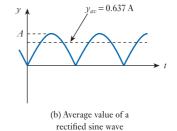

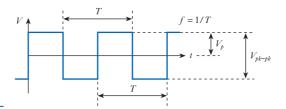

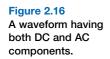

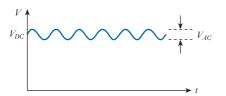

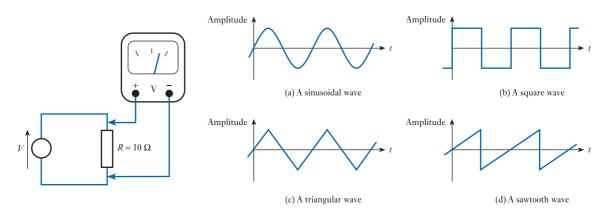

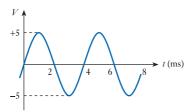

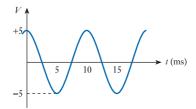

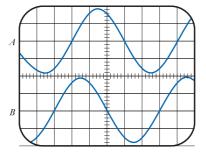

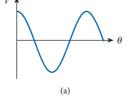

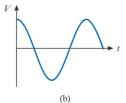

| 2.2 Sine waves                                                                               | 21     | 4.10 Circuit symbols                            | 79  |

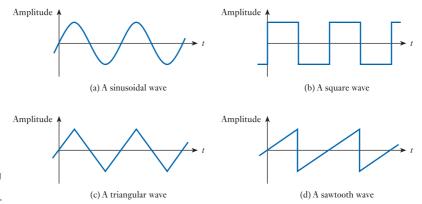

| 2.3 Square waves                                                                             | 28     | Further study                                   | 80  |

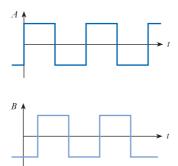

| 2.4 Measuring voltages and currents                                                          | 29     | Key points                                      | 80  |

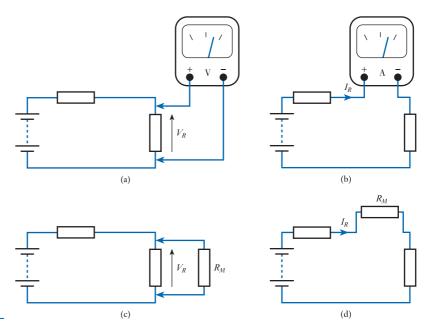

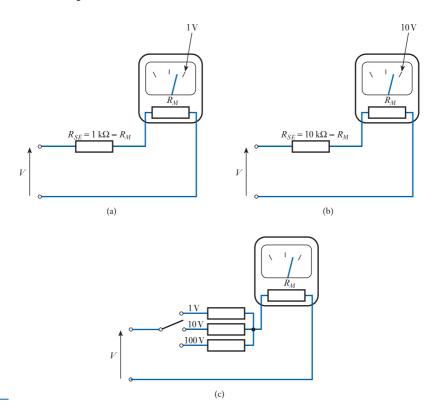

| 2.5 Analogue ammeters and voltmeters                                                         | 30     | Exercises                                       | 81  |

| 2.6 Digital multimeters                                                                      | 34     |                                                 |     |

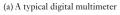

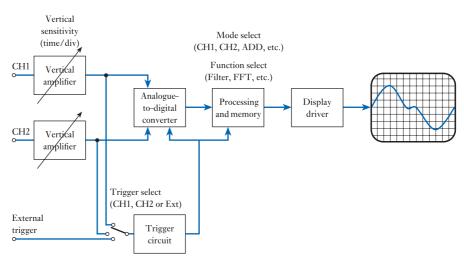

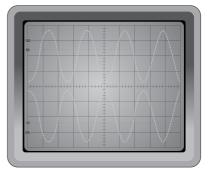

| 2.7 Oscilloscopes                                                                            | 35     | 5 Inductance and Magnetic Fields                | 83  |

| Further study                                                                                | 38     | 5.1 Introduction                                | 83  |

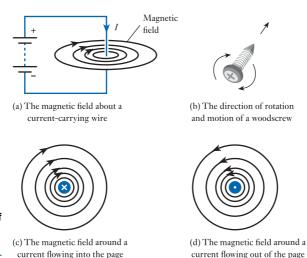

| Key points                                                                                   | 38     | 5.2 Electromagnetism                            | 83  |

| Exercises                                                                                    | 39     | 5.3 Reluctance                                  | 87  |

|                                                                                              |        |                                                 |     |

#### viii Contents

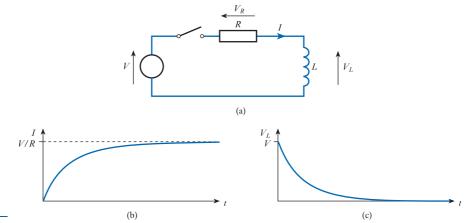

| 5.4   | Inductance                          | 87  | 8.3 The decibel (dB)                      | 138 |

|-------|-------------------------------------|-----|-------------------------------------------|-----|

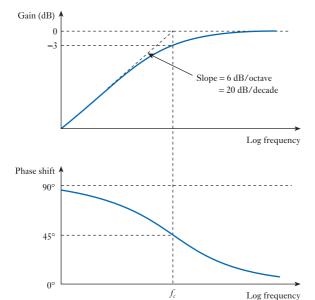

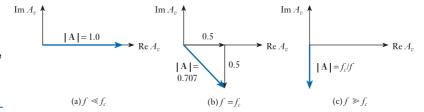

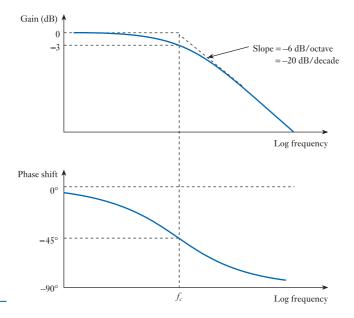

| 5.5   | Self-inductance                     | 88  | 8.4 Frequency response                    | 140 |

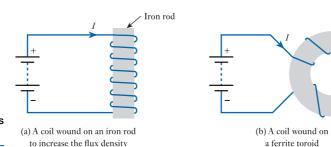

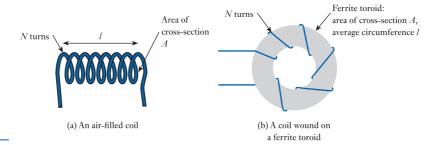

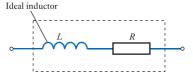

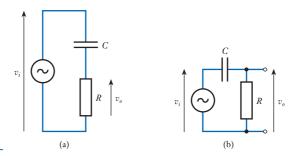

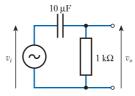

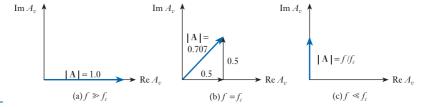

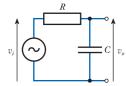

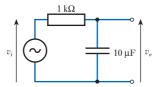

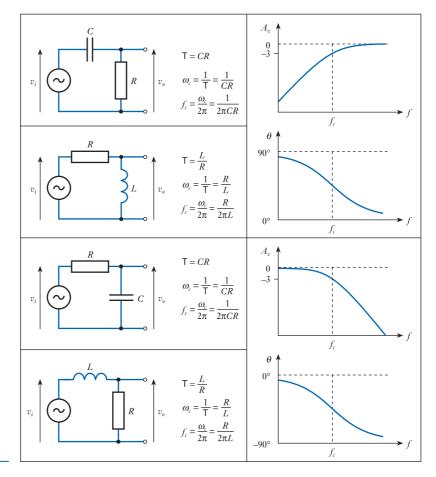

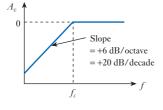

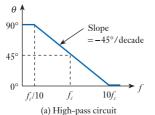

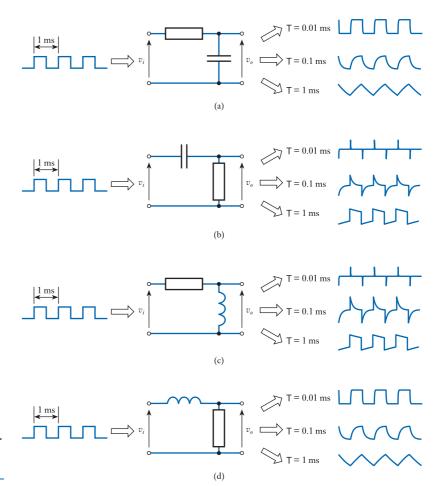

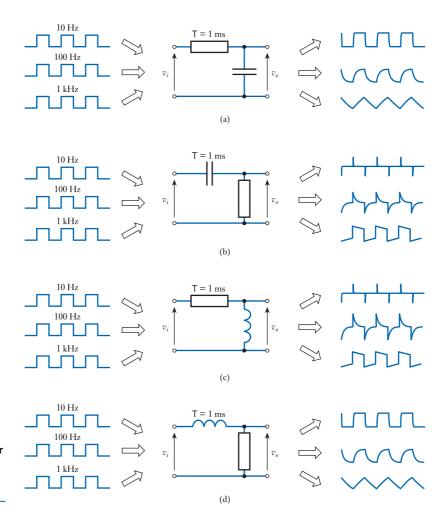

| 5.6   | Inductors                           | 89  | 8.5 A high-pass RC network                | 141 |

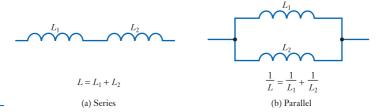

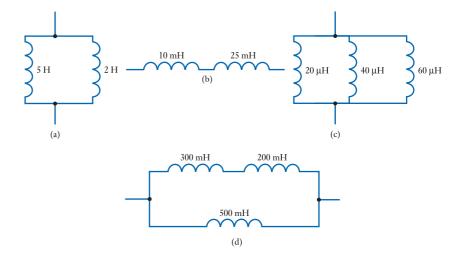

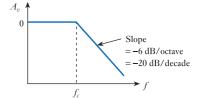

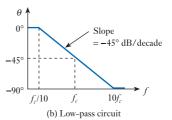

| 5.7   | Inductors in series and in parallel | 91  | 8.6 A low-pass RC network                 | 145 |

| 5.8   | Relationship between voltage and    |     | 8.7 A low-pass RL network                 | 148 |

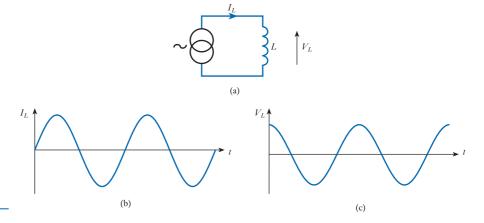

|       | current in an inductor              | 91  | 8.8 A high-pass <i>RL</i> network         | 149 |

| 5.9   | Sinusoidal voltages and currents    | 93  | 8.9 A comparison of RC and RL             |     |

|       | Energy storage in an inductor       | 94  | networks                                  | 150 |

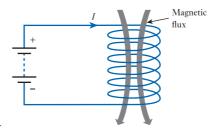

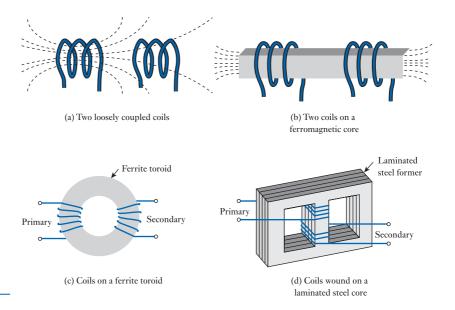

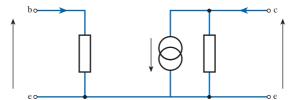

|       | Mutual inductance                   | 94  | 8.10 Bode diagrams                        | 151 |

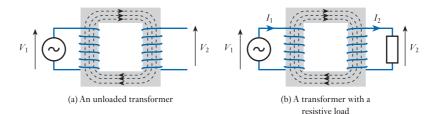

|       | Transformers                        | 96  | 8.11 Combining the effects of several     |     |

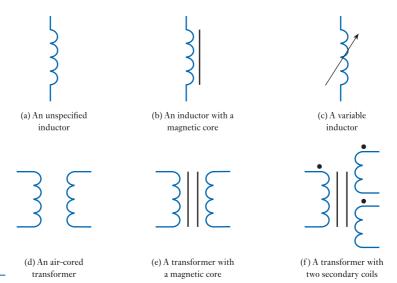

|       | Circuit symbols                     | 97  | stages                                    | 152 |

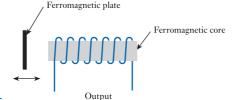

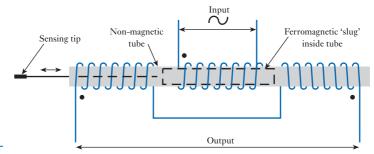

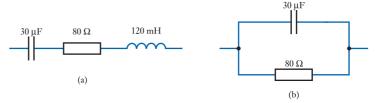

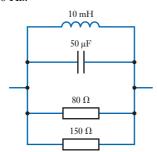

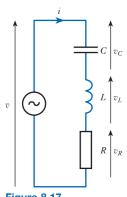

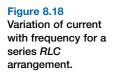

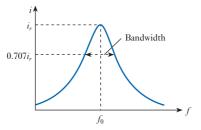

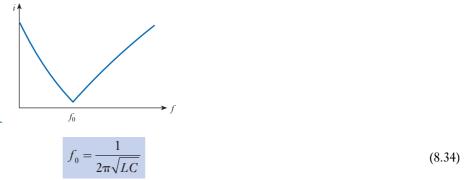

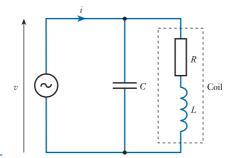

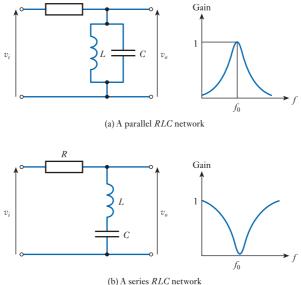

| 5.14  | The use of inductance in sensors    | 98  | 8.12 RLC circuits and resonance           | 154 |

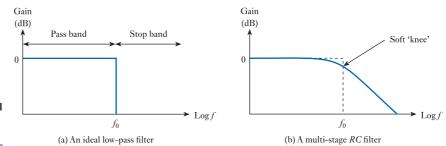

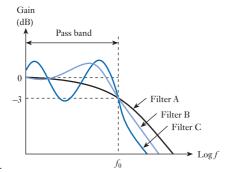

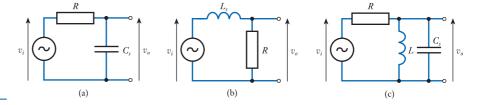

| Furtl | ner study                           | 99  | 8.13 Filters                              | 159 |

| Key   | points                              | 100 | 8.14 Stray capacitance and                |     |

| Exer  | cises                               | 100 | inductance                                | 163 |

| •     |                                     |     | Further study                             | 164 |

|       | Alternating Voltages and            |     | Key points                                | 164 |

| C     | Currents                            | 103 | Exercises                                 | 165 |

| 6.1   | Introduction                        | 103 |                                           |     |

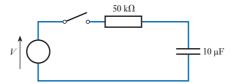

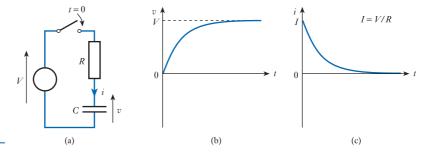

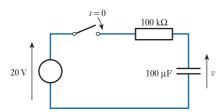

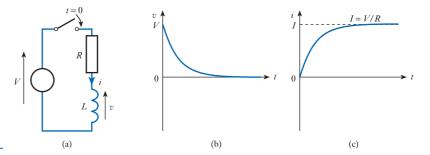

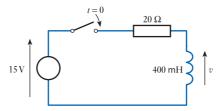

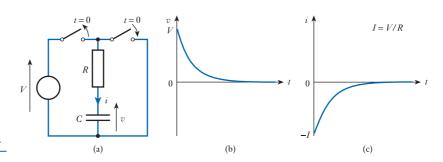

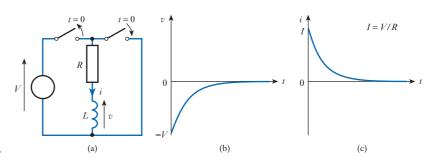

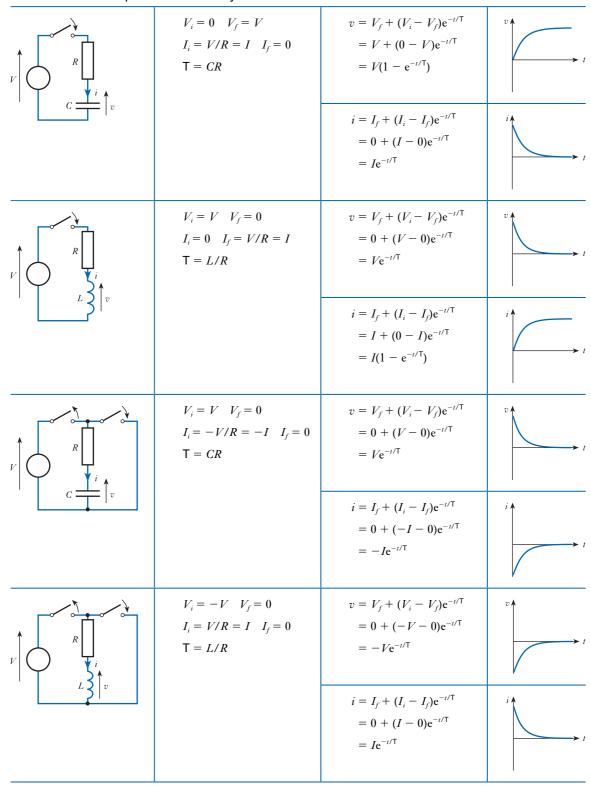

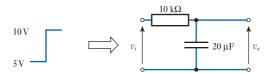

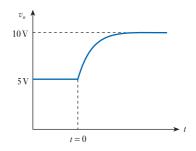

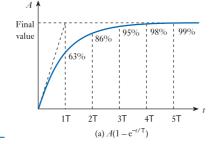

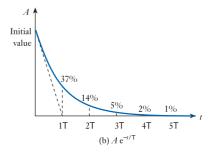

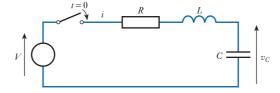

| 6.2   | Relationship between voltage        |     | 9 Transient Behaviour                     | 168 |

|       | and current                         | 104 | 9.1 Introduction                          | 168 |

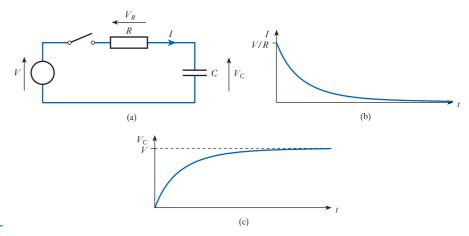

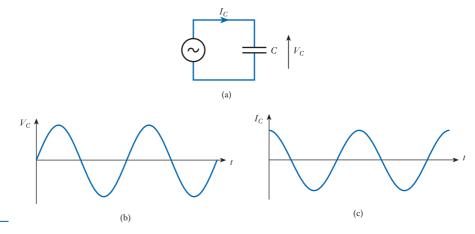

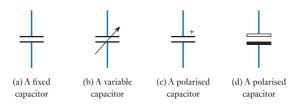

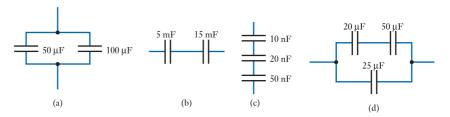

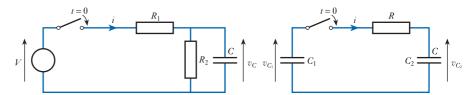

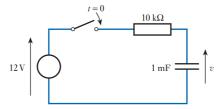

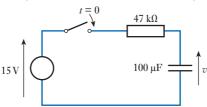

| 6.3   | Reactance of inductors and          |     | 9.2 Charging of capacitors and energising | 100 |

|       | capacitors                          | 105 | of inductors                              | 168 |

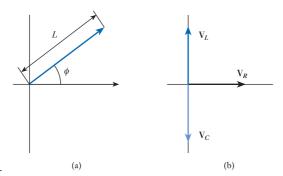

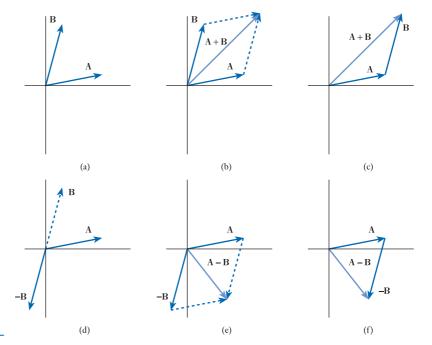

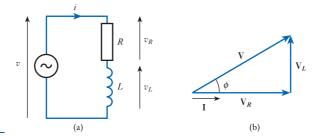

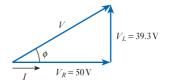

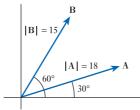

| 6.4   | Phasor diagrams                     | 108 | 9.3 Discharging of capacitors and         | 100 |

| 6.5   | Impedance                           | 114 | de-energising of inductors                | 172 |

| 6.6   | Complex notation                    | 115 | 9.4 Generalised response of first-order   | 172 |

| Furtl | ner study                           | 121 | systems                                   | 174 |

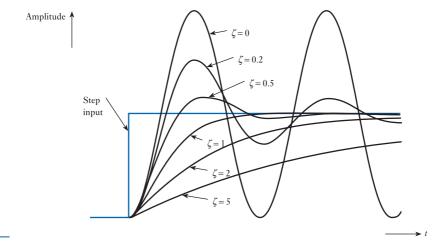

|       | points                              | 121 | 9.5 Second-order systems                  | 179 |

|       | rcises                              | 122 | 9.6 Higher-order systems                  | 180 |

|       |                                     |     | Further study                             | 180 |

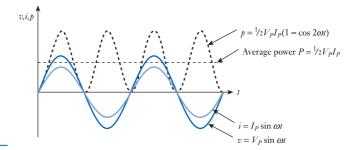

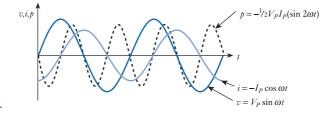

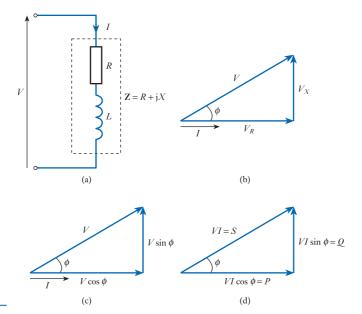

| 7 P   | Power in AC Circuits                | 125 | Key points                                | 181 |

| 7.1   | Introduction                        | 125 | Exercises                                 | 181 |

| 7.2   | Power dissipation in resistive      |     | Exorologo                                 | 101 |

|       | components                          | 125 |                                           |     |

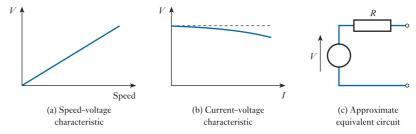

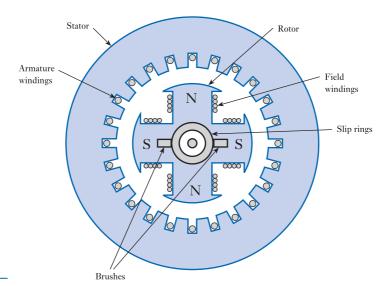

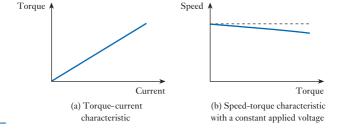

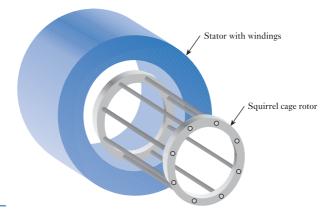

| 7.3   | Power in capacitors                 | 126 | 10 Electric Motors and                    |     |

| 7.4   | Power in inductors                  | 127 | Generators                                | 184 |

| 7.5   | Power in circuits with resistance   |     | 10.1 Introduction                         | 184 |

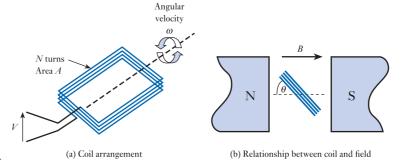

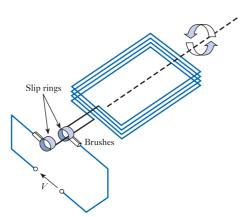

|       | and reactance                       | 127 | 10.2 A simple AC generator                | 184 |

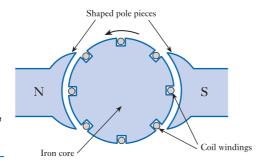

| 7.6   | Active and reactive power           | 129 | 10.3 A simple DC generator                | 186 |

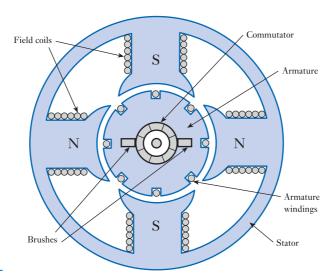

| 7.7   | Power factor correction             | 131 | 10.4 DC generators or dynamos             | 188 |

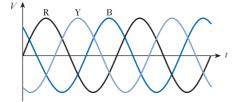

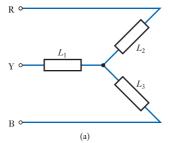

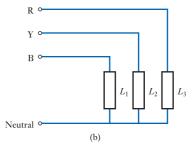

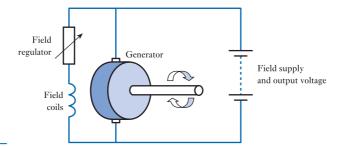

| 7.8   | Three-phase systems                 | 132 | 10.5 AC generators or alternators         | 189 |

| 7.9   | Power measurement                   | 133 | 10.6 DC motors                            | 190 |

| Furtl | ner study                           | 133 | 10.7 AC motors                            | 191 |

|       | points                              | 134 | 10.8 Universal motors                     | 193 |

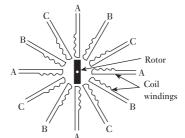

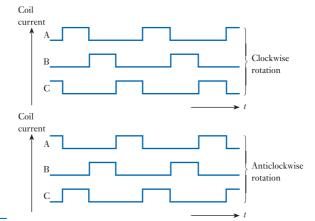

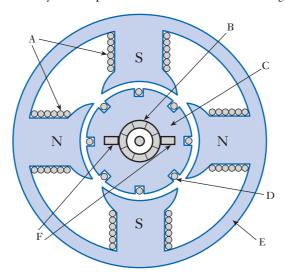

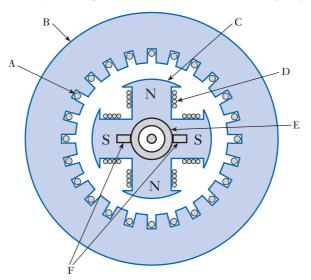

| _     | cises                               | 134 | 10.9 Stepper motors                       | 193 |

|       |                                     |     | 10.10 Electrical machines -               |     |

| 8 F   | requency Characteristics            |     | a summary                                 | 195 |

| 0     | f AC Circuits                       | 136 | Further study                             | 196 |

| 8.1   | Introduction                        | 136 | Key points                                | 196 |

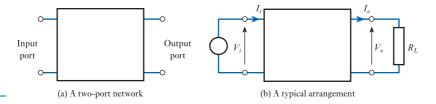

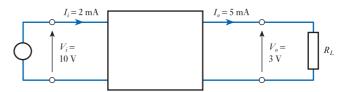

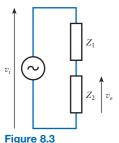

| 8.2   | Two-port networks                   | 136 | Exercises                                 | 196 |

|       |                                     |     |                                           |     |

| Par    | t 2                                |     | 14.5<br>14.6 | Output power                      | 250        |

|--------|------------------------------------|-----|--------------|-----------------------------------|------------|

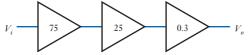

|        | CTRONIC SYSTEMS                    | 199 |              | Power gain                        | 253        |

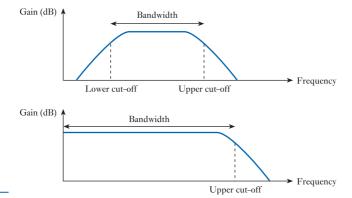

|        |                                    |     | 14.7         | Frequency response and bandwidth  | 254<br>255 |

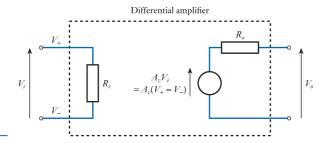

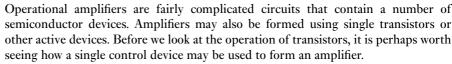

|        |                                    |     | 14.8         | Differential amplifiers           |            |

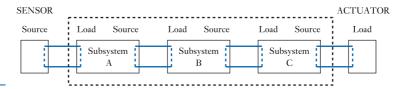

| 11 E   | lectronic Systems                  | 201 | 14.9         | Simple amplifiers                 | 257        |

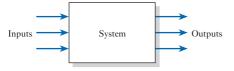

| 11.1   | Introduction                       | 201 |              | er study                          | 258        |

| 11.2   | A systems approach to engineering  | 202 | Key p        |                                   | 258        |

| 11.3   | Systems                            | 202 | Exerc        | ises                              | 259        |

| 11.4   | System inputs and outputs          | 203 |              |                                   |            |

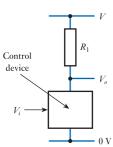

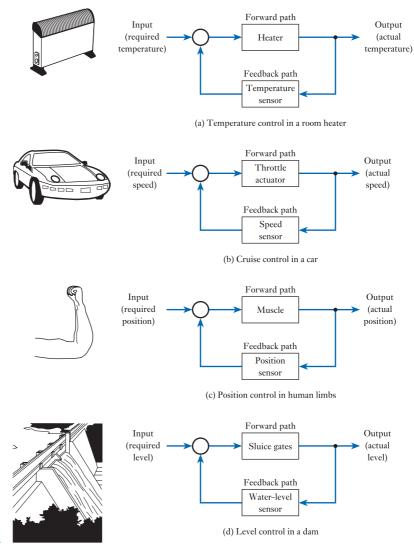

| 11.5   | Physical quantities and electrical |     | 15 C         | Control and Feedback              | 261        |

|        | signals                            | 204 | 15.1         | Introduction                      | 261        |

| 11.6   | System block diagrams              | 206 | 15.2         | Open-loop and closed-loop         | 201        |

|        | er study                           | 207 |              | systems                           | 262        |

| Key p  |                                    | 208 | 15.3         | Automatic control systems         | 263        |

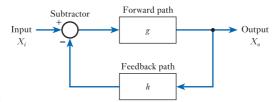

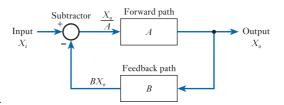

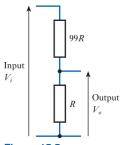

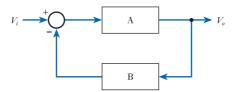

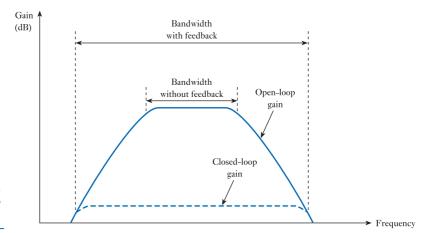

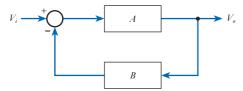

| Exerci |                                    | 208 | 15.4         | Feedback systems                  | 265        |

| LXOIO  | 000                                | 200 | 15.5         | Negative feedback                 | 267        |

| 12 6   | ensors                             | 209 | 15.6         | The effects of negative feedback  | 271        |

|        |                                    |     | 15.7         | Negative feedback – a summary     | 274        |

| 12.1   | Introduction                       | 209 | Furthe       | er study                          | 274        |

| 12.2   | Describing sensor performance      | 210 | Key p        |                                   | 275        |

| 12.3   | Temperature sensors                | 212 | Exerc        |                                   | 275        |

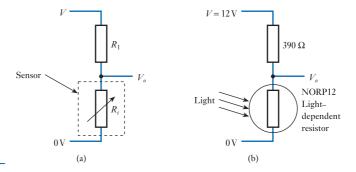

| 12.4   | Light sensors                      | 213 | LXGIG        | 1000                              | 270        |

| 12.5   | Force sensors                      | 216 | 40.0         | No avational Amenitions           | 070        |

| 12.6   | Displacement sensors               | 217 | 16 C         | Operational Amplifiers            | 278        |

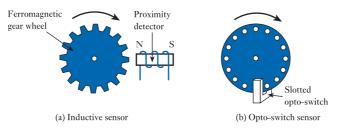

| 12.7   | Motion sensors                     | 222 | 16.1         | Introduction                      | 278        |

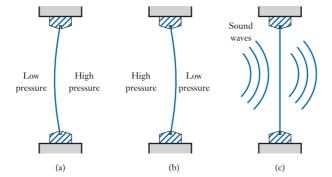

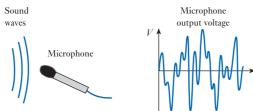

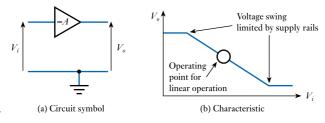

| 12.8   | Sound sensors                      | 223 | 16.2         | An ideal operational amplifier    | 280        |

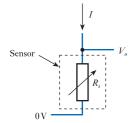

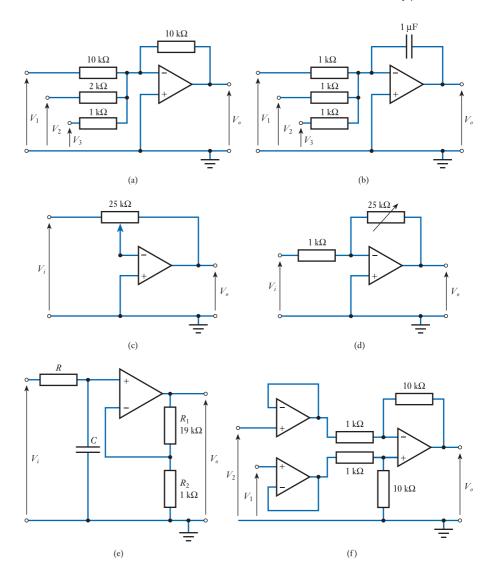

| 12.9   | Sensor interfacing                 | 224 | 16.3         | Some basic operational amplifier  |            |

|        | Sensors – a summary                | 227 |              | circuits                          | 280        |

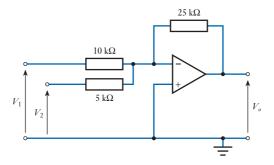

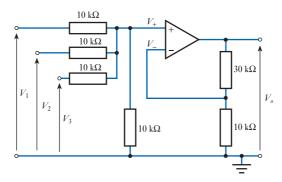

| Furthe | er study                           | 227 | 16.4         | Some other useful circuits        | 285        |

| Key p  | oints                              | 228 | 16.5         | Real operational amplifiers       | 294        |

| Exerci | ses                                | 228 | 16.6         | Selecting component values for    |            |

|        |                                    |     |              | op-amp circuits                   | 298        |

| 13 A   | ctuators                           | 230 | 16.7         | The effects of feedback on op-amp |            |

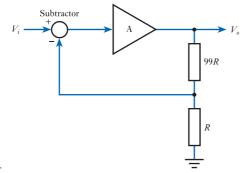

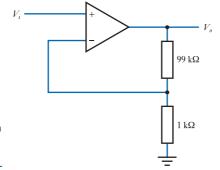

| 13.1   | Introduction                       | 230 |              | circuits                          | 299        |

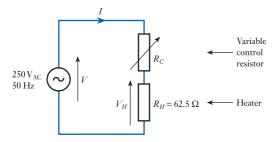

| 13.2   | Heat actuators                     | 230 | Furthe       | er study                          | 302        |

| 13.3   | Light actuators                    | 231 | Key p        | oints                             | 303        |

| 13.4   | Force, displacement and motion     |     | Exerc        | ises                              | 304        |

|        | actuators                          | 233 |              |                                   |            |

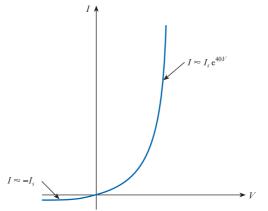

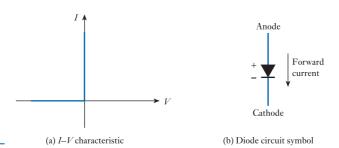

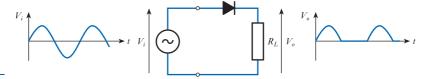

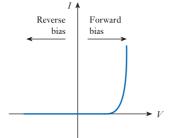

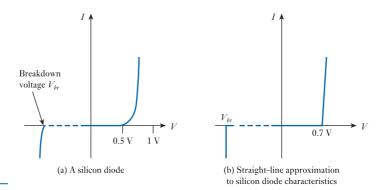

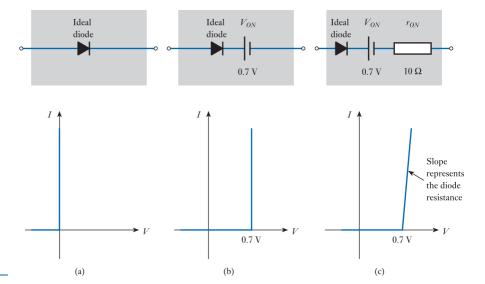

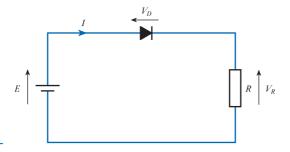

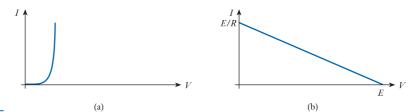

| 13.5   | Sound actuators                    | 235 | 17.9         | Semiconductors and Diodes         | 309        |

| 13.6   | Actuator interfacing               | 236 |              |                                   |            |

| 13.7   | Actuators – a summary              | 237 | 17.1         | Introduction                      | 309        |

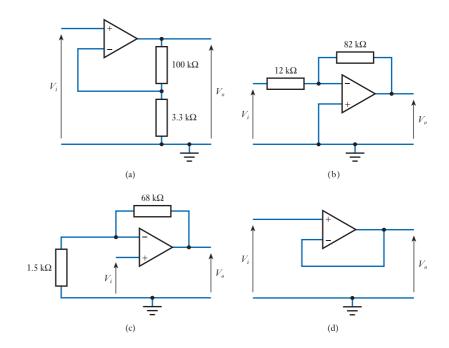

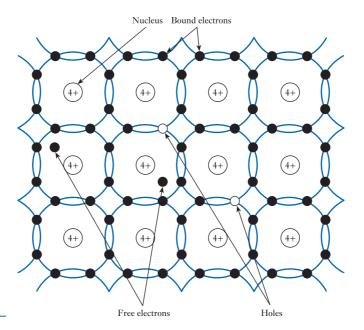

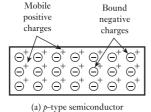

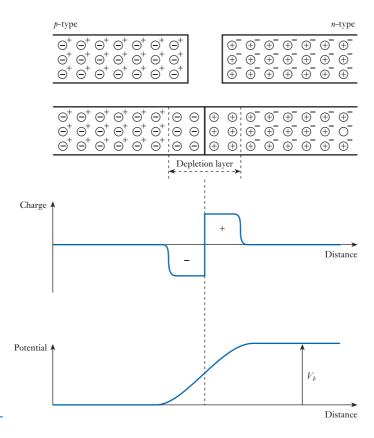

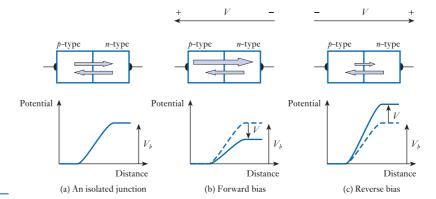

| Furthe | er study                           | 239 | 17.2         | Electrical properties of solids   | 309        |

| Key p  |                                    | 239 | 17.3         | Semiconductors                    | 310        |

| Exerci |                                    | 239 | 17.4         | pn junctions                      | 312        |

| LXCICI | 363                                | 200 | 17.5         | Diodes                            | 315        |

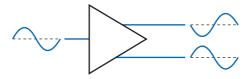

| 14 ^   | mplification                       | 241 | 17.6         | Semiconductor diodes              | 316        |

|        | mplification                       | 241 | 17.7         | Special-purpose diodes            | 324        |

| 14.1   | Introduction                       | 241 | 17.8         | Diode circuits                    | 328        |

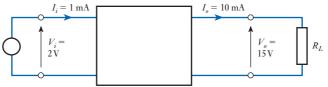

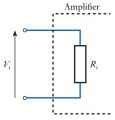

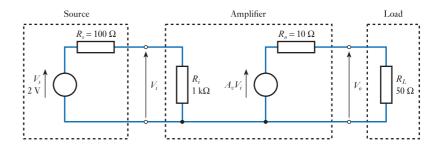

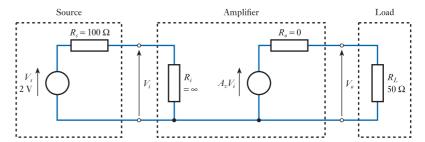

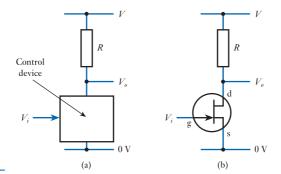

| 14.2   | Electronic amplifiers              | 243 |              | er study                          | 333        |

| 14.3   | Sources and loads                  | 244 | Key p        |                                   | 333        |

| 14.4   | Equivalent circuit of an amplifier | 246 | Exerc        | ises                              | 334        |

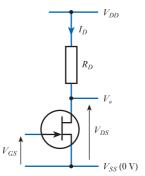

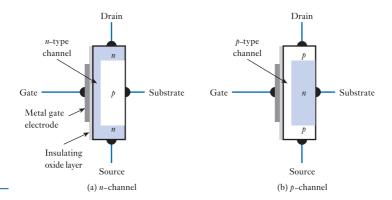

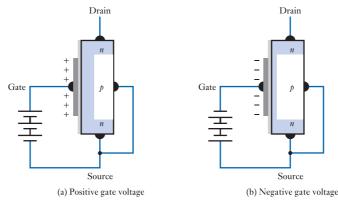

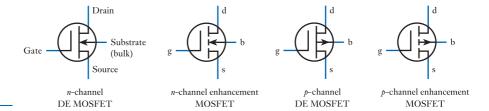

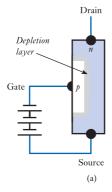

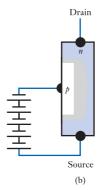

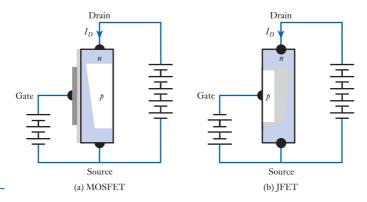

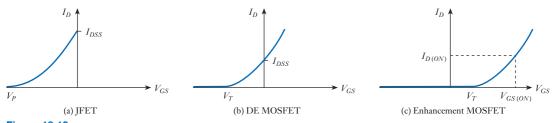

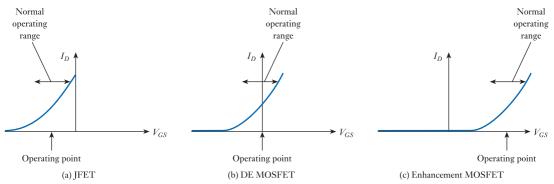

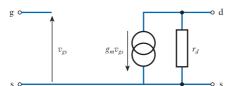

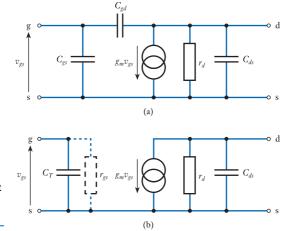

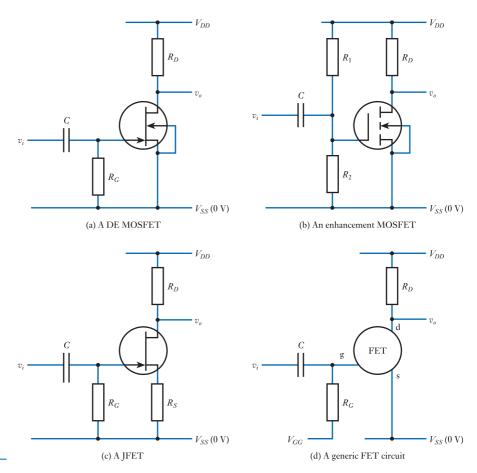

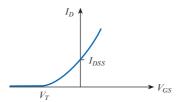

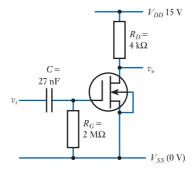

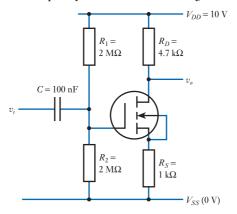

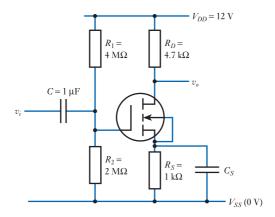

| 18 F   | ield-effect Transistors                 | 336             | 22 Noise and Electromagnetic              |     |

|--------|-----------------------------------------|-----------------|-------------------------------------------|-----|

| 18.1   | Introduction                            | 336             | Compatibility                             | 488 |

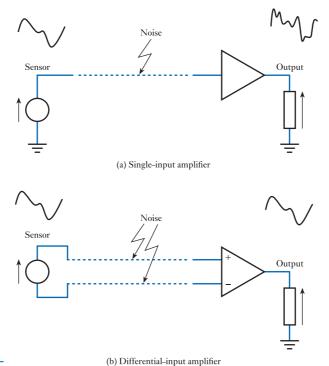

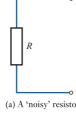

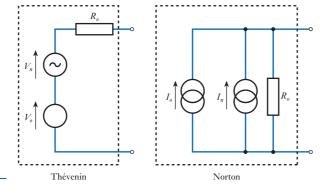

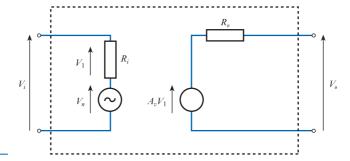

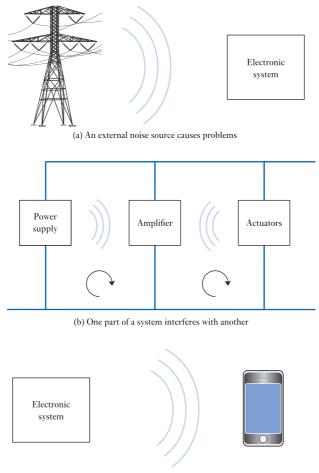

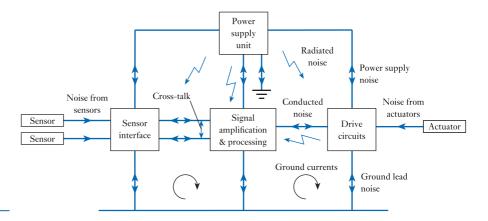

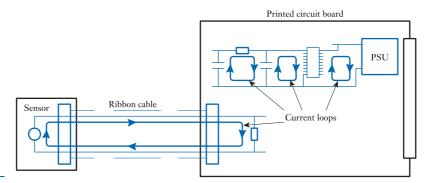

| 18.2   | An overview of field-effect transistors | 336             | 22.1 Introduction                         | 488 |

| 18.3   | Insulated-gate field-effect transistors | 338             | 22.2 Noise sources                        | 489 |

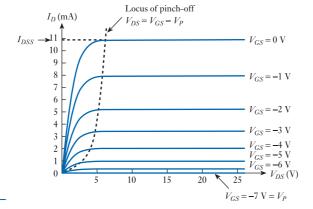

| 18.4   | Junction-gate field-effect transistors  | 340             | 22.3 Representing noise sources within    |     |

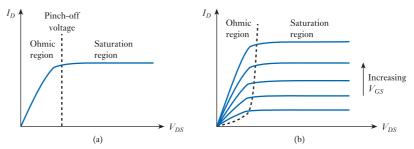

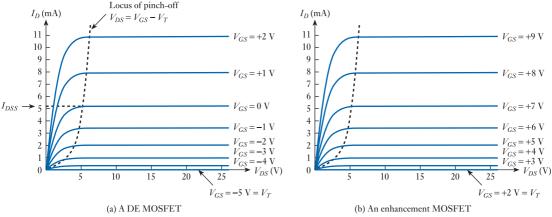

| 18.5   | FET characteristics                     | 342             | equivalent circuits                       | 492 |

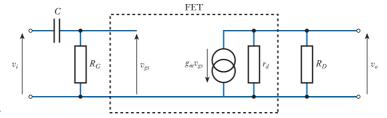

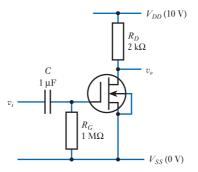

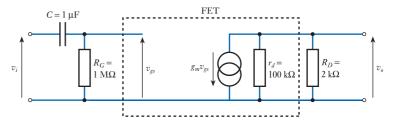

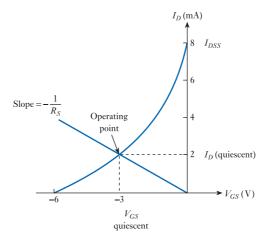

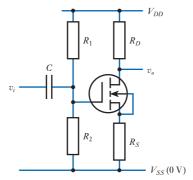

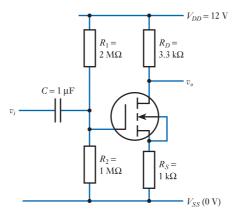

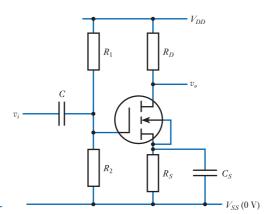

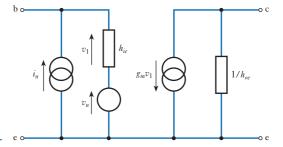

| 18.6   | FET amplifiers                          | 350             | 22.4 Noise in bipolar transistors         | 493 |

| 18.7   | Other FET applications                  | 372             | 22.5 Noise in FETs                        | 493 |

| 18.8   | FET circuit examples                    | 378             | 22.6 Signal-to-noise ratio                | 493 |

| Furth  | er study                                | 381             | 22.7 Noise figure                         | 494 |

| Key p  |                                         | 381             | 22.8 Designing for low-noise applications | 495 |

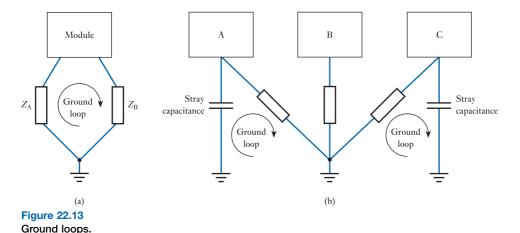

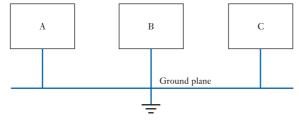

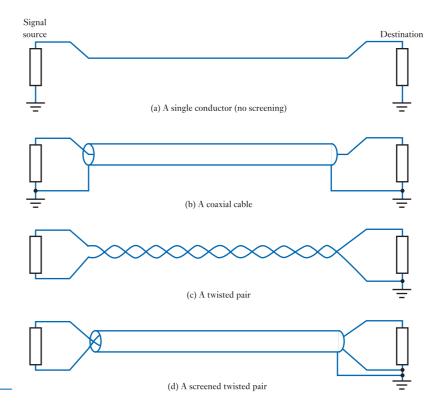

| Exerc  |                                         | 382             | 22.9 Electromagnetic compatibility        | 496 |

| LXCIO  | 1000                                    | 002             | 22.10 Designing for EMC                   | 501 |

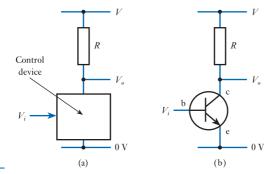

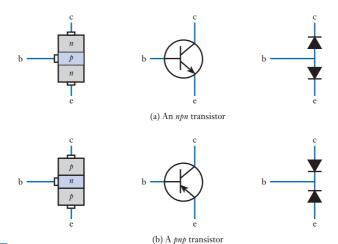

| 19 E   | Bipolar Junction Transistors            | 385             | Further study                             | 510 |

| 19.1   | Introduction                            | 385             | Key points                                | 510 |

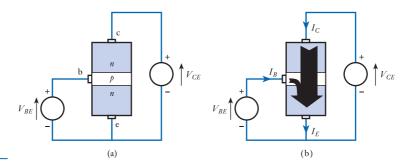

| 19.2   | An overview of bipolar transistors      | 385             | Exercises                                 | 511 |

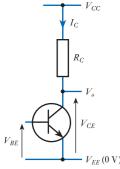

| 19.3   | Bipolar transistor operation            | 387             |                                           |     |

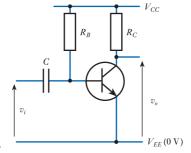

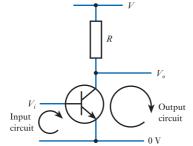

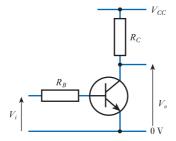

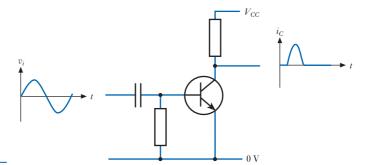

| 19.4   | A simple amplifier                      | 390             | 23 Positive Feedback, Oscillators         |     |

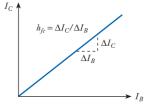

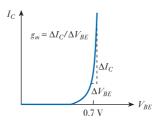

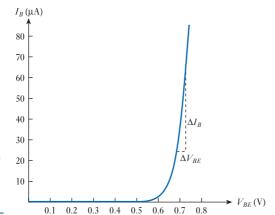

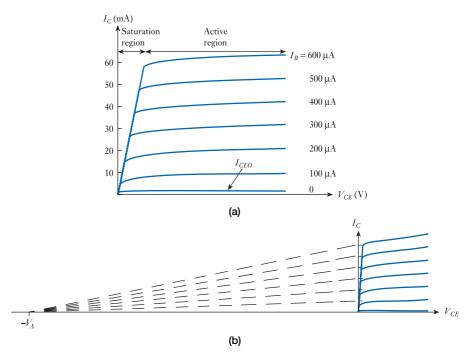

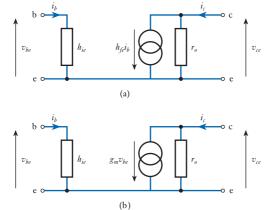

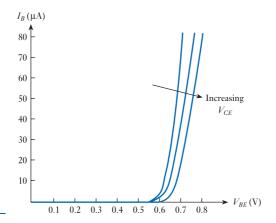

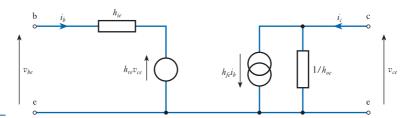

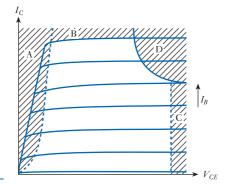

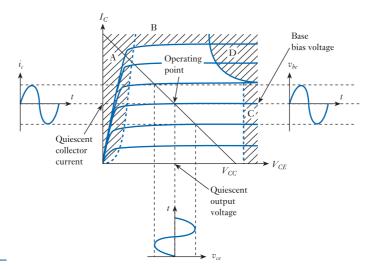

| 19.5   | Bipolar transistor characteristics      | 391             | and Stability                             | 512 |

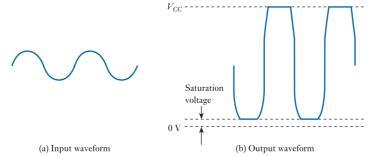

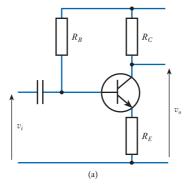

| 19.6   | Bipolar amplifier circuits              | 400             | 23.1 Introduction                         | 512 |

| 19.7   | Bipolar transistor applications         | 437             | 23.2 Oscillators                          | 512 |

| 19.8   | Circuit examples                        | 440             | 23.3 Stability                            | 512 |

|        | er study                                | 442             | •                                         |     |

| Key p  |                                         | 443             | Further study                             | 524 |

| Exerc  |                                         | 444             | Key points Exercises                      | 524 |

|        |                                         |                 | Exercises                                 | 524 |

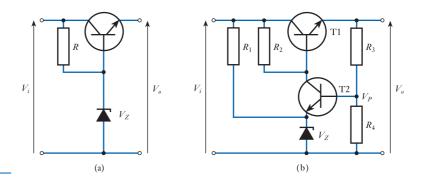

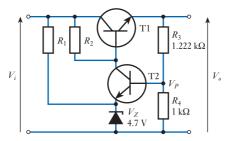

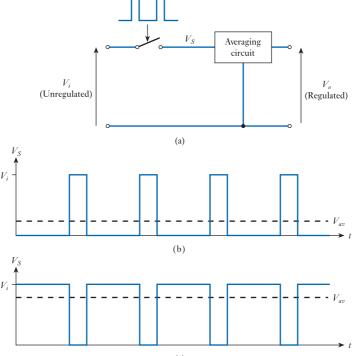

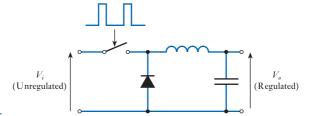

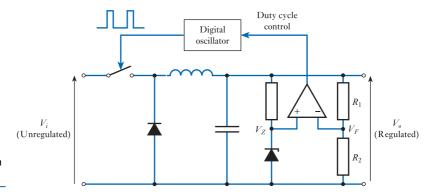

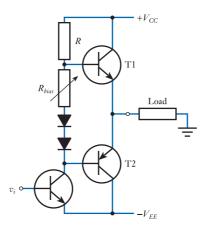

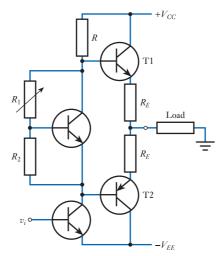

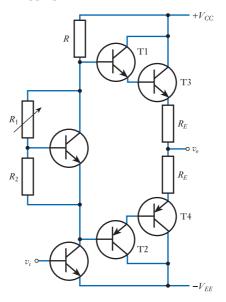

| 20 F   | Power Electronics                       | 449             | 24 Digital Systems                        | 527 |

| 20.1   | Introduction                            | 449             | 24.1 Introduction                         | 527 |

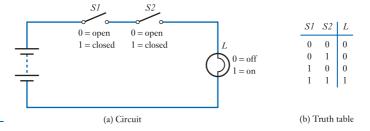

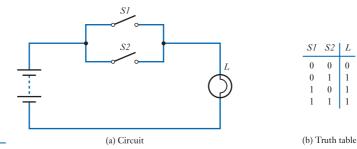

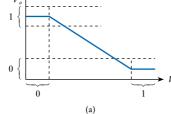

| 20.2   | Bipolar transistor power                |                 | 24.2 Binary quantities and variables      | 527 |

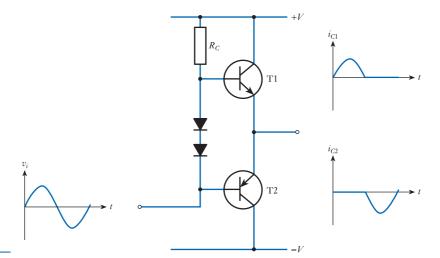

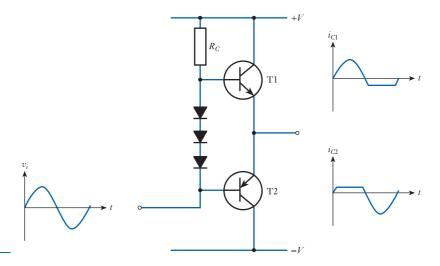

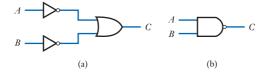

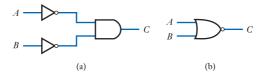

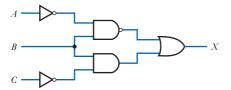

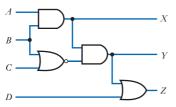

|        | amplifiers                              | 450             | 24.3 Logic gates                          | 531 |

| 20.3   | Classes of amplifier                    | 453             | 24.4 Boolean algebra                      | 535 |

| 20.4   | Power amplifiers                        | 456             | 24.5 Combinational logic                  | 537 |

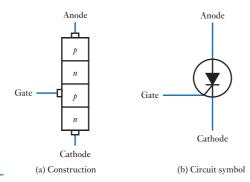

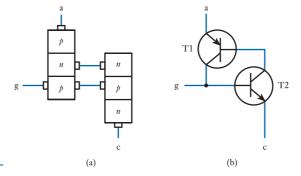

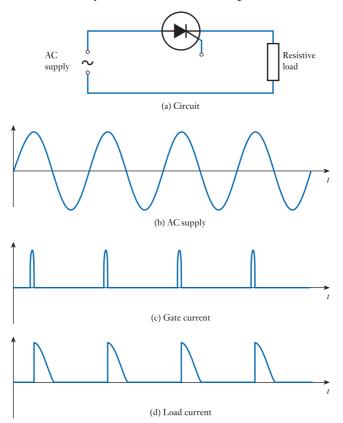

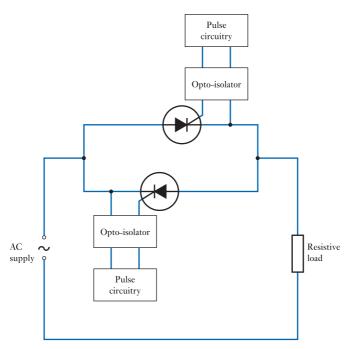

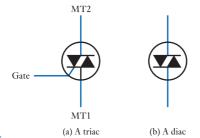

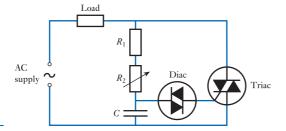

| 20.5   | Four-layer devices                      | 461             | 24.6 Boolean algebraic manipulation       | 542 |

| 20.6   | Power supplies and voltage              |                 | 24.7 Algebraic simplification             | 545 |

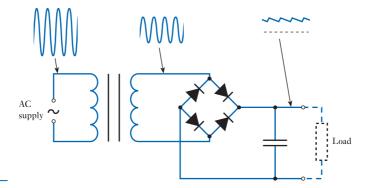

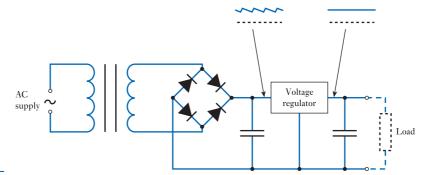

|        | regulators                              | 466             | 24.8 Karnaugh maps                        | 547 |

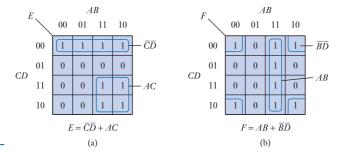

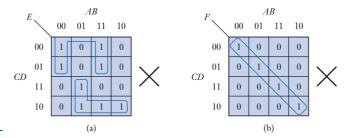

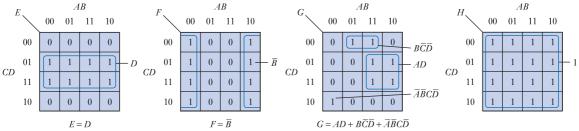

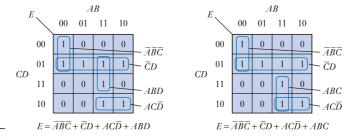

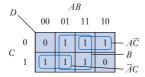

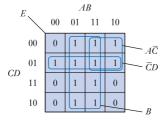

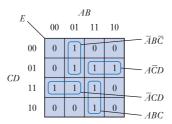

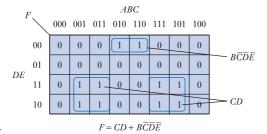

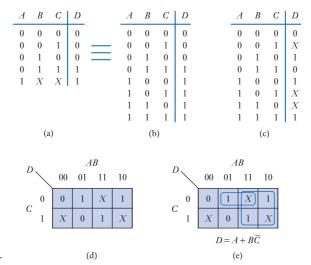

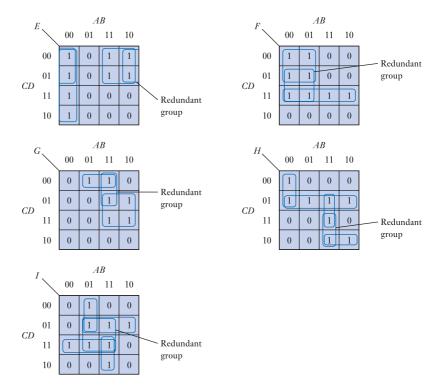

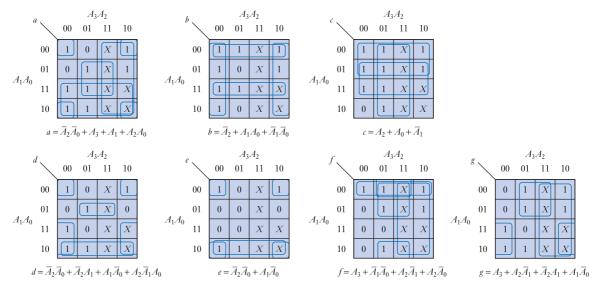

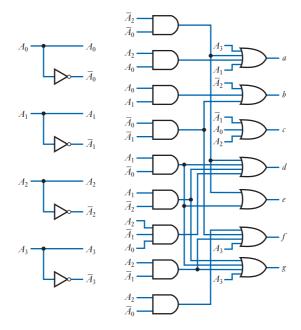

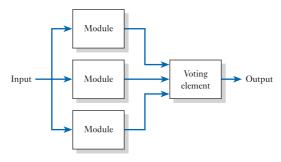

| Furthe | er study                                | 471             | 24.9 Automated methods of minimisation    | 554 |

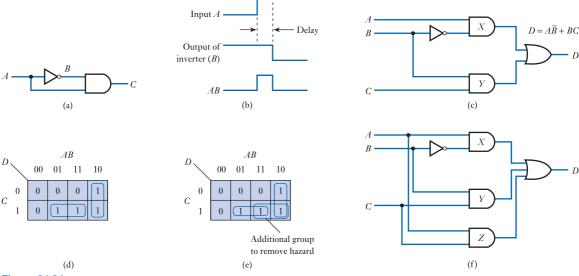

| Key p  | ooints                                  | 471             | 24.10 Propagation delay and hazards       | 555 |

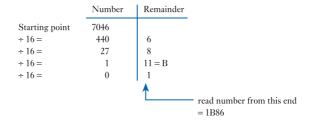

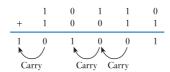

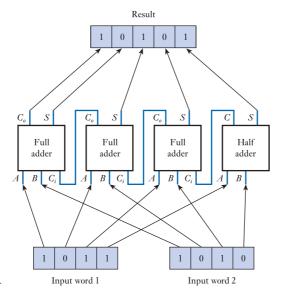

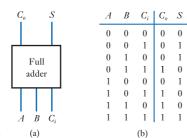

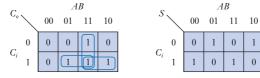

| Exerc  | ises                                    | 472             | 24.11 Number systems and binary           |     |

|        |                                         |                 | arithmetic                                | 557 |

| 21 l   | nternal Circuitry of                    |                 | 24.12 Numeric and alphabetic codes        | 568 |

|        | Operational Amplifiers                  | 475             | 24.13 Examples of combinational logic     |     |

| 21.1   | Introduction                            | 475             | design                                    | 574 |

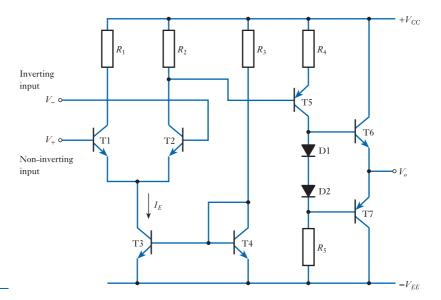

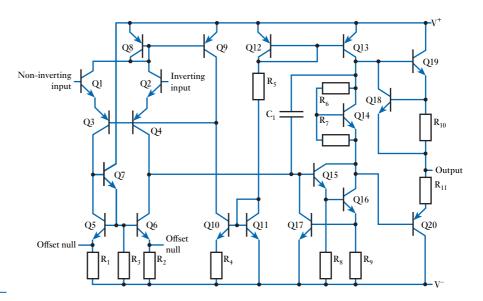

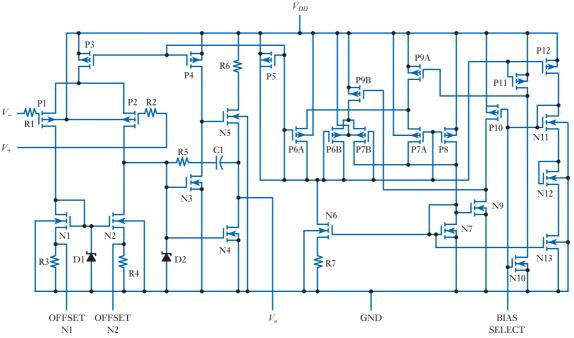

| 21.2   | Bipolar operational amplifiers          | 476             | Further study                             | 580 |

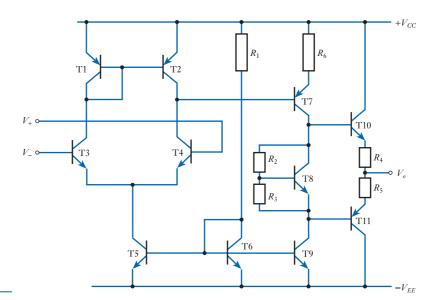

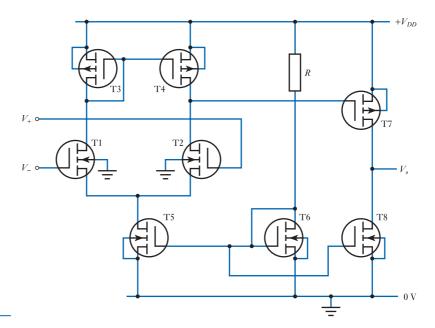

| 21.3   | CMOS operational amplifiers             | 481             | Key points                                | 581 |

| 21.4   | BiFET operational amplifiers            | 485             | Exercises                                 | 582 |

| 21.5   | BiMOS operational amplifiers            | 485             |                                           |     |

|        | er study                                | 486             | 25 Sequential Logic                       | 586 |

| Key p  |                                         | 486             | 25.1 Introduction                         | 586 |

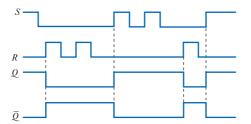

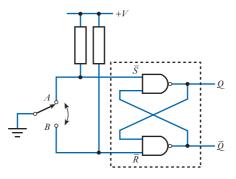

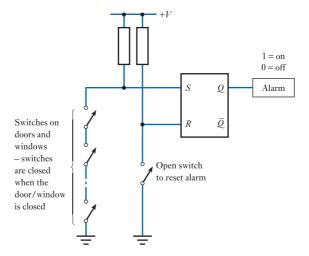

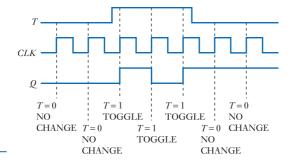

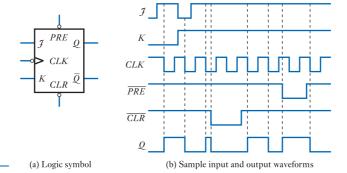

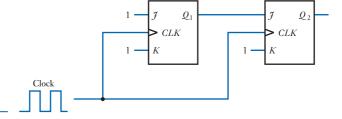

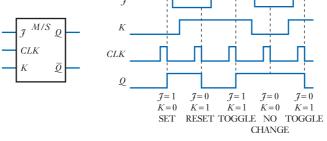

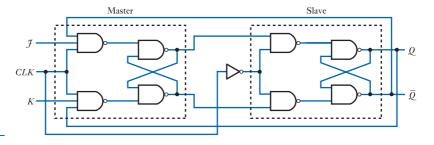

| Exerc  |                                         | 486             | 25.2 Bistables                            | 587 |

| LAGIC  | 1000                                    | <del>-</del> 50 |                                           |     |

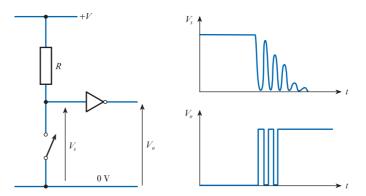

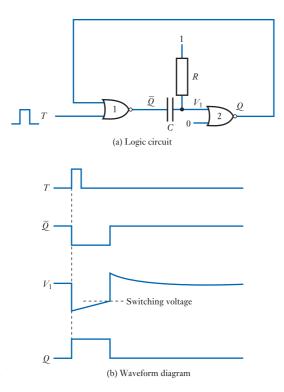

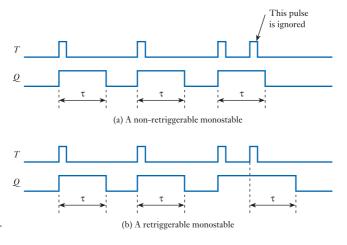

| 25.3         | Monostables or one-shots          | 597        | 28 Data Acquisition and         |            |

|--------------|-----------------------------------|------------|---------------------------------|------------|

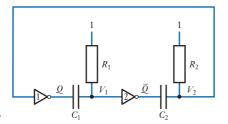

| 25.4         | Astables                          | 598        | Conversion                      | 753        |

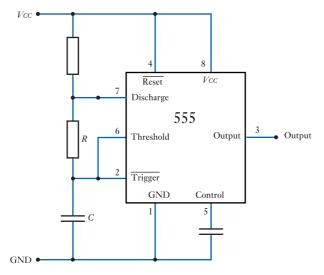

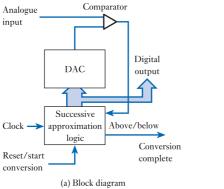

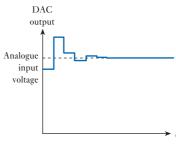

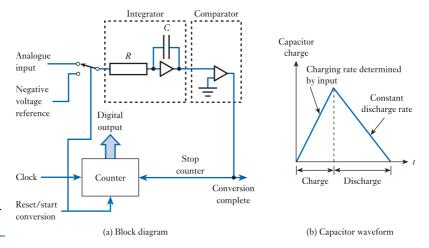

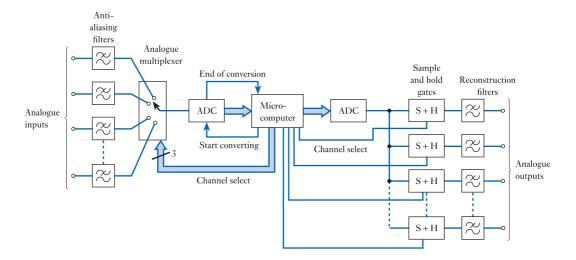

| 25.5         | Timers                            | 600        | 28.1 Introduction               | 753        |

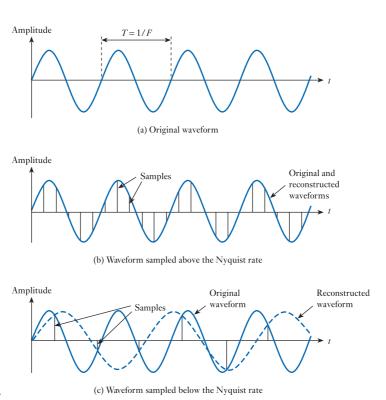

| 25.6         | Memory registers                  | 602        | 28.2 Sampling                   | 753        |

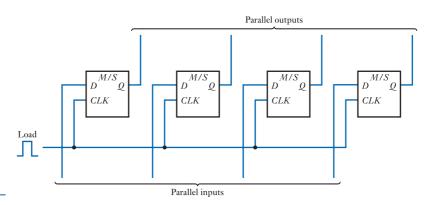

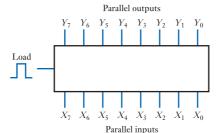

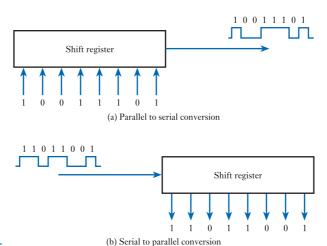

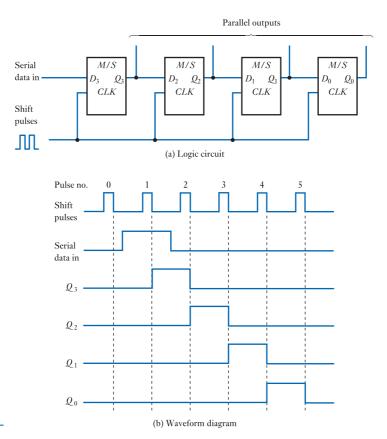

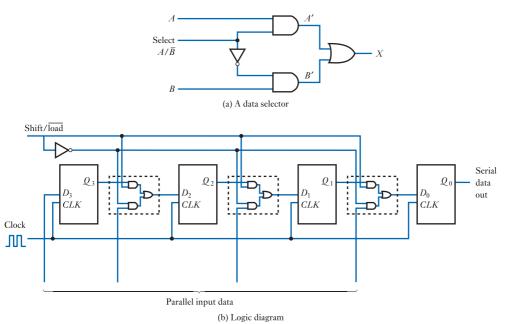

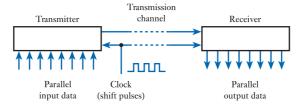

| 25.7         | Shift registers                   | 603        | 28.3 Signal reconstruction      | 755<br>755 |

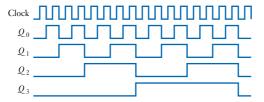

| 25.8         | Counters                          | 606        | 28.4 Data converters            | 755<br>755 |

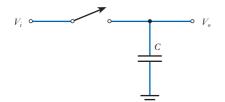

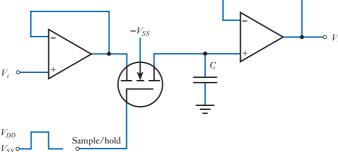

| 25.9         | Design of sequential logic        |            | 28.5 Sample and hold gates      | 762        |

|              | circuits                          | 614        | 28.6 Multiplexing               | 762        |

| Furthe       | er study                          | 625        | '                               |            |

| Key p        |                                   | 626        | Further study                   | 766        |

| Exerc        |                                   | 627        | Key points Exercises            | 766<br>766 |

|              |                                   |            | Exercises                       | 700        |

| 26 E         | Digital Devices                   | 630        | 29 Communications               | 768        |

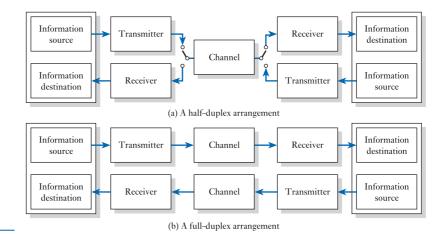

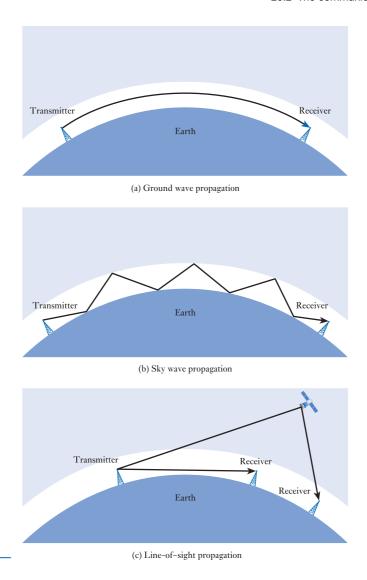

| 26.1         | Introduction                      | 630        | 29.1 Introduction               | 768        |

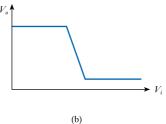

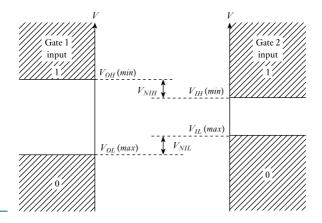

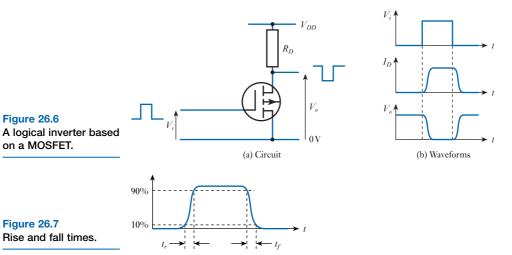

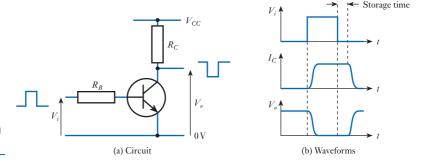

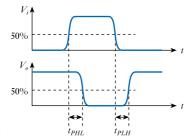

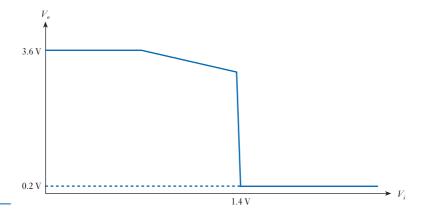

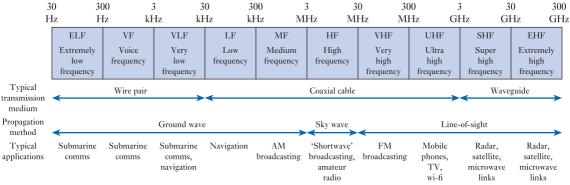

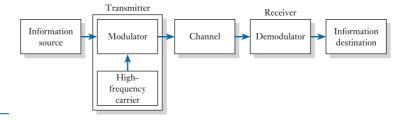

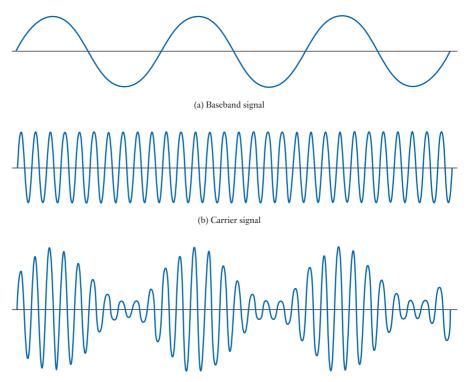

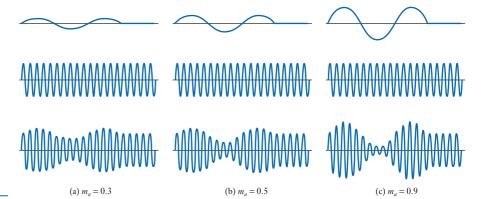

| 26.2         | Gate characteristics              | 632        | 29.2 The communications channel | 770        |

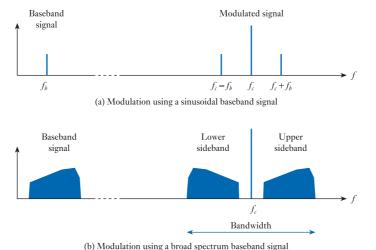

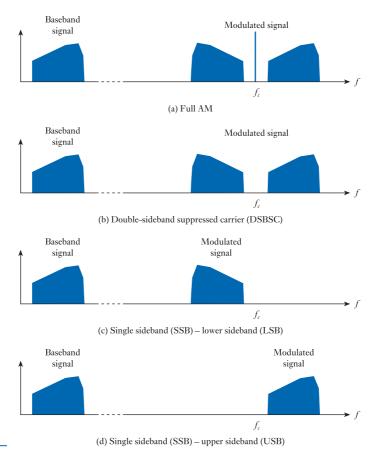

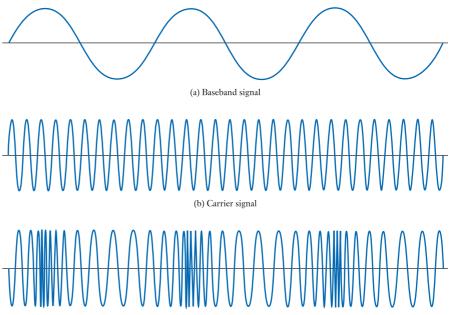

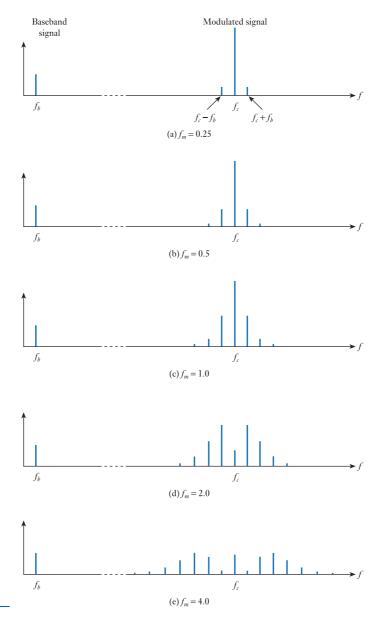

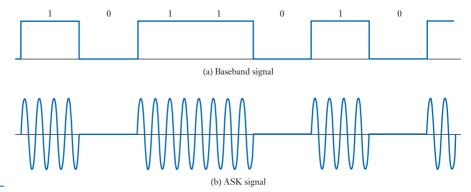

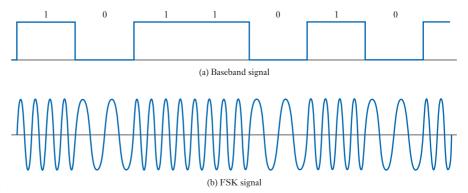

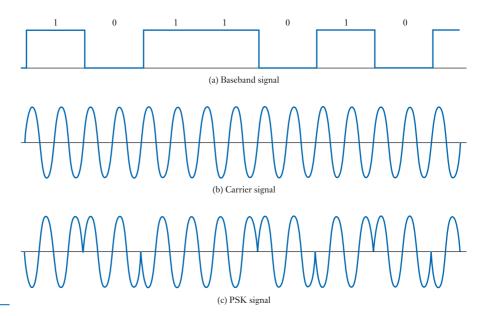

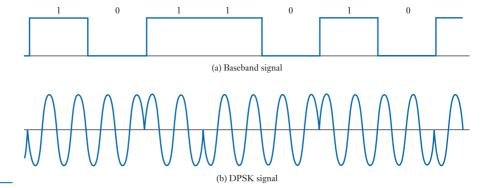

| 26.3         | Logic families                    | 638        | 29.3 Modulation                 | 773        |

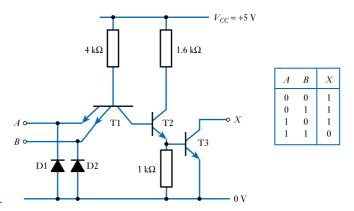

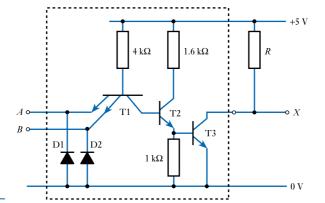

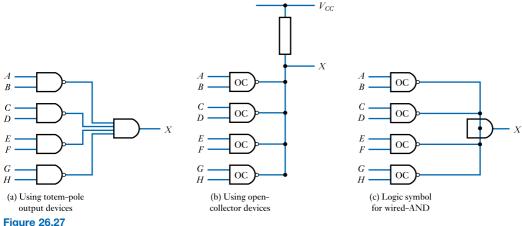

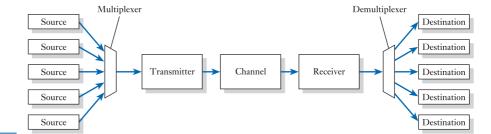

| 26.4         | ΠĹ                                | 648        | 29.4 Demodulation               | 787        |

| 26.5         | CMOS                              | 659        | 29.5 Multiplexing               | 787        |

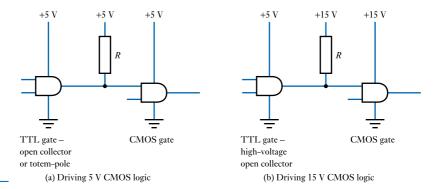

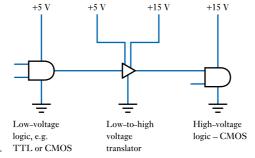

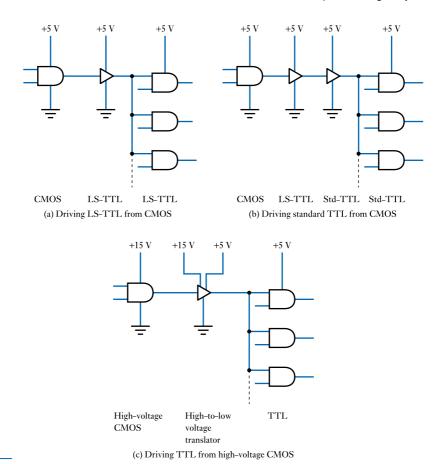

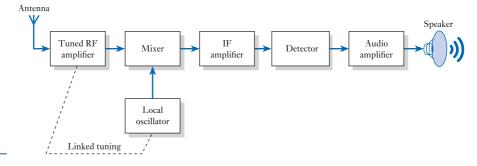

| 26.6         | Interfacing TTL and CMOS or logic |            | 29.6 Radio receivers            | 788        |

|              | using different supply voltages   | 673        | 29.7 Microwave communication    | 790        |

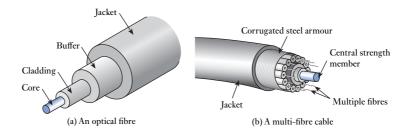

| 26.7         | Power dissipation in digital      |            | 29.8 Fibre-optic communication  | 792        |

|              | systems                           | 675        | Further study                   | 793        |

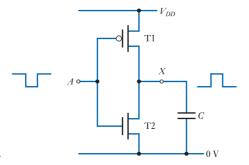

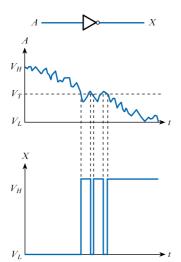

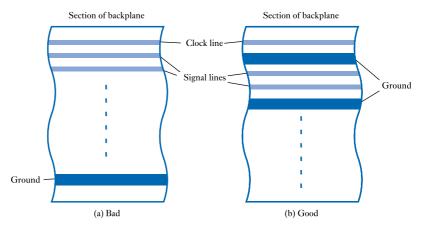

| 26.8         | Noise and EMC in digital systems  | 677        | Key points                      | 794        |

| Furthe       | er study                          | 683        | Exercises                       | 794        |

| Key p        | oints                             | 683        | 20 System Design                | 796        |

| Exerc        | ises                              | 684        | 30 System Design                |            |

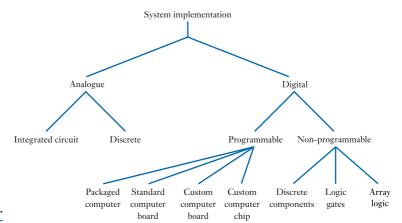

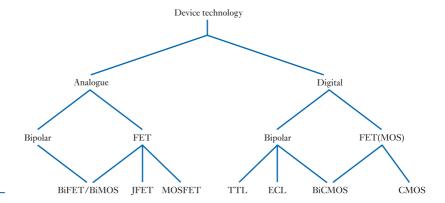

|              |                                   |            | 30.1 Introduction               | 796        |

| 27 l         | mplementing Digital Systems       | 688        | 30.2 Design methodology         | 796        |

|              |                                   | 688        | 30.3 Choice of technology       | 798        |

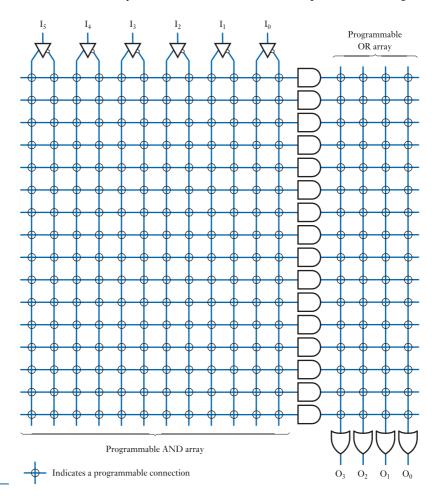

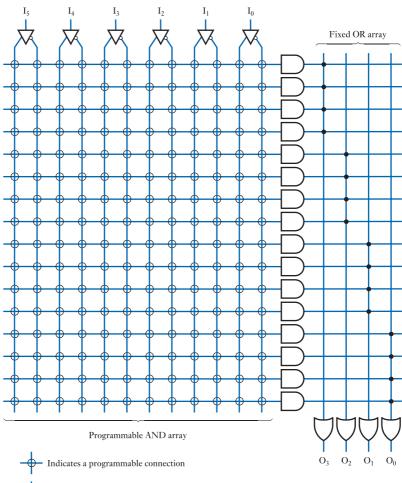

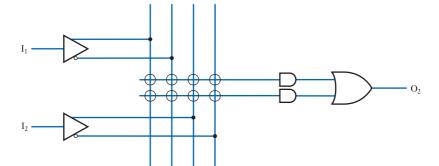

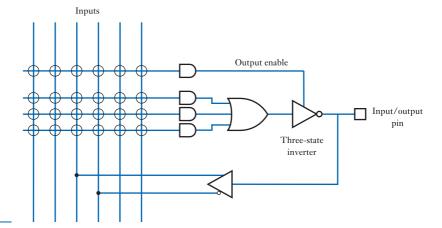

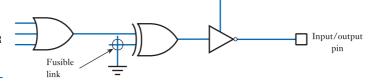

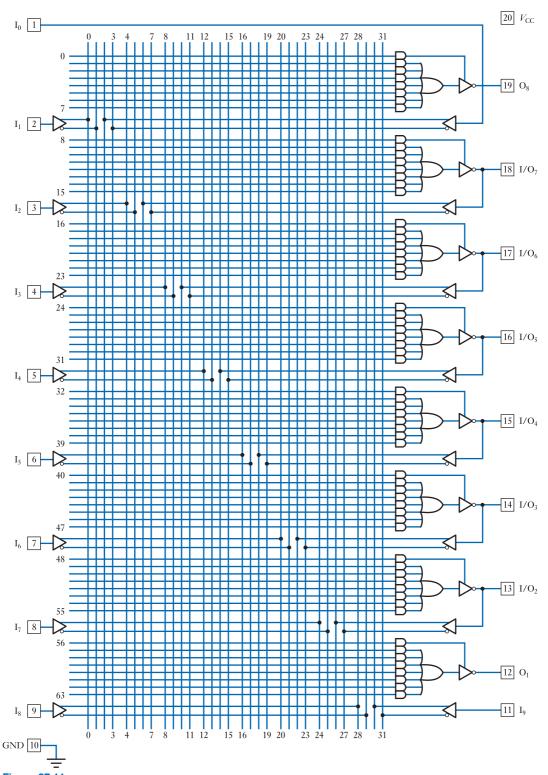

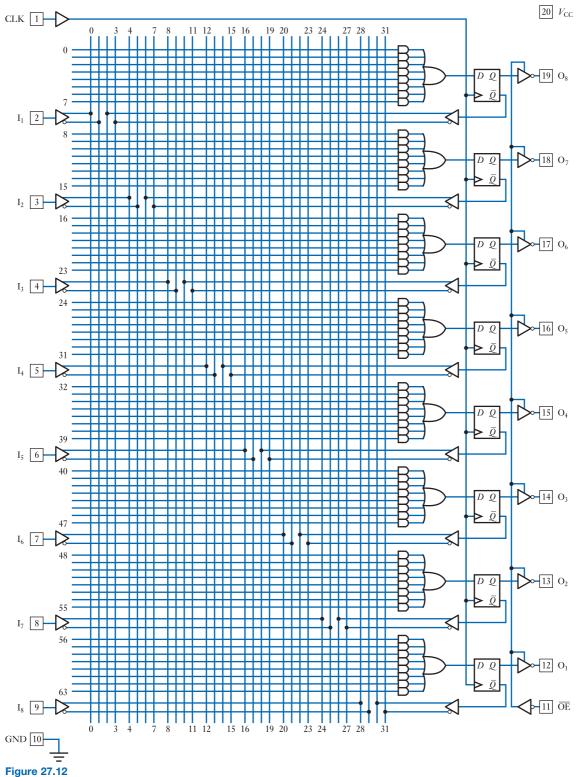

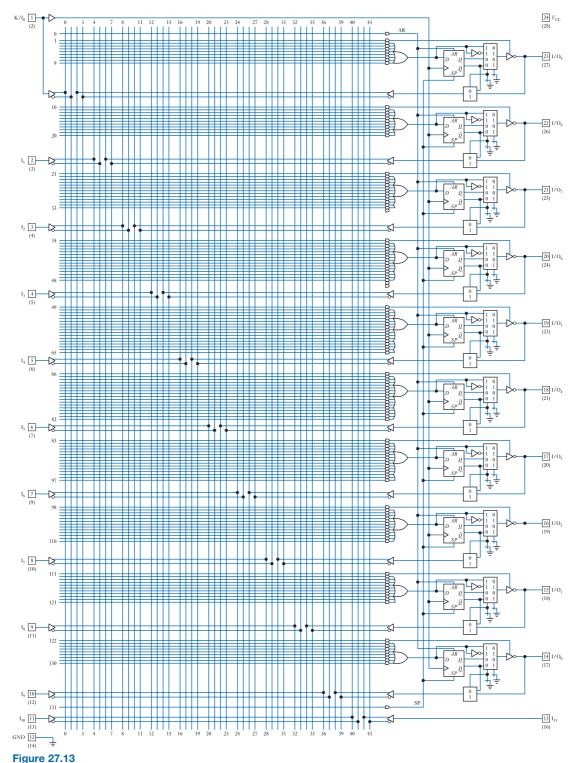

| 27.1<br>27.2 | Introduction                      | 689        | 30.4 Electronic design tools    | 802        |

| 27.2         | Array logic Microprocessors       | 709        | Further study                   | 806        |

| 27.3         | System-on-a-chip (SOC) devices    | 709<br>744 | Key points                      | 806        |

| 27.5         | Programmable logic controllers    | 744        | Exercises                       | 807        |

| 21.5         | (PLCs)                            | 744        | Appendices                      |            |

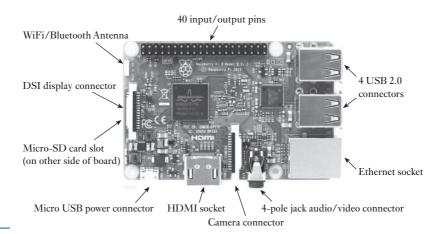

| 27.6         | Single-board computers            |            | • •                             | 000        |

|              | and microcontrollers              | 745        | A Symbols                       | 808        |

| 27.7         | Selecting an implementation       |            | B SI units and prefixes         | 811        |

|              | method                            | 749        | C Op-amp circuits               | 813        |

| Furth        | er study                          | 749        | D Complex numbers               | 818        |

| Key p        |                                   | 749<br>750 | E Answers to selected exercises | 823        |

| Exerc        |                                   | 750<br>751 | Index                           | 826        |

|              | 1000                              | , , ,      | i iiidon                        | 020        |

### **Companion Website**

For open-access **student resources** specifically written to complement this textbook and support your learning, please visit www.pearsoned.co.uk/storey-elec

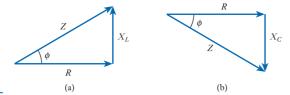

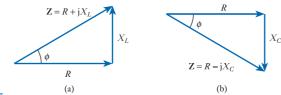

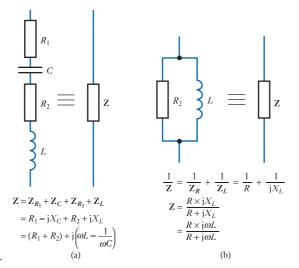

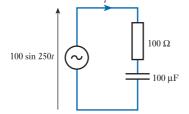

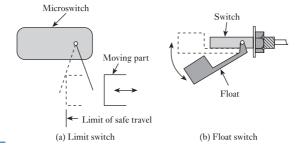

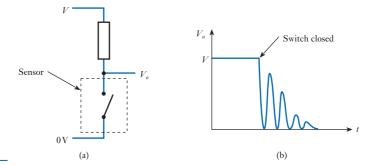

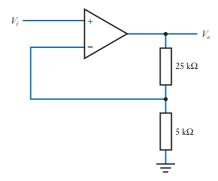

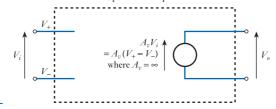

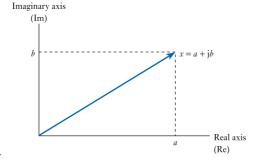

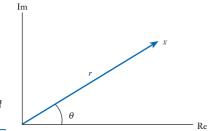

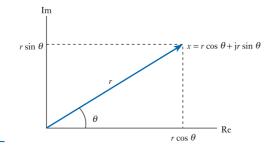

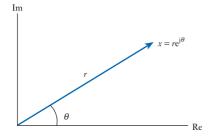

# Preface