## CARRIER CURRENT TRANSMITTER FOR DATA TRANSMISSION

**RADIO-ELECTRONICS**

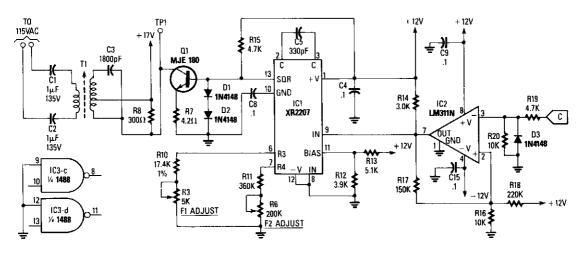

Fig. 18-1

$$f_1 = \frac{1}{R_3 C_1}$$

$$f_2 = f_1 + \Delta f_1$$

where:

$$\Delta f_1 = \frac{1}{R_4 C_1}$$

In this circuit, data at input C is amplified by IC2 and then fed to modulator IC1. IC1 generates two frequencies, depending on the values of  $C_5$ ,  $R_{10}$ ,  $R_3$ ,  $R_{11}$ , and  $R_6$ . The frequency f, is generated if pin 9 IC1 is low and  $f_2$  if pin 9 IC1 is high. A square wave appears at pin 13 of IC1 and is fed to Q1, an amplifier stage, that is coupled via tuned transformer T, to the ac line via C1 and C2. Notice that, for safety reasons, C1 and C2 must be specifically rated for the ac line voltage.

## **CARRIER-CURRENT RECEIVER FOR DATA TRANSMISSION**

**RADIO-ELECTRONICS**

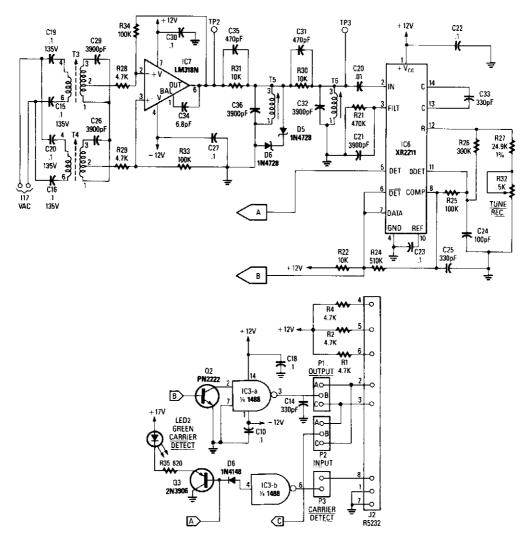

Fig. 18-2

Receive frequency:

$$f_0 = \frac{1}{(R_{27} + R_{32}) C_{33}}$$

This receiver consists of an input network amplifier IC7 FSK PLL detector ICG, and output amplifier/interface Q2, Q3, IC3A and IC3B, a 1488 Quad RS232 line driver of the carrier-current signal. Tuned amplifier IC7 amplifies this signal and drives PLL detector IC8. The values shown in the circuit are suitable for operation in the 100-kHz range. Recovered data at pins 5, 6, 7 is fed to the output amplifier/interface circuit (Fig. 6). This circuit is also used with the carrier-current data transmitter to form a pair.