# CIRCUIT SURGE

REGULAR CLINIC

BY IAN BELL

# **Power supply switching**

**AST MONTH**, we considered some issues related to the provision of multiple supply voltages. This is a very common requirement in electronic systems where different chips and subsystems, and often individual chips, need different power supply voltages. That article was in response to some discussion on the provision of multiple power supply voltages, power supply switching and regulator circuits, started by user Tuurbo46 on the EPE Chat Zone. The discussion continued (under username Rocket **Ron**) on the new EPE forum hosted by EEWeb (www.eeweb.com/forum/tags/ epe-magazine).

One of the specific issues from Tuurbo46/Rocket Ron posts concerned the possible use of a potential divider to obtain a lower supply voltage from a higher one. We looked at the fundamentals of potential dividers and demonstrated that potential dividers were very inefficient (wasteful of power) used in this way if reasonable load regulation was required, and are thus generally unsuitable for providing power supply voltages. The exception might be for a sub-circuit with extremely low power requirements. We also looked briefly at possible configurations of two regulators used to provide two different supply voltages.

On the EEWeb forum the discussion moved on to the issue of switching power supplies on and off using a microcontroller. Rocket Ron wrote: 'I am now going to use three LM317s to set separate voltages, 5V, 2.5V and 1.25V to supply 100mA. I want to switch these three separate voltages ON/OFF with three micro I/O pins...'.

Later, he added: '...I have decided to use a PFET in series with VIN on the LM317 (default setting off), and

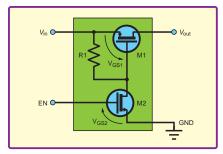

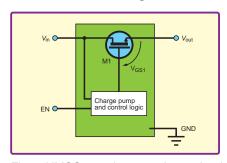

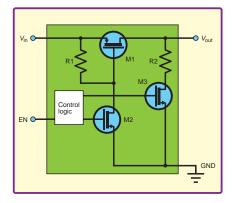

Fig.1. Basic load switch circuit.

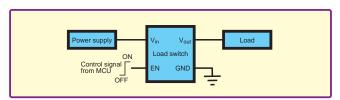

Fig.2. Connection of load switch from Fig.1 in a circuit

then an NPN on the gate connected to GND. The I/O pin is connected to the base of the transistor. When voltage is required, the I/O pin powers the base on the transistor. Is this a better method of doing it?'.

Therefore, continuing with the power supply theme from last month, we will now look at the various options for switching power supplies on and off as part of system operation.

The switching of power supplies, like the need for multiple supplies, is a common requirement in electronic systems. Multiple power supplies often have to be switched on and off in a particular order to ensure correct operation, or even prevent damage to a system - this is known as power supply sequencing. It is also a common requirement to be able to power-off some subsystems when they are not in use to reduce power consumption known as power supply distribution.

# **PMOS load switches**

Circuits for power supply switching are typically called load switches or power switches. You can also implement a load switch using transistors, as suggested by Rocket Ron. A typical basic load switch circuit is shown in Fig.1, and is similar to the circuit described by Rocket Ron except that both transistors are MOSFETs. EN is the enable input, which may be connected to a microcontroller output (as in  ${\it Rocket\ Ron's}$  application). The connection of the load switch in a circuit is shown in Fig.2.

In the circuit in Fig.1, M1 is a PMOS transistor, which acts as the main switch. M2 is an NMOS transistor used to switch M1 via the EN input. A high input (logic 1 output from a microcontroller general purpose I/O pin) is required at EN to switch the load on (connect  $V_{\rm in}$  to  $V_{\rm out}$ ). With 0V applied (GPIO logic 0) to EN, the load will be off ( $V_{\rm in}$  disconnected from  $V_{

m out}$ ). To consider the circuit in more

detail recall that a MOSFET transistor

will switch on when its gate-source voltage  $(V_{\rm GS})$  is greater than its threshold voltage  $(V_{TH})$ . A PMOS transistor requires a negative  $V_{

m GS}$  to turn on (gate negative with respect to source) whereas an NMOS transistor requires a positive  $V_{\rm GS}$  (gate positive with respect to source). In the circuit in Fig.1, with a high input on EN, M2 turns on and pulls the gate of M1 low (close to 0V) so that, assuming  $V_{\mathrm{in}}$  is larger than the threshold voltage of M1, M1 will turn on, connecting  $V_{\rm in}$ to  $V_{\text{out}}$ . When EN is at 0V, M2 will be off (effectively open circuit), during which time resistor R1 ensures that the gate voltage of M1 is pulled up to  $V_{\rm in}$  – so that the gate-source voltage of M1 is close to zero and M1 is off. In some situations it may be necessary to include a pull-down resistor between the gate of M2 and ground to make sure M2 is always off when not actively driven.

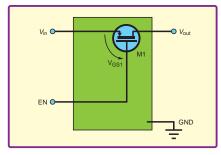

It may be possible to use a simpler switch circuit – just a PMOS transistor (as in Fig.3) with its gate connected directly to the microcontroller. The connection of the load switch is as in Fig.2 except that the logic of the on and off control on EN input is inverted. Although this circuit uses fewer components it has a number of disadvantages. One problem is that the switch will be on with a 0V output from the microcontroller. This means the switch is likely to

Fig.3. A single PMOS transistor is potentially usable as a load switch, but this circuit has some disadvantages.

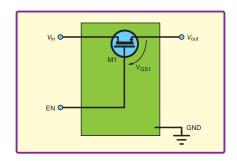

Fig.4. A single NMOS transistor used as a load switch. This circuit can be used if the logic high voltage applied to EN is sufficiently more positive than  $V_{\text{IN}}$ .

be on at system power-up, before the microcontroller initialises and the code has reached a point where the switch can be controlled. Also, putting the microcontroller into power-down or sleep modes will be likely to turn the switch on, which in many cases would not be what is required.

Another issue with using a single PMOS transistor relates to the voltages that can be switched. For the transistor to be off its gate voltage must be greater than  $V_{\rm IN}-V_{\rm TH}$  so that  $V_{\rm GS}$  is less than  $V_{\rm TH}$ . This restricts the maximum  $V_{\rm IN}$  voltage that can be handled to be  $V_{\rm OH}+V_{\rm TH}$ , where  $V_{\rm OH}$  is the logic 1 (high) output voltage from the microcontroller.

#### **NMOS** switches

A single NMOS transistor can also be used as a load switch, as shown in Fig.4. The connection and logic direction are as in Fig.2, but because the NMOS transistor requires a positive  $V_{\rm GS}$  to switch on,  $V_{\rm IN}$  must be less than  $V_{\rm OH}-V_{\rm TH}$ . This could be feasible in some situations, such as a 5V microcontroller controlling a 3.3V supply, or a 3.3V microcontroller switching a 1.8V supply. However, there are many situations where a single NMOS transistor cannot be used.

In situations where the control voltage is not larger than  $V_{\mathrm{IN}}$ , an NMOS transistor can still be used with the help of some additional circuitry to produce a higher voltage than  $V_{\rm IN}$ , which is used to control the gate of M1 – see Fig.5. The higher voltage is produced by a circuit called a charge pump, a form of switch-mode DCto-DC converter which only uses capacitors, rather than the inductors commonly found in full switch-mode power supplies. Use of capacitors facilitates on-chip implementation, although discrete-component charge pumps can also be built.

The basic way in which a charge pump works is to charge a capacitor to  $V_{\rm IN}$  and then use MOSFET switches to rearrange the capacitor connections so that the negative end is connected to  $V_{\rm IN}$ . This produces a voltage of  $2\,V_{\rm IN}$  (across  $V_{\rm IN}$  and the capacitor in series), which can be used to charge another capacitor to  $2\,V_{\rm IN}$ . The switching

process is repeated under control of a clock signal to keep 'pumping up' the output capacitor to the higher voltage. Diodes are used to ensure the charging currents flow as required. Using multiple stages, voltages of several times  $V_{\rm IN}$  can be achieved.

So far, we have introduced some basic load-switching circuits, and with the exception of the charge pump in Fig.5, these require a very small number of components and are easily implemented with discrete MOSFETs. However, a variety of load switch integrated circuits are available from a number of manufacturers. The availability of ICs indicates a commercial driver for their existence, in this case it is the common need for load switching combined with miniaturisation - load switch ICs take up less board space than circuits built with discrete components. This is important if you are trying to fit everything in a small package such as a mobile phone or mini tablet. Miniaturisation is generally of less concern to amateur designers, but IC load switches often provide additional features or performance enhancements over the basic two-transistor circuit, so are worth considering.

Fig.5. NMOS transistor used as a load switch with a charge pump supplying the required gate voltage.

#### **Characteristics**

There are a number of characteristics and issues that may need to be considered when selecting a load switch IC or designing a load switch circuit. Some basic characteristics are detailed below.

Input voltage – the range of voltages, which can be switched. The power supply voltage being switched must be within this range. For discrete designs this will relate to the maximum voltage ratings of the transistors used. For load-switch ICs, the input range will be given on the data sheet. Furthermore, load-switch ICs may also have another connection (sometimes called the bias voltage), which is a supply for the internal circuits. Again, the datasheet will specify the requirements for this voltage.

Maximum continuous current – the maximum current the switch can handle. The maximum continuous current taken from the supply by the circuit being switched must be less

than this. This will specified for a loadswitch IC. For a discrete MOSFET, the maximum continuous drain-source current must be suitable.

On resistance - the resistance of the load switch from input to output in the on state. This is basically the on resistance of the M1 MOŠFET in Fig.1, 3, 4 and 5. The on resistance has a significant effect on the power dissipation of the load switch when the load is active – a low on resistance is required to keep dissipation down. It is worth noting that although M1 (in the circuits shown) is on when  $V_{\rm GS}$  is just greater than the threshold voltage, a sufficiently low on resistance may require a significantly larger gate-source voltage than  $V_{\rm TH}$ . This could be an issue in some uses of the circuits in Fig.1, 3 and 4, depending on  $V_{\rm IN}$  and/ or the microcontroller logic voltage. The charge-pump circuit in Fig.5 can overcome the limitations of the low circuit voltages to apply a larger  $V_{GS}$  to achieve low on resistance.

Leakage and quiescent currents – the load switch will exhibit some leakage current from  $V_{\rm IN}$  when the power supply is on and the load switch is off. For IC load switches there will be some quiescent current in addition to the load current required to power internal circuitry, even if no load is connected. For the circuit in Fig.1, when the switch is on there will be current flowing through R1 (via M2) which will be in addition to the load current, reducing the efficiency of the circuit.

There are also a number of circuit behaviour/performance issues, which may need to be taken into account and which may not be obvious to anyone who has not used load switches before. Of particular importance are: the effect of inrush current, the behaviour of the load after switch-off, and the need for reverse-current protection in some applications.

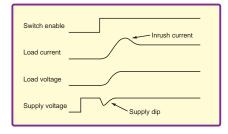

## Inrush current and supply dip

Directly after a circuit is switched on it may briefly take a much higher current than during normal operation. Typically this is due to capacitance across the supply lines changing up and is referred to as 'inrush current'. For a simple system, where all the circuitry powers up together this may not be a problem - the system can be stopped from trying to do anything with a power-on reset which lasts longer than time taken for the supplies to settle. However, when a system is already powered up and a new subsystem is switched on using a load switch, the power supply will experience the inrush current and may not be able to sustain its output voltage due to the sudden heavy demand. The supply voltage will dip momentarily, which may disrupt the operation of other subsystems that

Fig.6. Inrush current and supply dip waveforms.

are already powered up. Waveforms illustrating this situation are shown in Fig.6.

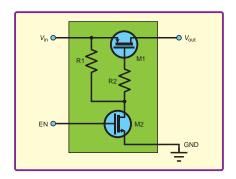

To prevent load switches from disrupting system power supplies they can be designed to limit the rate of increase of their output voltage (known as the 'slew rate'). This is a typical feature of IC load switches, which may allow the slew rate to be controlled via an external capacitor or resistor. In discrete circuits, the output voltage slew rate can be reduced by putting a resistor in series with the MOSFET gate. Fig.7 shows the circuit from Fig.1 modified in this way.

Fig.7. Load switch from Fig.1 with slew-rate-limiting resistor R2 added.

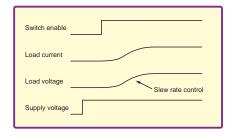

A MOSFET gate is a capacitance, and the resistor simply increases the time it takes to charge up during switch on. The effect is to relatively gradually reduce the on resistance, which causes the load capacitance to charge more slowly, reducing the inrush current. The resulting waveforms are shown in Fig.8.

Fig.8. Load switch waveforms with slew-rate limiting (compare with Fig.6).

# Rapid output discharge

There may also be problems when a load is switched off. A load switch such as the circuit in Fig.1 simply disconnects the supply. However, the disconnected circuit may continue to be active for a while, powered from

Fig.9. Load switch with output discharge.

the capacitance across its supplies. Again, this may occur in a simple all-on/all-off system, but will not usually have any consequences. However, if a subsystem is powered down in this uncontrolled way while other parts of the system are active, its continued, possibly erratic operation may cause problems. The solution is to switch a resistance across the load switch output to rapidly discharge a load capacitance and ensure a quick and clean shutdown.

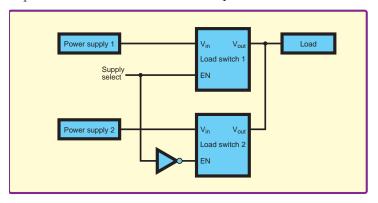

An example of a rapid output discharge switch, applied to the circuit in Fig.1, is shown in Fig.9. The control logic switches M3 on when the load is switched off. The value of R2 is selected to provide rapid reduction in the load supply voltage without causing excessive current flow. Use of a rapid output discharge switch is not possible in all situations, for example where load switches are used to select between different input supplies (see Fig.10), or when a battery is connected across  $V_{

m OUT}$ . In such cases, the rapid discharge circuit would apply an excessive load to the other power source.

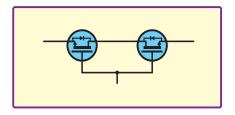

Fig.11. Two MOSFETs forming a switch with reverse-current protection.

are a number of ways in which load switches can be protected from reverse currents. A diode in the path from  $V_{\rm IN}$  to  $V_{\rm OUT}$  is a possibility, but this will drop voltage and dissipate power, which is not ideal.

Another approach to reverse-current protection is to use two MOSFETS in the switch, with their sources and drains in opposite directions, as shown in Fig.11 (for an NMOS switch). When the MOSFET is on it is effectively symmetrical in this situation - the low on resistance means that the voltage drop from source to drain is small, so the gate-source and gatedrain voltages are more or less equal. When the device is off the body diode can conduct in one direction; using two MOSFETS, as in Fig.11, means that the two body diodes in series are in opposite directions and cannot provide a conducting path. With all else equal, this circuit will have a higher on resistance than one using a single transistor, but is likely to have lower impact than using a diode in the power line.

## Load switch ICs

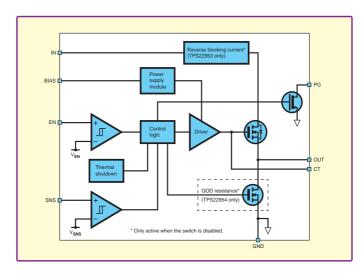

As mentioned earlier, there are a large number of load switch ICs available. Fig.12 shows the block diagram for a pair of devices, the TPS22954/

Fig. 10. Supply multiplexing using load switches.

# **Reverse protection**

In situations where a load switch is off, but a voltage is present on  $V_{\rm OUT}$  — for example, in the supply multiplexer shown in Fig.10 — there is a possibility that a reverse current may flow through the off switch if its input voltage is less than  $V_{\rm OUT}$ . The reverse current can flow through the body diode of the switch MOSFET and may cause damage to the transistor and other parts of the system. There

TPS22953 14m $\Omega$  on-resistance load switch from Texas Instruments, chosen somewhat randomly to illustrate some of the features that these chips offer. The two chips provide the option of either quick discharge or reverse block, as just discussed. These chips can handle  $V_{\rm IN}$  from 0.7V to 5.7V, and currents up to 5A.

The TP\$22954/TP\$22953 provides output slew-rate control via a capacitor connected to the CT pin. The device

Fig.12. Example load switch IC – the Texas Instrument TPS22954/TPS22953 (block diagram from device datasheet).

requires a separate power supply via the BIAS pin, which may be connected to  $V_{\rm IN}$  if the voltage levels are suitable. The control logic is a little more complex than the examples discussed above. This sense pin (SNS) can be used to monitor a voltage level and provide a 'power good' output via the PG pin. One possible use for this is in power supply sequencing — once the first supply is fully on this is sensed by its load switch and its PG output is used to enable the next supply in the sequence. This is far from the full story of applications for, and features of, this and other similar ICs — consult their datasheets for details.