## Pseudo-random timer for a bird scarer

This circuit is designed to triggor a gas cannon to scare brids and bats away from crops. The period between cannon firings must vary or else the flying creatures will learn to avoid it. It was decided that the cannon firings must have a minimum interval of 10 minutes and a maximum of one hour. This circuit (Fig. 1) cycles through 10 different periods which are preset using resistors.

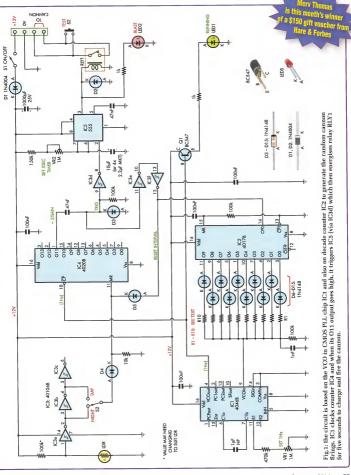

It's based around the voltage controlled oscillator (VCO) section of CMOS PLL chip IC1 (4046B) plus decade counter IC2 (4017B). At power-up, the MR pin of IC2 is pulled high and so the counter is reset. In this state, output O0 (pin 3) is high while the other outputs are low. This means that D6 is forward-biased and so current can flow through R1, which is normally 100kΩ (as explained later).

This forms a voltage divider with the lower 100kΩ resistor which is filtered by a 1nF capacitor and the resulting voltage (about 5.5V) is applied to pin 9 of IC1. This is the VCO control input and so determines the oscillator frequency.

Other components which affect the frequency are the  $1\mu F$  capacitor between the C1a and C1b pins and the resistance from pin 11 (R1) to ground. VR1 is adjusted so that with R1 =

$100k\Omega$ , the VCO output at pin 4 is 1Hz. This is buffered by NPN transistor Q1 to flash the running LED (LED1) to indicate that the circuit is operational.

It's also fed into CMOS 14-stage ripple carry counter IC4 (4020B). Its O11 output (pin 1) goes high after 2<sup>11</sup> (2048) clocks which, with an input rate of 1Hz, is after around 35 minutes (ie, 2048 + 60 seconds).

When this output goes high, the pulse is coupled to input 9 of IC3d, one section of a Schmitt-trigger inverter. It's AC-coupled via a capacitor to give a brief pulse and the output of the inverter's low excursion triggers 555 timer IC5 which energies er 18 RLY1 for five seconds (adjusted using trimpot VR2).

This is the charge time for the case

cannon and when the relay contacts open, the cannon fires, making a very loud noise! LED2 is lit during the charging period, to warn people who may be working on the unit to cover their ears.

At the same time, this trigger signal is buffered using inverter stages IC3e and IC3f to give a positive pulse at the MR (master reset) input of IC4, so that it starts counting from zero again. This pulse is also applied to clock input CP0 (pin 14) of IC2 and the next output then goes high.

After the first 35-minute period, O1 of IC2 is now high while the other outputs are low and so now R2 determines the voltage at pin 9 of IC1. By selecting a different value from R1, the result is that the VCO runs at a different frequency and so the next period before the cannon fires is different to the last. This period is proportional to the resistor value, so R1-R10 can range from  $27 k\Omega$  (10 minutes) up to  $180 k\Omega$  (just over an hour).

The remainder of the circuit is used to set the unit so that it only runs during daylight hours or alternatively, only at night, depending on what type of creature is being attracted to the crop. When light falls on the LDR, its resistance is low and so the output of inverter IC3a is high. Thus, if switch S2 is set in the "night" position, during the day, diode D4 is forward-biased, holding the master reset input of IC4 high and thus preventing it from counting.

The output of IC3a is further inverted by IC3b and so if the switch is in the "day" position, the opposite occurs. In other words, IC4 is held in a reset state at night and allowed to run during the day.

Note that it is suggested that  $R1 = 100 k\Omega$  since that makes calibration easy; at power-up, the output of IC1 should be exactly 1Hz so VR1 can then easily be adjusted with the aid of a frequency counter (built into many DMMs these days).

Mery Thomas, Balgal Beach, Old.

siliconchip.com.au JANUARY 2014 77