## **EXCLUSIVE-OR GATE APPLICATIONS**

## **ANAND TAMBOLI**

OR gate is a derived logic gate that finds many applications in digital circuits. Here we have described use of XOR gate as controlled inverter, 9's BCD subtractor and up-/down-counter.

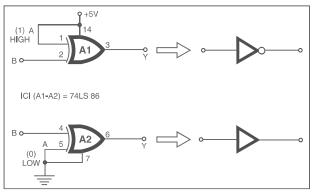

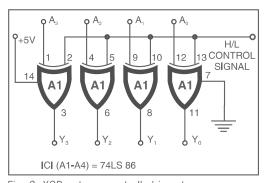

It can be seen from Fig. 1 and the accompanying truth table that XOR gate works as NOT (inverter) gate when its one input is held high, and as a buffer when the same input is pulled low. The common input (as shown in Fig. 2) can

therefore be used as control input for XOR gates to behave as inverters or buffers. Here one of the inputs of each XOR gate are connected

| TRUTH TABLE I<br>XOR Gate |   |   |  |  |

|---------------------------|---|---|--|--|

| A                         | В | Y |  |  |

| 0                         | 0 | 0 |  |  |

| 0                         | 1 | 1 |  |  |

| 1                         | 0 | 1 |  |  |

| 1                         | 1 | 0 |  |  |

|                           |   |   |  |  |

Fig. 1: XOR gate as inverter and buffer

Fig. 2: XOR gate as controlled inverter

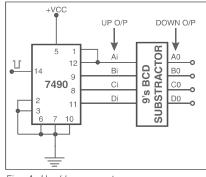

Fig. 4: Up-/down-counter

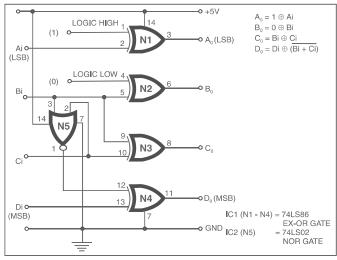

Fig. 3: XOR gate as 9's BCD subtractor

together to serve as the control signal, while the remaining inputs serve as input bits.

When control signal is zero, the output is same as the input (buffer mode). However, when control signal is held high, all bits are inverted. Thus the output is complement of the input. This complementing function is useful in

subtraction circuits using 1's and 2's complements.

In another configuration of XOR gate shown in Fig. 3, the circuit works as a 9's BCD subtractor. Its output = 9 - input.

The circuit in Fig. 3 can be used as a down-counter when employed with 4-bit BCD counter IC 7490 as shown in Fig. 4. Truth table of this configuration is given alongside. As seen from the figure, this circuit can be built using a single XOR-IC (TTL-

| TRUTH TABLE II<br>Down-Counter |          |          |          |  |

|--------------------------------|----------|----------|----------|--|

| DiCiBiAi                       | DEC. EQ. | D0C0B0A0 | DEC. EQ. |  |

| 0000                           | 0        | 1001     | 9        |  |

| 0001                           | 1        | 1000     | 8        |  |

| 0010                           | 2        | 0111     | 7        |  |

| 0011                           | 3        | 0110     | 6        |  |

| 0100                           | 4        | 0101     | 5        |  |

| 0101                           | 5        | 0100     | 4        |  |

| 0110                           | 6        | 0011     | 3        |  |

| 0111                           | 7        | 0010     | 2        |  |

| 1000                           | 8        | 0001     | 1        |  |

| 1001                           | 9        | 0000     | 0        |  |

7486). The NOR gate used in the circuit is inevitable, but it can be replaced by a resistance-transistor logic (RTL) circuit or any other equivalent circuit.