#### A HEXADECIMAL KEYBOARD ENCODER

The simple hex keyboard encoder described in this month's column can be significantly improved by adding a 4-bit register to store the hex code of the key that has been pressed. This means the LED readout will display the 4-bit code for a particular switch when the switch is initially closed and continue to display it after the switch has been released. The display will change only when the scanning circuit detects a new key closure.

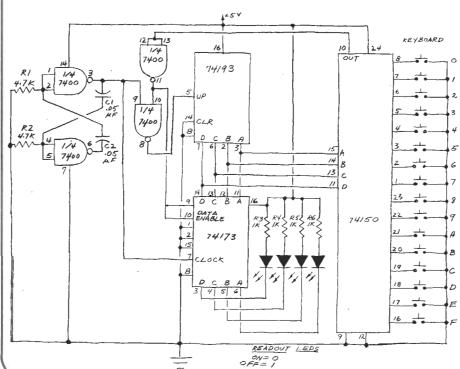

Compare the complete circuit diagram for the hex encoder shown here with Fig. 7 and you'll note that a 74173 4-bit register has been added and the readout LEDs have been moved from the counter output to the register output.

The clock and scanner portions of the circuit have already been analyzed, and the 74173 was described in the March 1978 Experimenter's Corner. It's a flexible storage register with 3-state outputs that can be readily tied to the address or data

bus of a microcomputer or controller.

When the scanner circuitry detects a switch closure, the output of the 74150 sends a data enable pulse to the 74173 through one of the 7400 gates. The next clock pulse then loads the counter address into the 74173, and the circuit resumes its sequential scan of the switches. The four bits describing the previously closed switch, however, remain safely stored in the register.

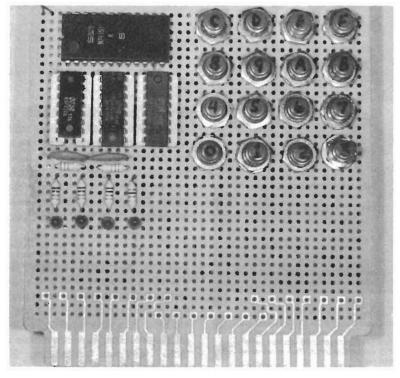

The photograph shows a prototype version of the encoder assembled on a perforated board (Radio Shack 276-152 or equivalent). Note the extra space on the board for the addition of other circuits such as a RAM. Also note that a standard calculator keyboard was not used. These keyboards are inexpensive and readily available, but the switches are arranged in x-y format not compatible with this circuit. Instead, individual normally open pushbutton switches were used to make a custom hex keyboard.

I used wrapped-wire construction throughout with the exception of solder connections to the switch terminals, the LEDs and several of the resistor and capacitor leads. Total assembly time was about three hours. In a subsequent Project of the Month we'll add a 16-word RAM to the encoder. You'll find the resulting circuit very interesting, so be sure to consider building the basic encoder in the meantime.

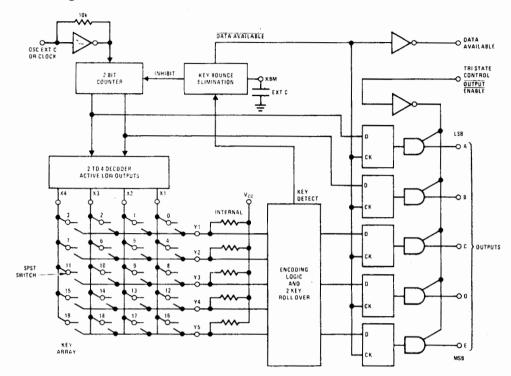

### THE 74C922 (16 KEY) AND 74C923 (20 KEY) ENCODERS

These CMOS key encoders provide all the necessary logic to fully encode an array of SPST switches. The keyboard scan can be implemented by either an external clock or external capacitor. These encoders also have onchip pull-up devices which permit switches with up to 50 kilohm on resistance to be used. No diodes in the switch array are needed to eliminate ghost switches. The internal debounce circuit needs only a single external capacitor and can be defeated by omitting the capacitor. A Data Available output goes to a high level when a valid keyboard entry has been made. The Data Available output returns to a low level when the entered key is released, even if another key is depressed. The Data Available will return high to indicate acceptance of the new key after a normal debounce period; this two key roll over is provided between any two switches.

An internal register remembers the last key pressed even after the key is released. The tristate outputs provide for easy expansion and bus operation and are LPTTL compatible.

#### typical applications

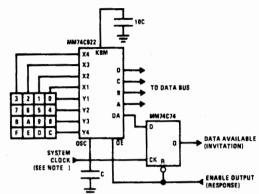

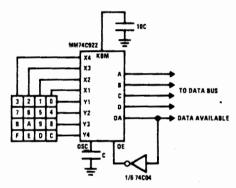

#### Synchronous Handshake (MM74C922)

#### Synchronous Data Entry Onto Bus (MM74C922)

Outputs are enabled when valid entry is made and go into TRI-STATE when key is released.

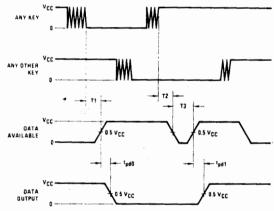

#### switching time waveforms

T1  $\simeq$  T2  $\approx$  RC, T3  $\approx$  0.7 RC where R  $\simeq$  10k and C is external capacitor at KBM input.

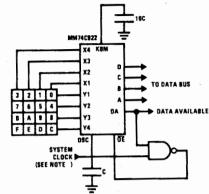

#### Asynchronous Data Entry Onto Bus (MM74C922)

Outputs are in TRI-STATE until key is pressed, then data is placed on bus. When key is released, outputs return to TRI-STATE.

Note: The keyboard may be synchronously scanned by omitting the capacitor at osc, and driving osc, directly if the system clock rate is lower than 10 kHz.

#### dc electrical characteristics Min/max limits apply across temperature range

| PARAMETER       |                                    | CONDITIONS                                                  | MIN | TYP  | MAX  | UNITS |

|-----------------|------------------------------------|-------------------------------------------------------------|-----|------|------|-------|

| CMOS TO CMOS    |                                    |                                                             |     |      |      |       |

| l <sub>rp</sub> | Row Pull-Up Current at Y1, Y2, Y3, | V <sub>CC</sub> = 5V, V <sub>IN</sub> = 0.1 V <sub>CC</sub> |     | 2    | -5   | μΑ    |

| -               | Y4 and Y5 Inputs                   | VCC = 10V                                                   |     | -10  | -20  | μΑ    |

|                 |                                    | V <sub>CC</sub> = 15V                                       |     | -22  | -45  | - µА  |

| Ron             | Column "ON" Resistance at          | V <sub>CC</sub> = 5V, V <sub>O</sub> = 0.5V                 |     | 500  | 1400 | Ω     |

|                 | X1, X2, X3 and X4 Outputs          | V <sub>CC</sub> = 10V, V <sub>O</sub> = 1V                  |     | 300  | 700  | Ω     |

|                 |                                    | V <sub>CC</sub> = 15V, V <sub>O</sub> = 1.5V                |     | 200  | 500  | Ω     |

| icc             | Supply Current                     | VCC = 5V, Osc at 0V                                         |     | 0.55 | 1.1  | mA    |

|                 |                                    | V <sub>CC</sub> = 10V                                       |     | 1.1  | 1.9  | m A   |

|                 |                                    | V <sub>CC</sub> = 15V                                       |     | 1.7  | 2.6  | mA    |

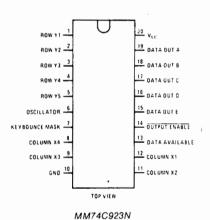

#### connection diagrams

# ROW Y1 1 1 18 Vcc ROW Y2 2 17 DATA DUT A 16 DATA DUT B 15 DATA DUT C 14 DATA DUT D 15 DATA DUT D 13 DUTPUT ENABLE 12 DATA AVAILABLE COLUMN X4 2 11 COLUMN X2 TOP VIEW MM74C922N

block diagram

#### features

- 50 kΩ maximum switch on resistance

- On or off chip clock

- On chip row pull-up devices

- 2 key roll-over

- Keybounce elimination with single capacitor

- Last key register at outputs

- TRI-STATE outputs LPTTL compatible

- Wide supply range 3V to 15V

- Low power consumption

## **BINDERS**

In response to many requests from our readers we have arranged for binders to be made so that you can keep ETI's first Canadian volume together and protected from damage. The binders are covered in attractive leather-look black plastic and are designed to hold twelve issues. The ETI design is printed in gold letters on the spine.

The binders cost \$6.00 each, which includes postage and packaging. Do not send cash — you can pay by cheque. Mastercharge, or Chargex Credit card orders must include your account number, the expiry date, and your signature. In all cases allow six weeks for delivery Send your order to ETI Binders. Unit 6, 25 Overlea Blvd., Toronto, Ontario M4H 181. Don't forget to include your name and address.

Ontario residents add PST.