:

# CSQ-100 SERVICE NOTES

Memory capacity ---- Up to 168 notes (84 notes/channel) 2 channels CV output ----- 1V/oct: -2V to +8V CV input ----- 1V/oct: OV to +5V Gate output ----- Off: OV On: +15V Gate input -- ---- Off: OV On: +15V (threshold +2.5V) EXT Start input ---- With switch: normally close, open to start or pulse: +15V EXT Step input ----- +15V pulse Power consumptions -- 8 watts Dimensions ------ 345W x 305D x 95H mm (13.6 x 12.0 x 3.7 in) Weight ----- 2.7 kg (5.94 lbs)

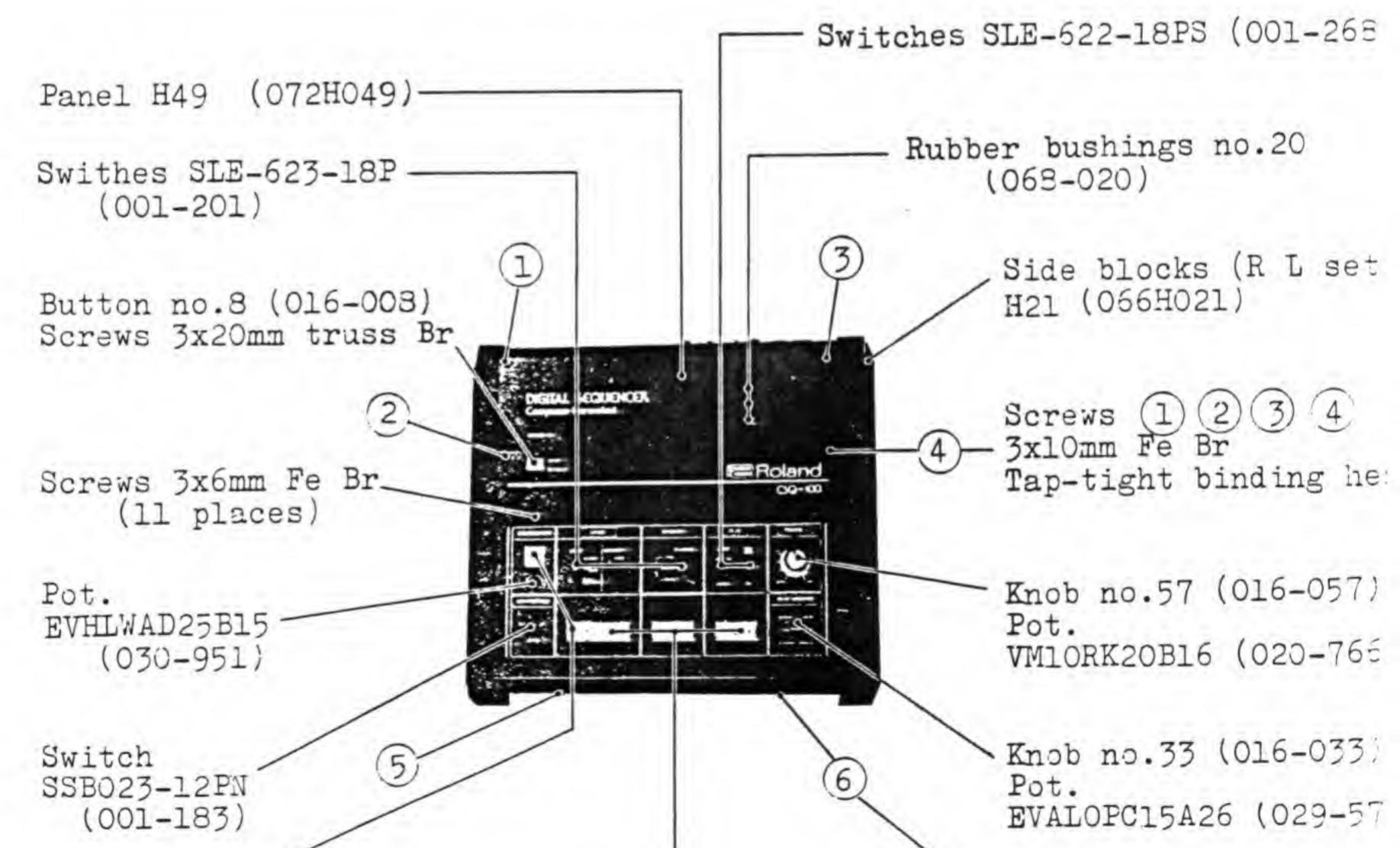

PANEL REMOVAL SCREWS: (1) through (8) ((7)(8) on the rear)

(6) Switches w/button SCK41168(001-275) (5)Screws Switches 3x6mm Fe Br bindind w/button specify legend for replacement SCK41167 order (001 - 276)

Feland

A3 Printed in Japan

**CSQ-100**

Switch

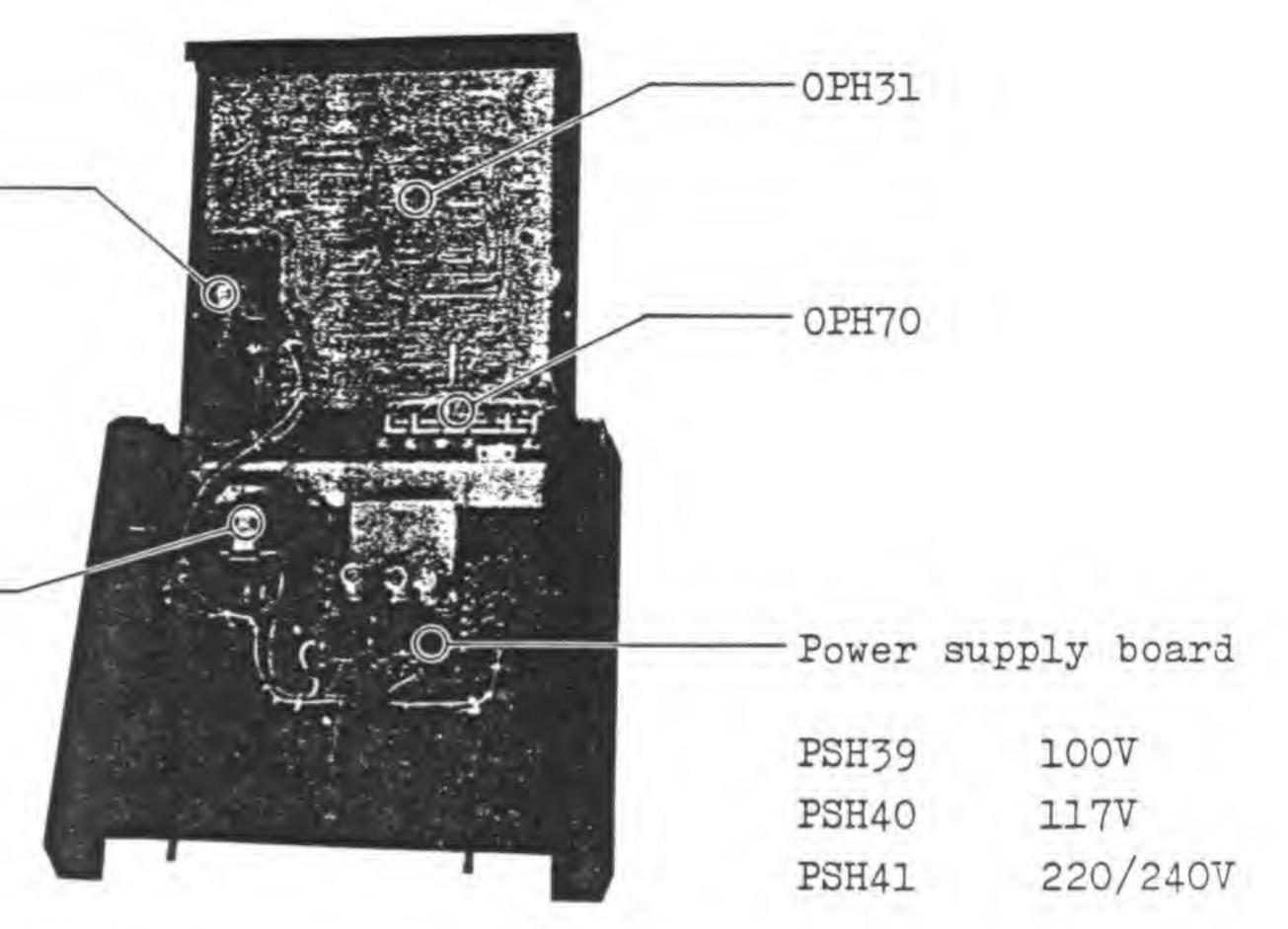

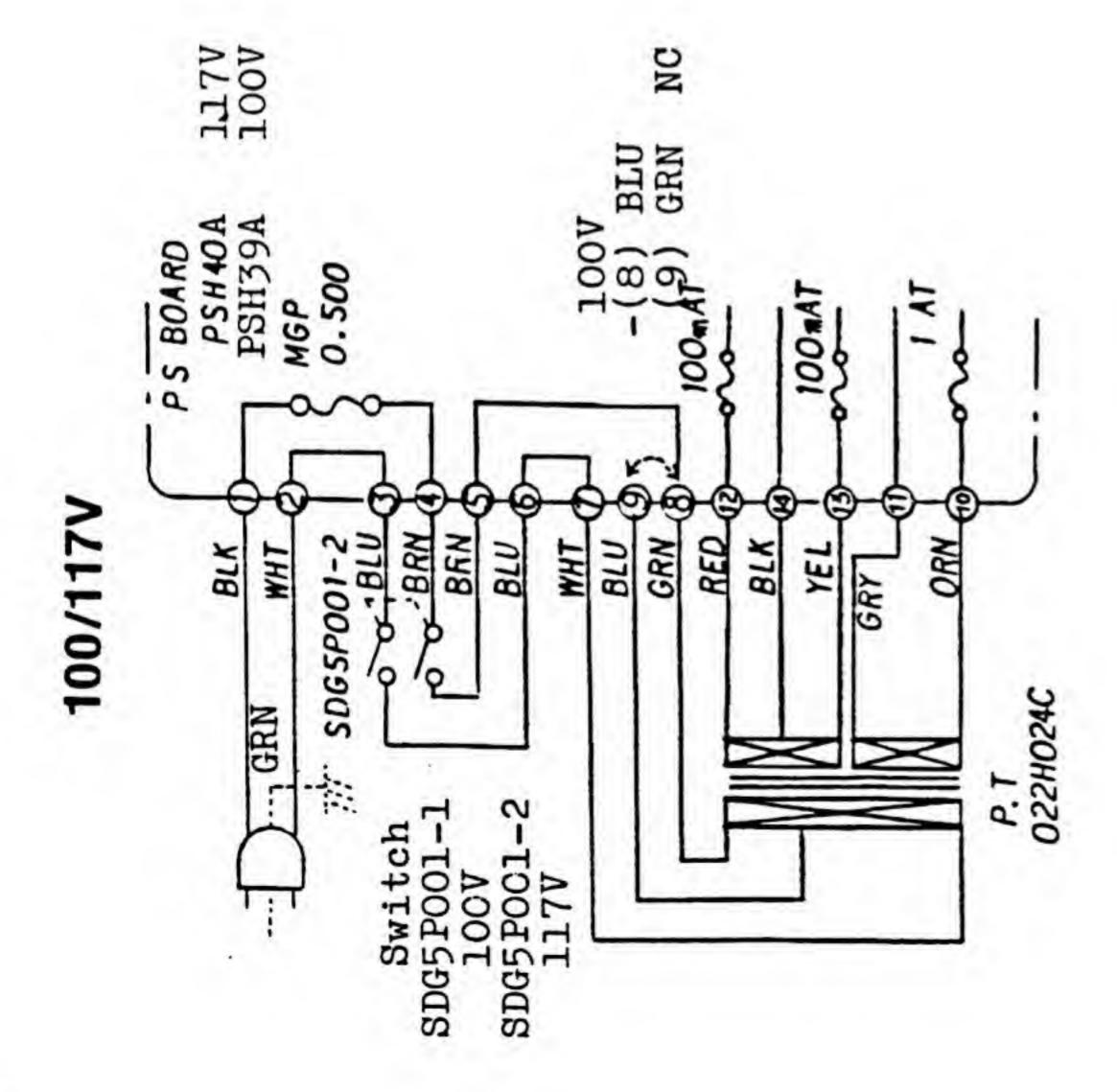

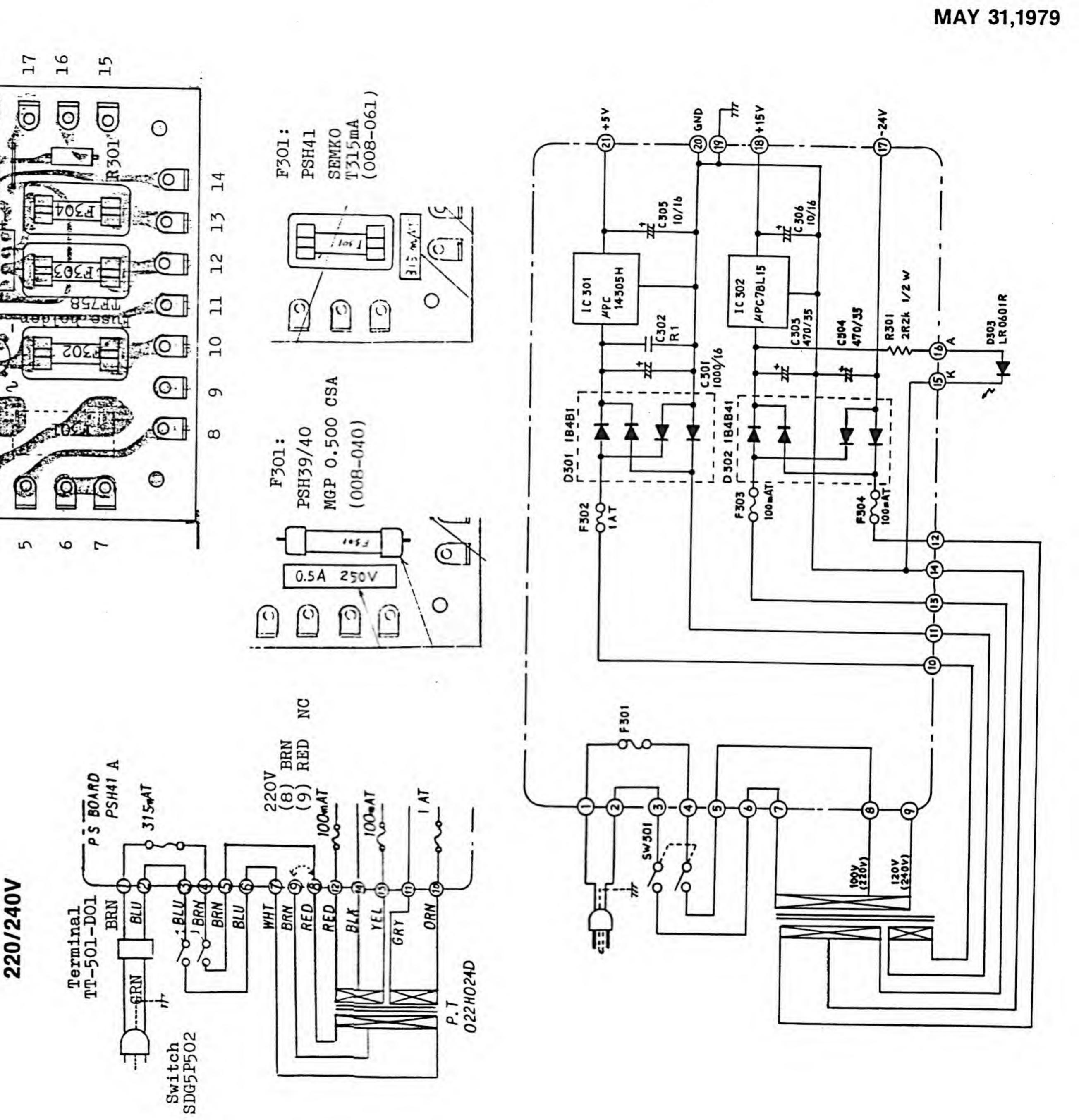

SDG5P 001-1 (001-215) 100V SDG5P 001-2 (001-216) 117V SDG5P-502 (001-217) 220/240V

Power transformer 100/117V 022H024C 220/240V 022H024D

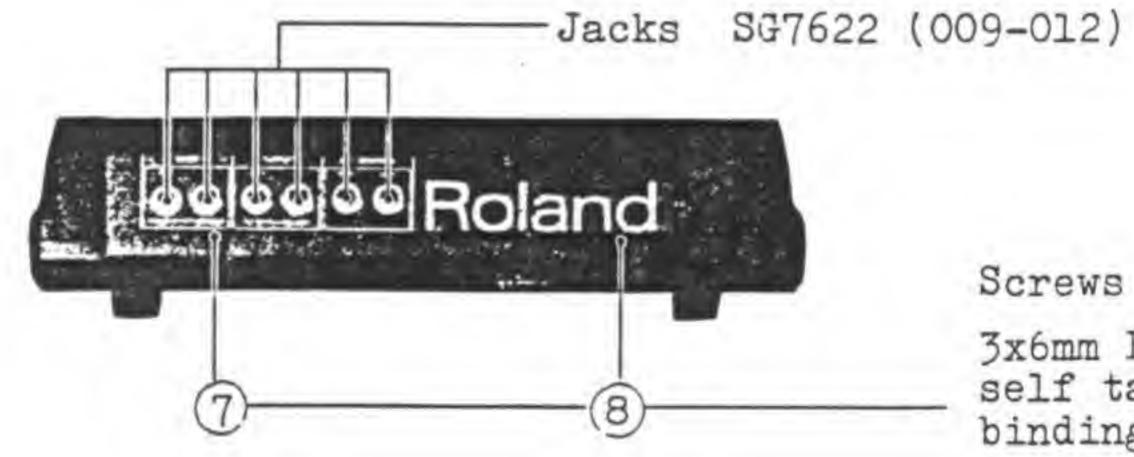

3x6mm Bl Fe Br self tapping binding head

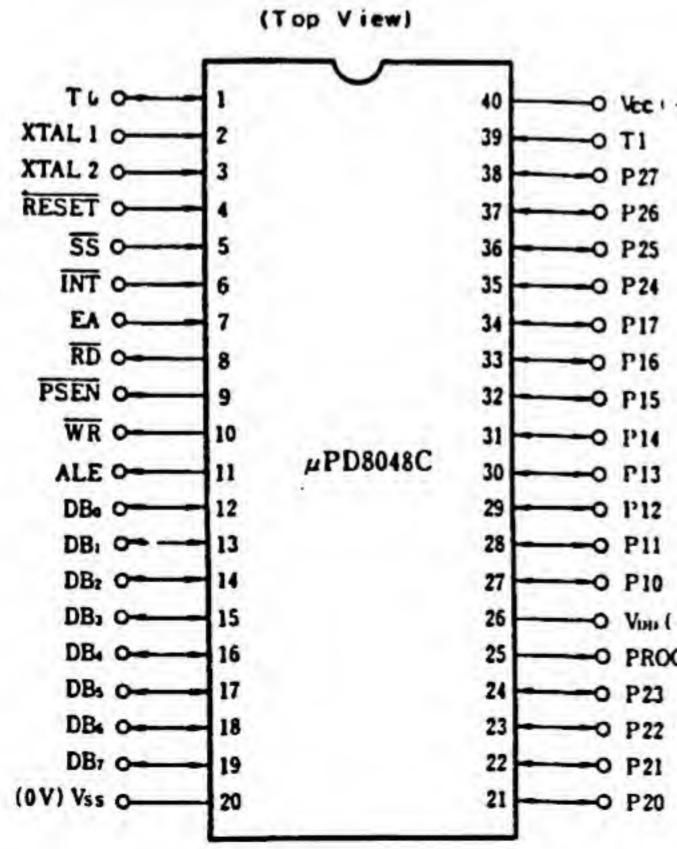

# μ PD8048 Pin Description

| Designation |     | Pin<br>No. | Function    |

|-------------|-----|------------|-------------|

| DB          | DBO | 12 -       | -           |

| (Data bus)  | 1   | 13         |             |

|             | 2   | 14         |             |

|             | 3   | 15         | CV data     |

|             | 4   | 16         | uata        |

|             | 5   | 17         |             |

|             | 6   | 18-        | 1           |

|             | 7   | 19         | Output Ga   |

| Pl          | P10 | 27         |             |

| (Port 1)    | 11  | 28         | RAM addre   |

|             | 12  | 29         |             |

|             | 13  | 30         | RAM addres  |

|             | 14  | 31         | LED timin,  |

|             | 15  | 32         | Output CV   |

|             | 16  | 33         |             |

|             | 17  | 34         | Metronome   |

| P2          | P20 | 21         |             |

| (Port 2)    | 21  | 22         |             |

|             | 22  | 23         | CV IN by-   |

|             | 23  | 24         |             |

|             | 24  | 35 -       | 1           |

|             | 25  | 36         | Read swit   |

|             | 26  | 37         |             |

|             | 27  | 38 -       |             |

| RESET       |     | 4          | Input to r  |

| INT         | 1.3 | 6          | External g  |

| TO          |     | 1          | Digital da  |

| Tl          |     | 39         | Accepts TH  |

| XTAL 1      |     | 2          | External s  |

| XTAL 2      |     | 3          | DAVET HAL S |

2

1.1

.

| CC + 5V)  |                                    |

|-----------|------------------------------------|

| F1        | The uPD8048 is an 8-bit parallel   |

| P27       | computer fabricated on a single    |

| P26       | sillicon chip. The 8048 contains a |

| P25       |                                    |

| P24       | 1k x 8 ROM program memory, 27 I/O  |

| P17       | lines, an 8-bit timer/counter and  |

| P16       | clock circuits.                    |

| P15       | Used in the CSQ-100 is a uPD8048C- |

| P14       | 028 version in which program and   |

| P13       |                                    |

| P12       | data dedicated to the CSQ-100 are  |

| P11       | stored in the program memory.      |

| P10       |                                    |

| Von (+5V) |                                    |

| PROG      |                                    |

| P23       |                                    |

| P22       |                                    |

| P21       |                                    |

|           |                                    |

.

3

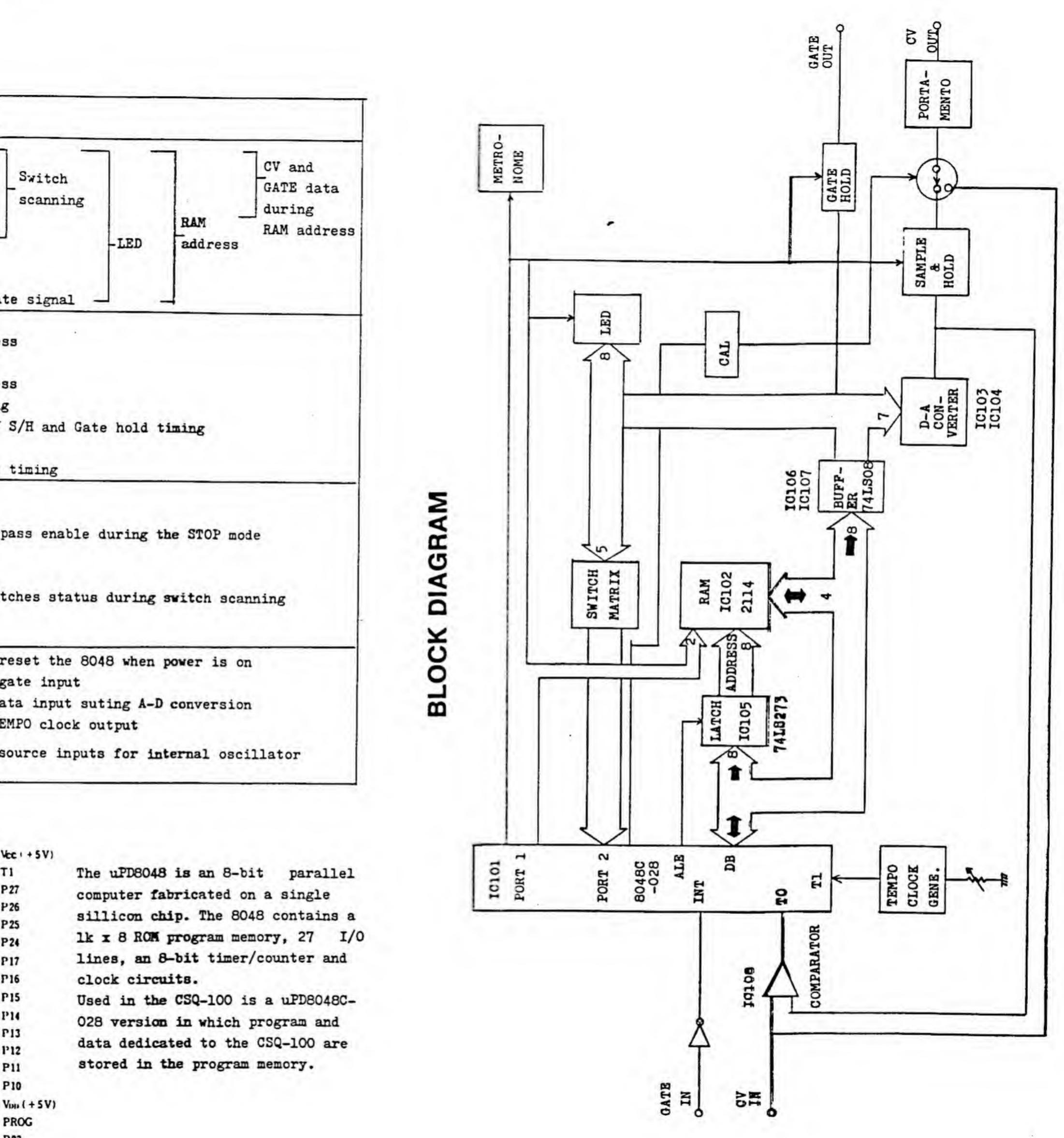

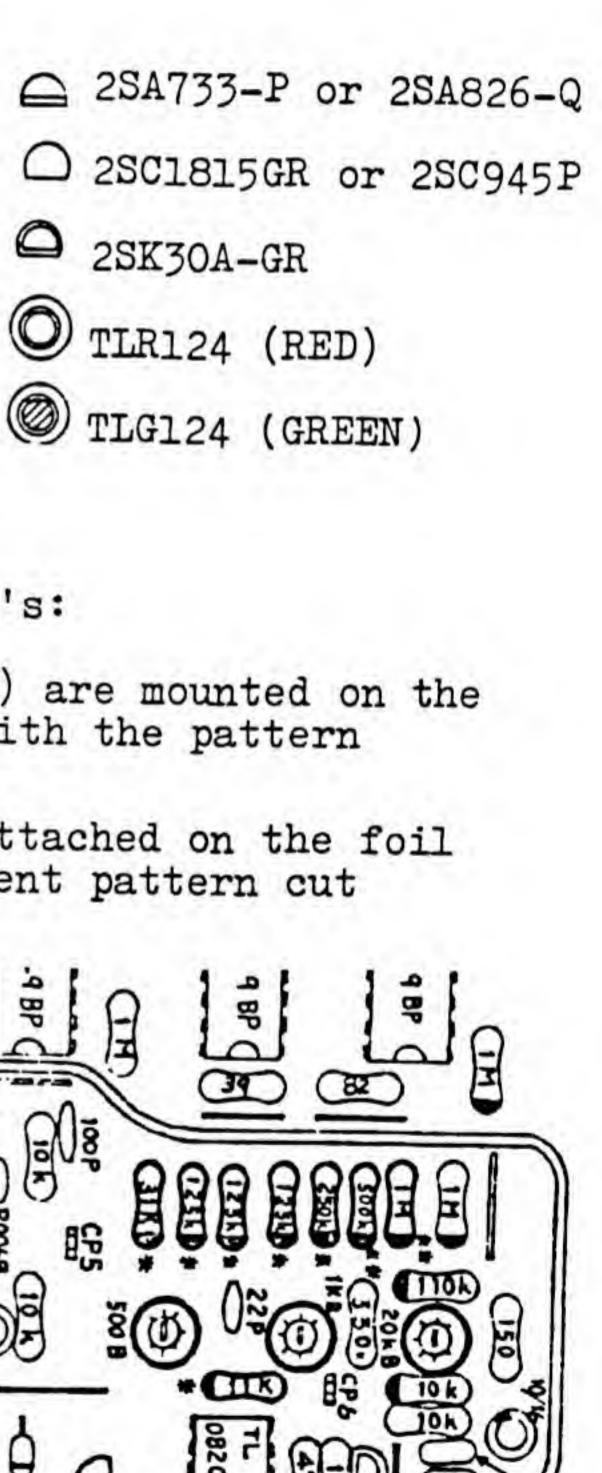

# **CIRCUIT DESCRIPTION**

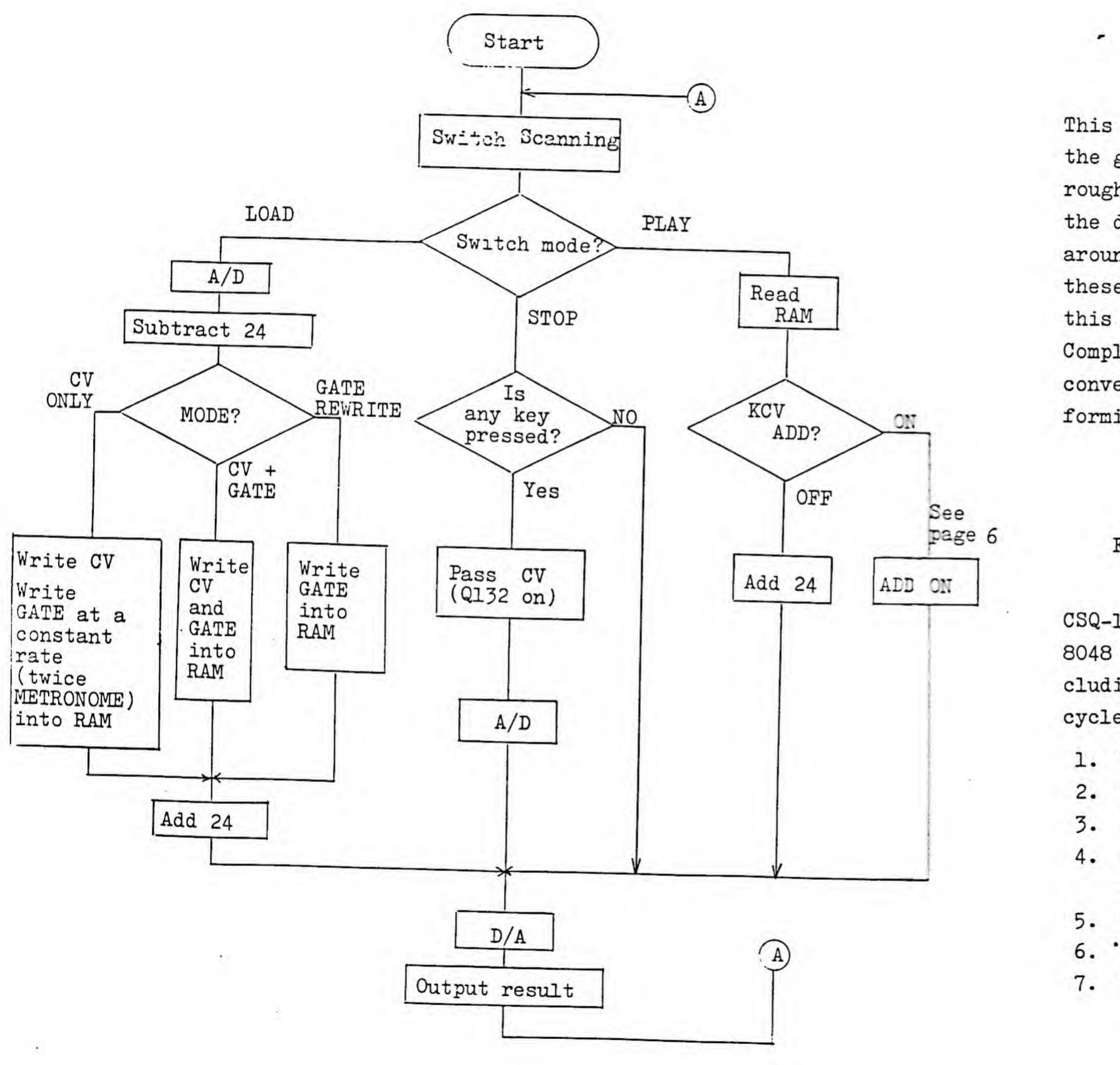

This description is divided into parts: the general description which explains roughly the functions of CSQ-100, and the detailed description which centers around A/D and D/A converters since these are practically the heart in this instrument.

Complete unserstanding of A/D and D/A conversion circuits will aid in performing adjustments in Section II.

# Function of " One chip computer" uPD8048

CSQ-100 performes its functions with uPD-8048 at the center position for all, including the following in its performance cycles:

Switch Scanning

D/A Conversion

A/D Conversion

Write/Read of Data to or from External RAM

Timing for lighting LED Indicator

Triggering of METRONOME

Holding of GATE OUT

.

### GENERAL

1. SWITCH SCANNING

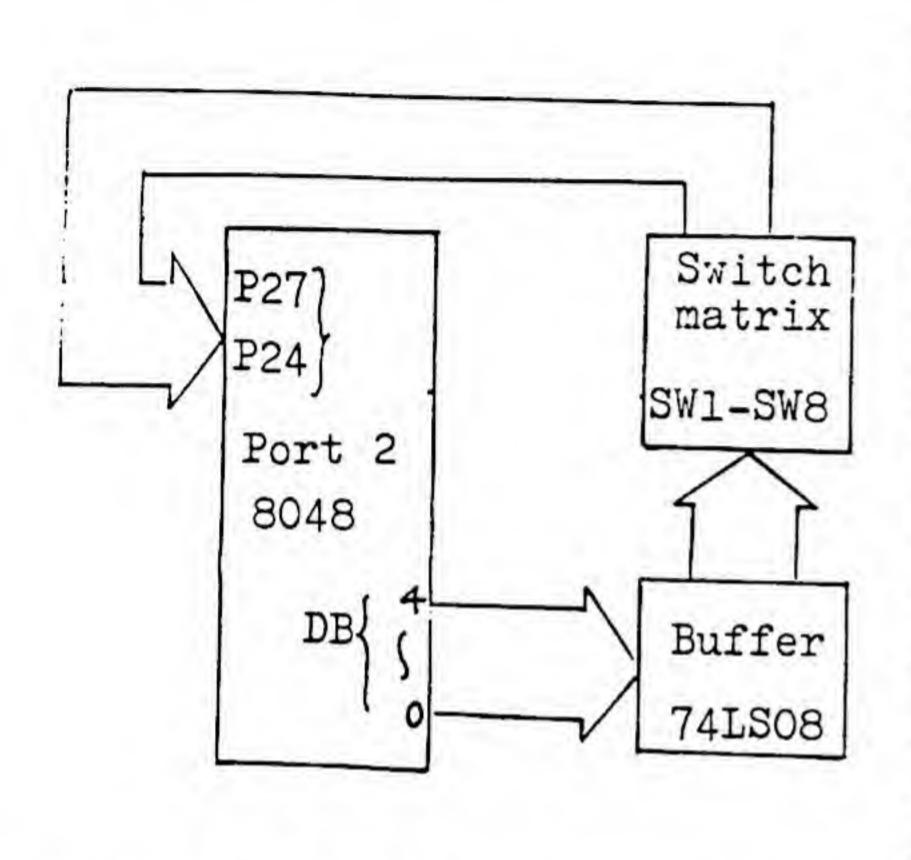

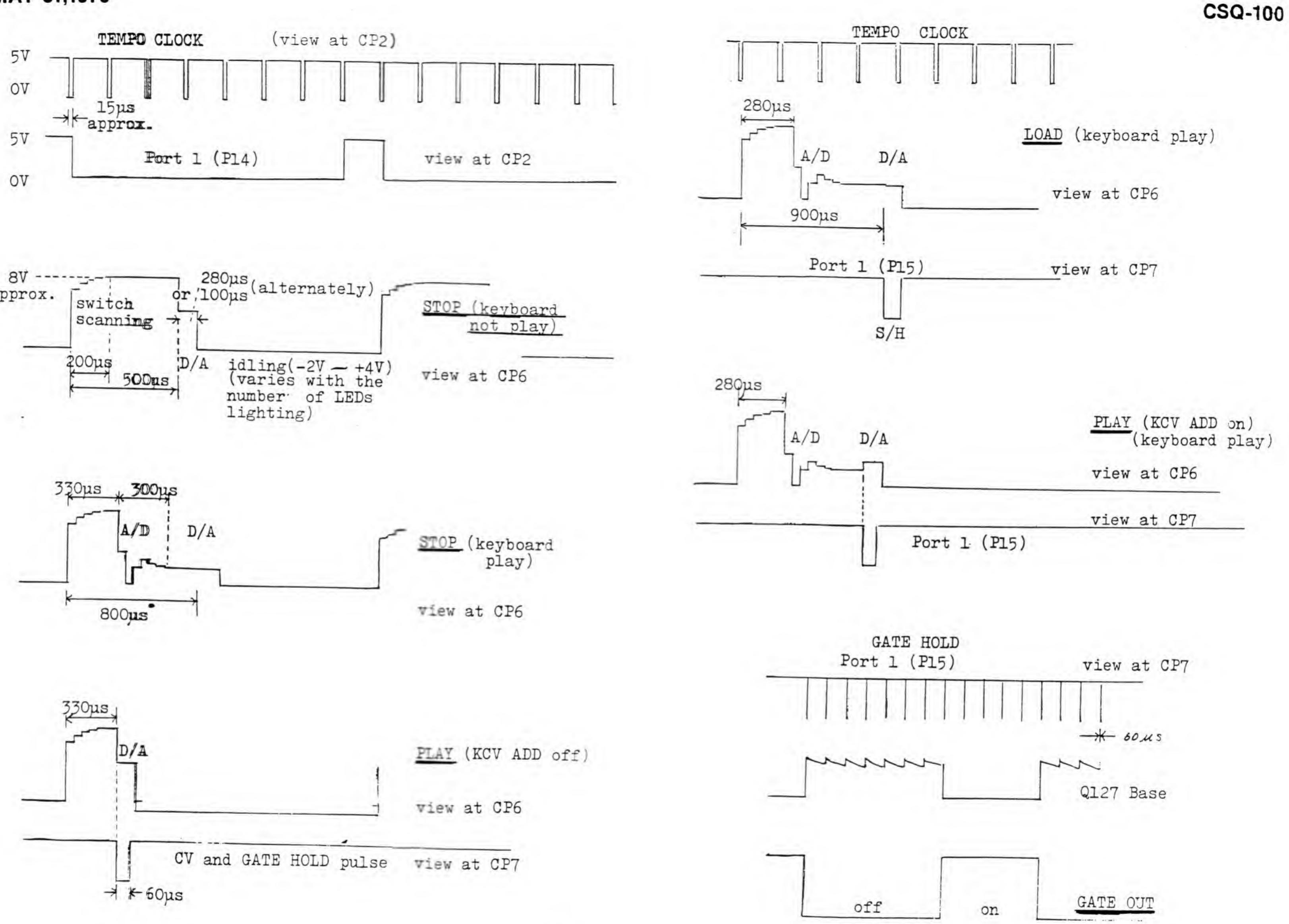

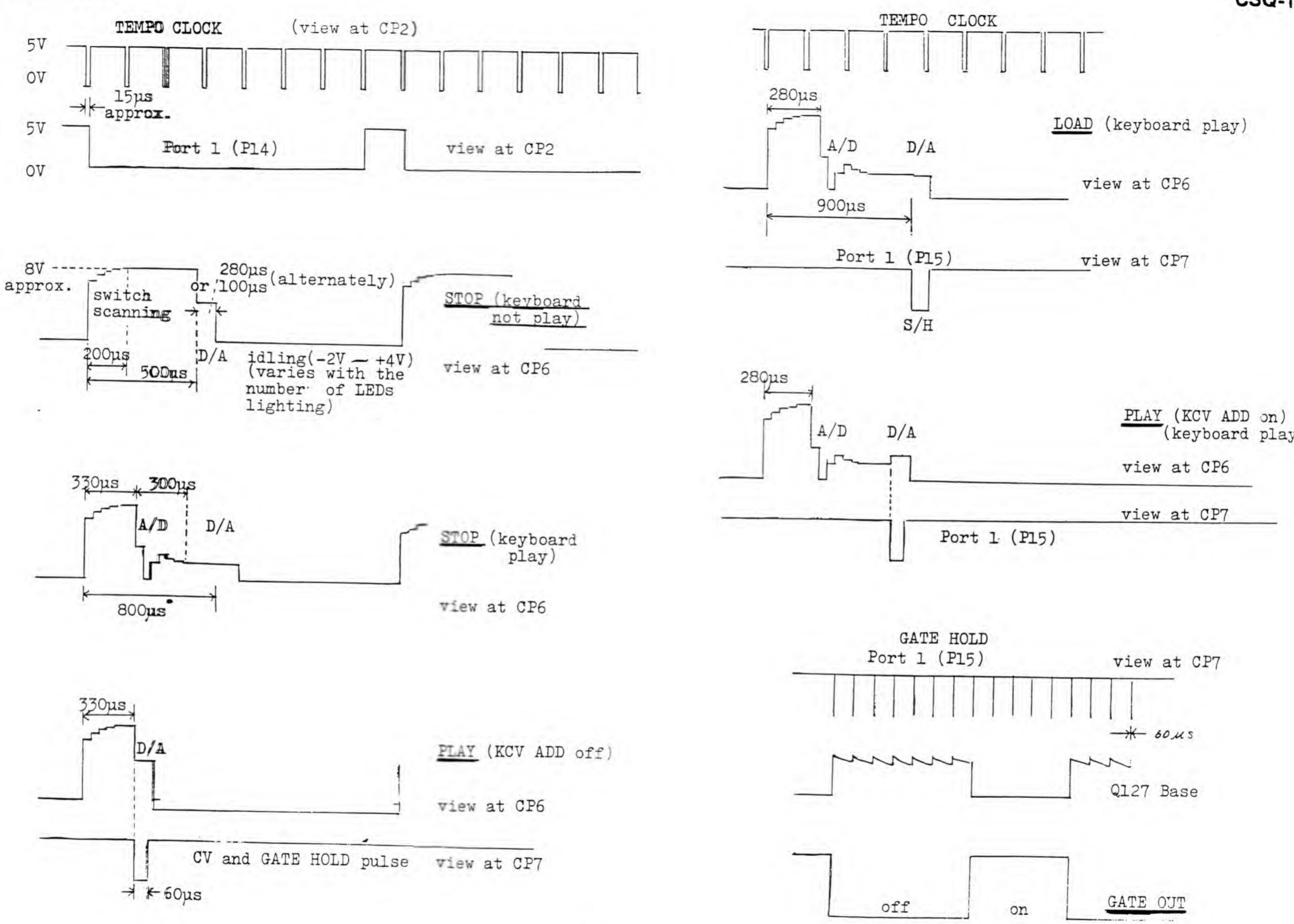

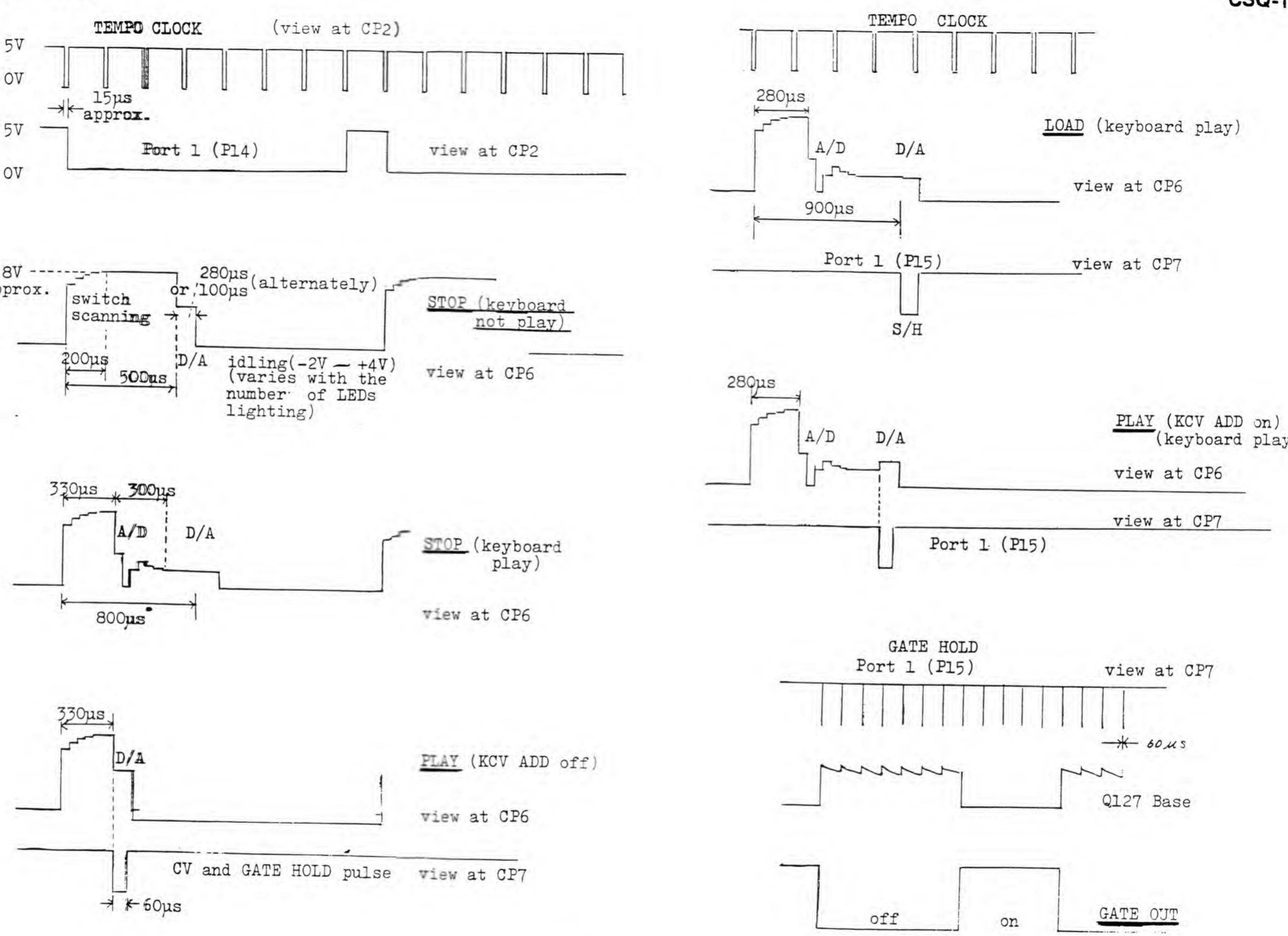

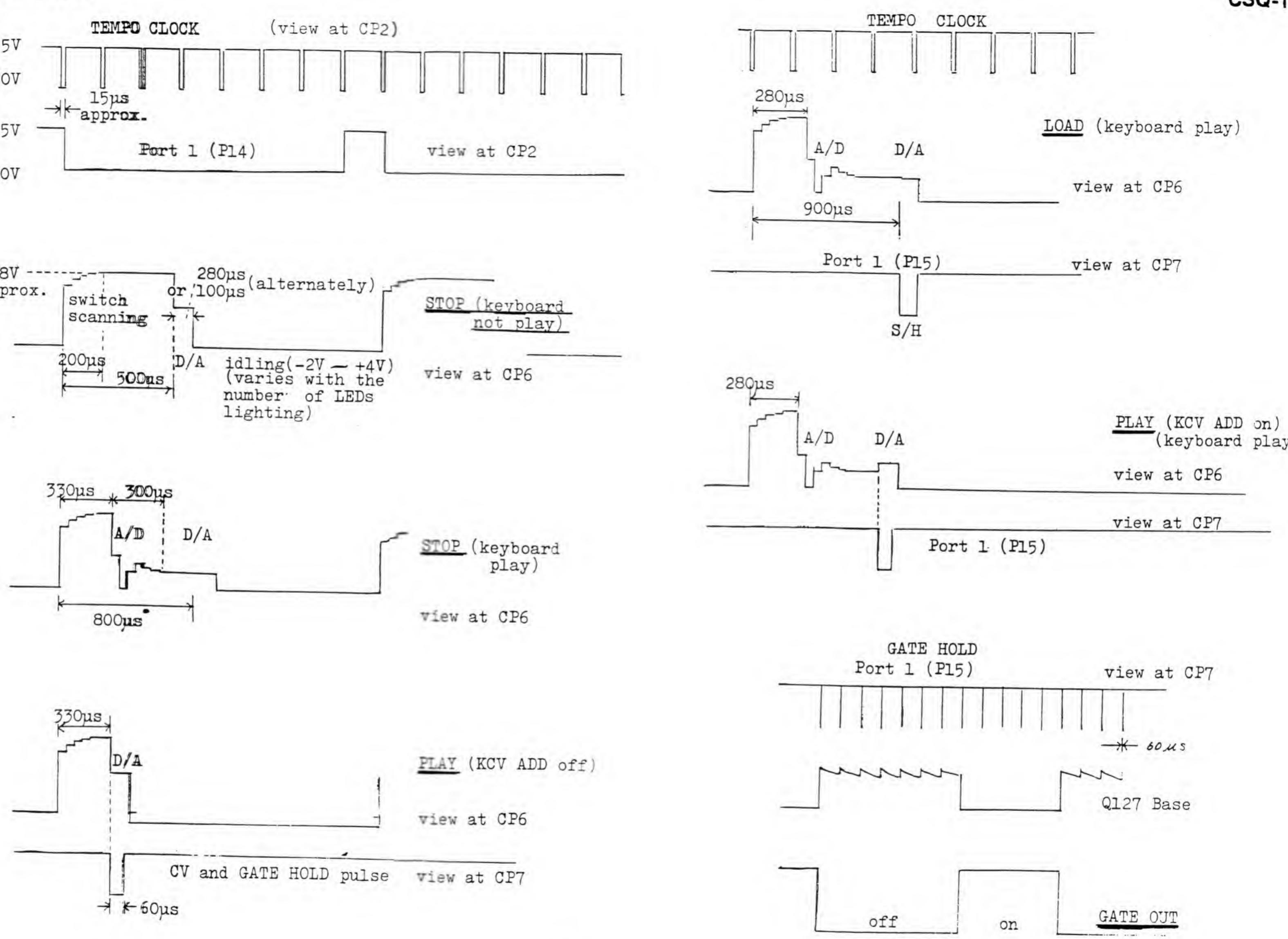

µPD8048 starts its running cycles beginning with switch canning. Into DBO-DB4 (Data Bus) of 8048, 5bit signals are being output according to the internal program, which are then brought to the switch matrix through the buffer. At first, L is output from DB4 while having H from other DBO to DB3. At the next instant, DB3

becomes to L while others change to H; and still next L on DB2 and so on, repeating such output changes 5 times on these bit signal combinations.

Depending on which key is depressed or in what position the switches are, corresponding signals are fed back through P24-P27 on Port 2.

2. D/A CONVERSION - Digital to Analog -

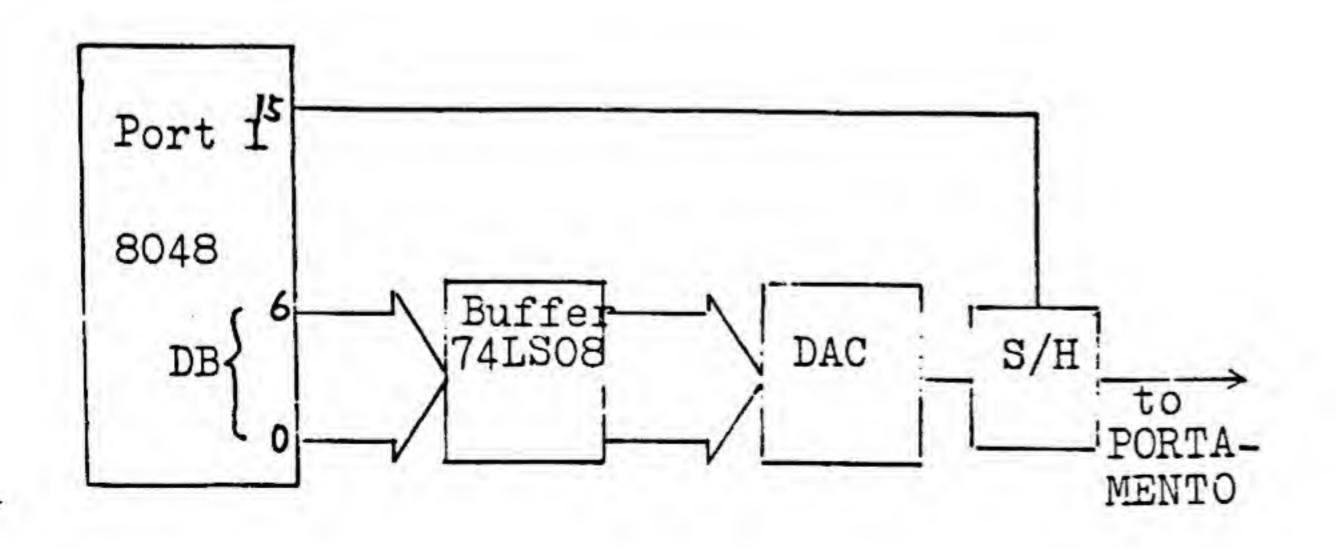

The D/A converter transforms the sequential data (switch scanning, RAM address, CVs, etc.) which are being output from the 8048 through internal programming, into analog voltages. Since the D/A converter (DAC) employed here is a summing type, with a weight-resistor-tree connected to an inverting input of an OP amp, each bit in the digital data is converted to an analog voltage in value to double the one immediately subordinate to each. When CV data are on output, pulses synchronized to CV data are supplied from P15 of Port 1 onto the Sample and Hold (S/H) circuit, and the analog CV voltage equivalent to the data are held on Cl24. (details disccused later)

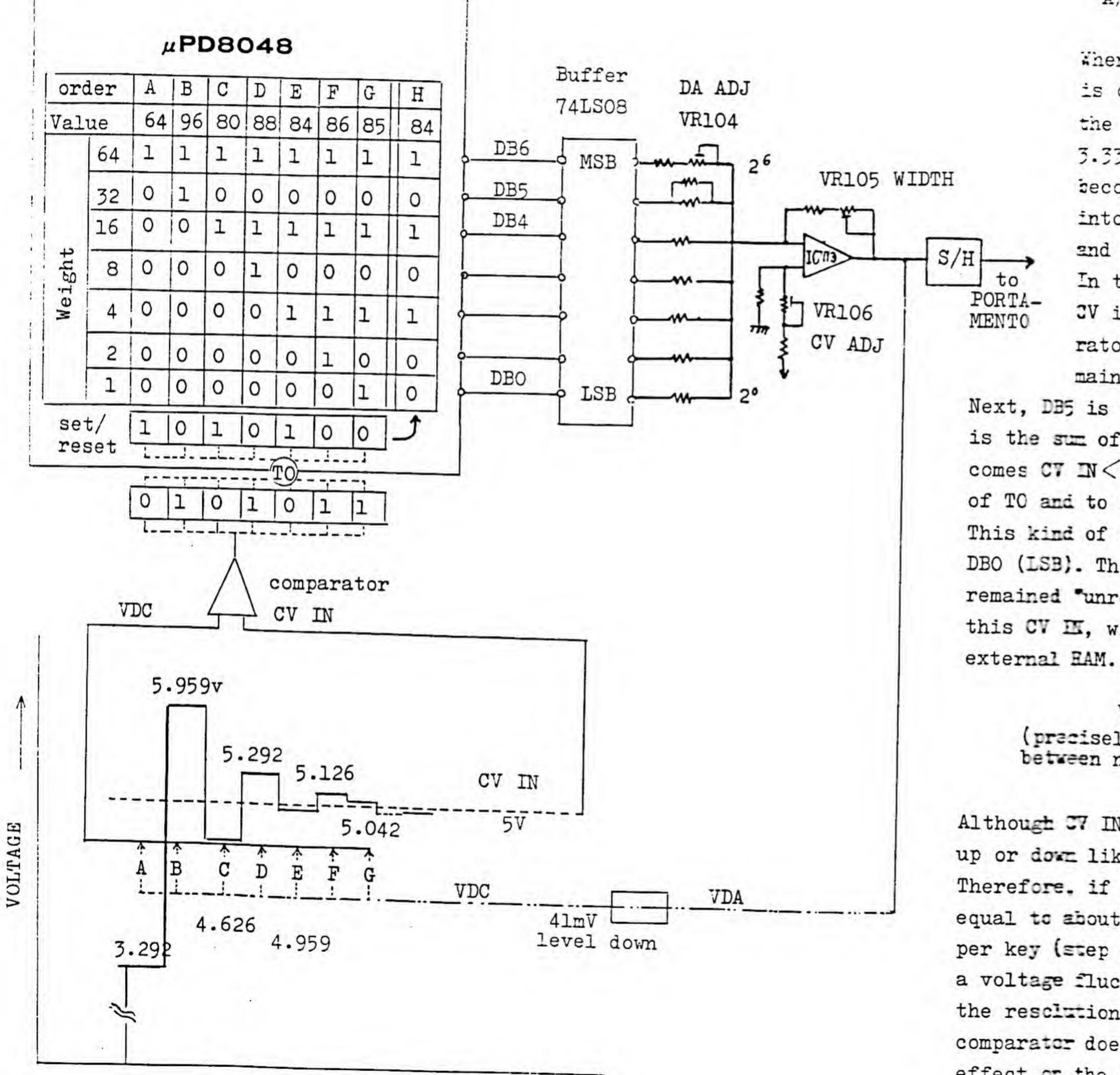

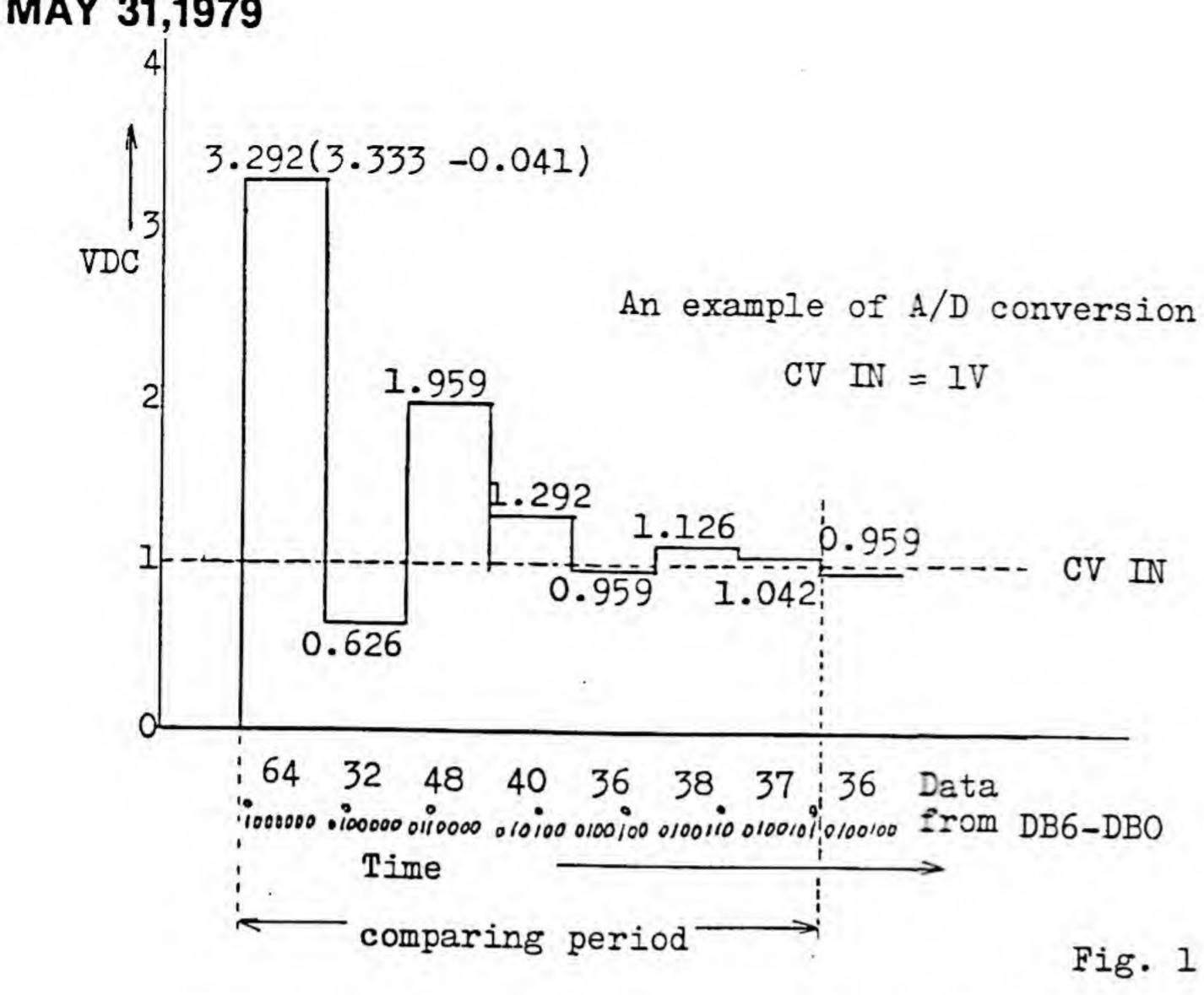

# 3. A/D CONVERSION (Analog to Digital)

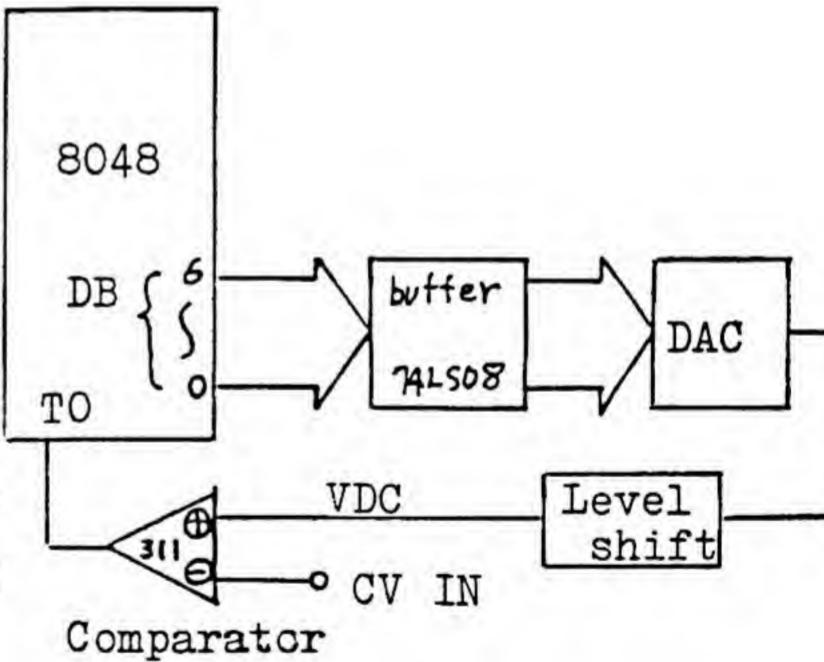

Since the CV IN is an analog voltage, it must be converted to digital data for making the storing in RAM possible. 8048 The method employed in the CSQ-100 is called "successive buffer DB DAC approximation conversion" where 742508 TO each bit, from DB6(for MSB; most significant bit) to DBO(for LSB; VDC Level 311 shift least significant bit), is being e - CV IN set successively to output "1" Comparator which, after being D/A converted. is to be compared with CV IN at the comparator (311). The comparator will then output "O" (low) if CV VDC, or "1" (high) if CV VDC, onto TO. When H is output to TO, the corresponding digital data is "reset" and becomes 0. Such set and "reset" is repeated 7 times for bits from DB6 to DBO and with the resultant value from such "set" "reset" the digital data of the CV IN is produced.

# MAY 31,1979

#### MAT 31,1979

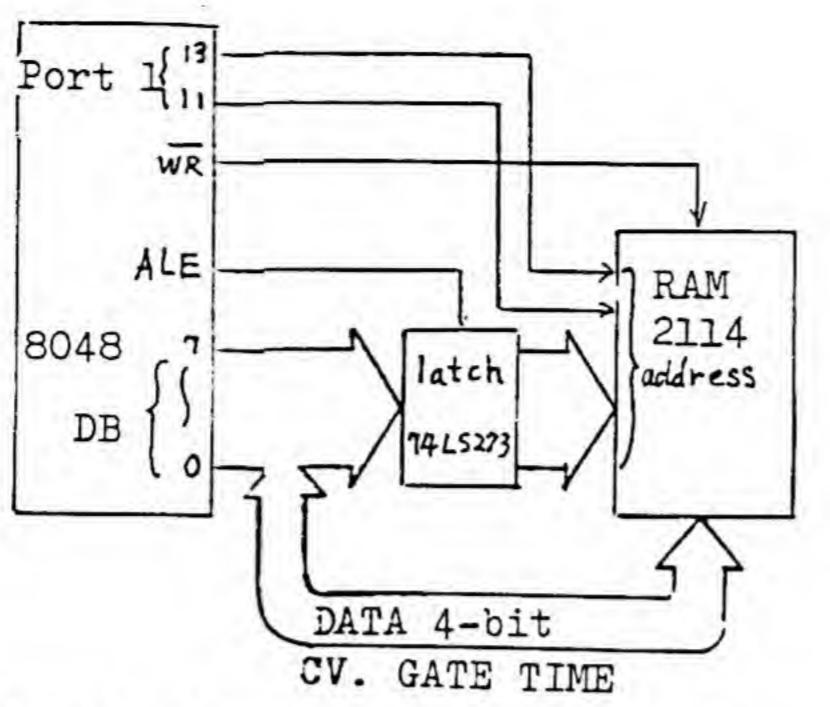

4. DATA (CV and GATE TIME) WRITE/READ to RAM

In the external RAM, memory cells are selected by the signal made in combination of the address signals latched on 74LS273 by the instruction signal from ALE (Address Latch Enable) and those from P11 and P13. The data (CV and GATE TIME) are written when WR is "low" and are read when it is "high". Although the data are in 8-bit format, they are written/read in two times separated to one-word-4-bit groups of lower and higher bits.

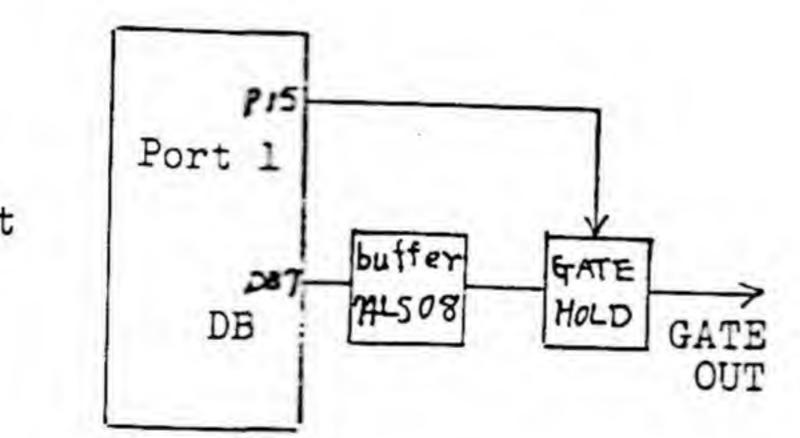

#### 5. GATE HOLD

From DB7, the GATE signals are also being output. They are held by the signal (the same as for S/H ) to become output of GATE signal.

# 6. LIGHTING of LEDS

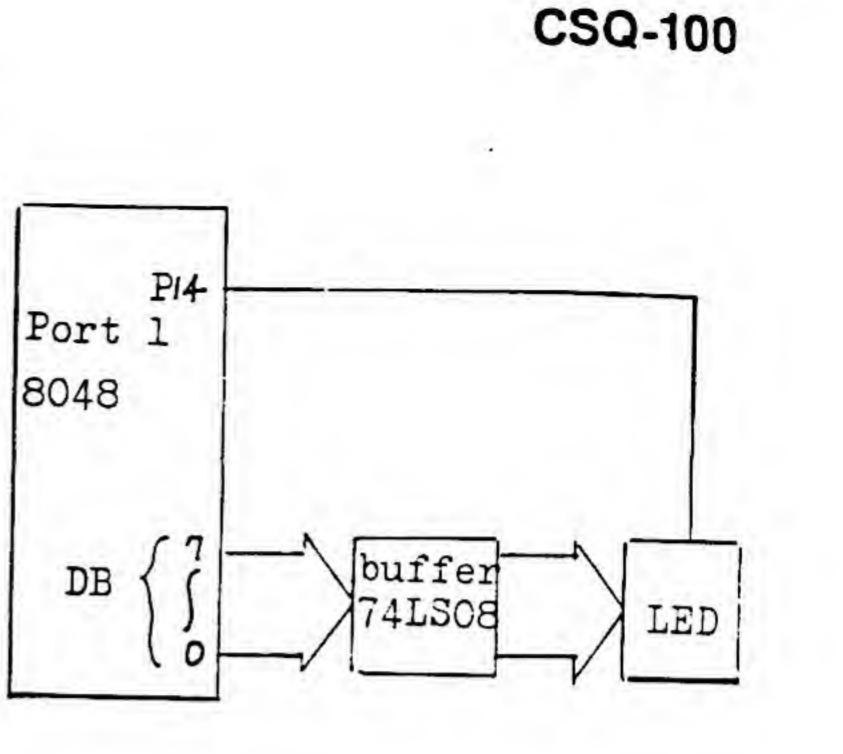

Signals for lighting LEDs (except TEMPO) are supplied from DB. However, because there are many signals on DB at every instance, timing pulses are given from P14 to control the LED circuits being fed only when there are output lighting signals.

The pulses are synchronized with those of TEMPO CLOCK GENERATOR and are output at the time rate one pulse for every eight CLOCK pulses. Because of this, lighting on/off cycling rate is also changed along with change in TEMPO, but the current amount to LED is still being kept unchanged through a means to maintain the duty ratio constant.

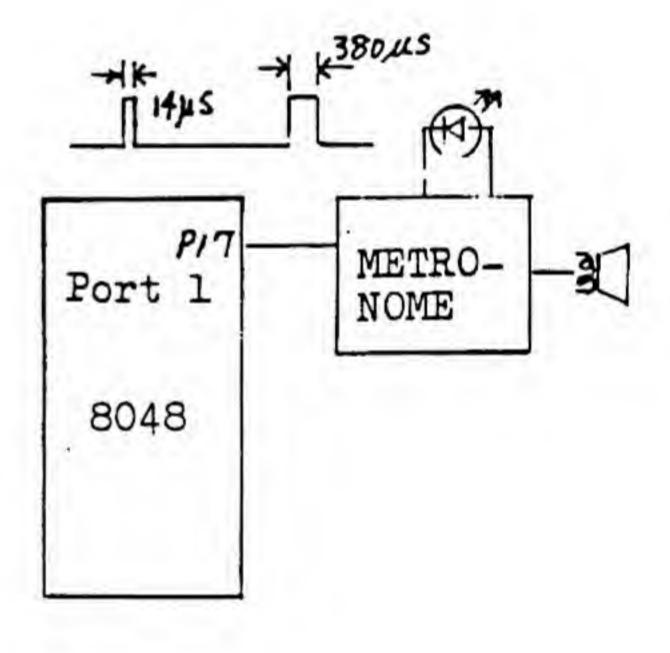

In LOAD mode, two pulses synchronized to TEMPO are being output ( in period 480 times the CLOCK pulse, in pulse widths of 14µs and 380µs for alternate output). METRONOME amp is driven by both pulses but since the shorter pulses of 14µs are filtered out by the integration circuit of R147 and C115 before arriving at LED, the longer pulses of 380us only are used for lighting the TEMPO LED.

### 7. METRONOME DRIVE

# LOAD

-

.

.

6

MAY 31,1979

.

.

# DESCRIPTION OF CICUIT FUNCTION DETAILS

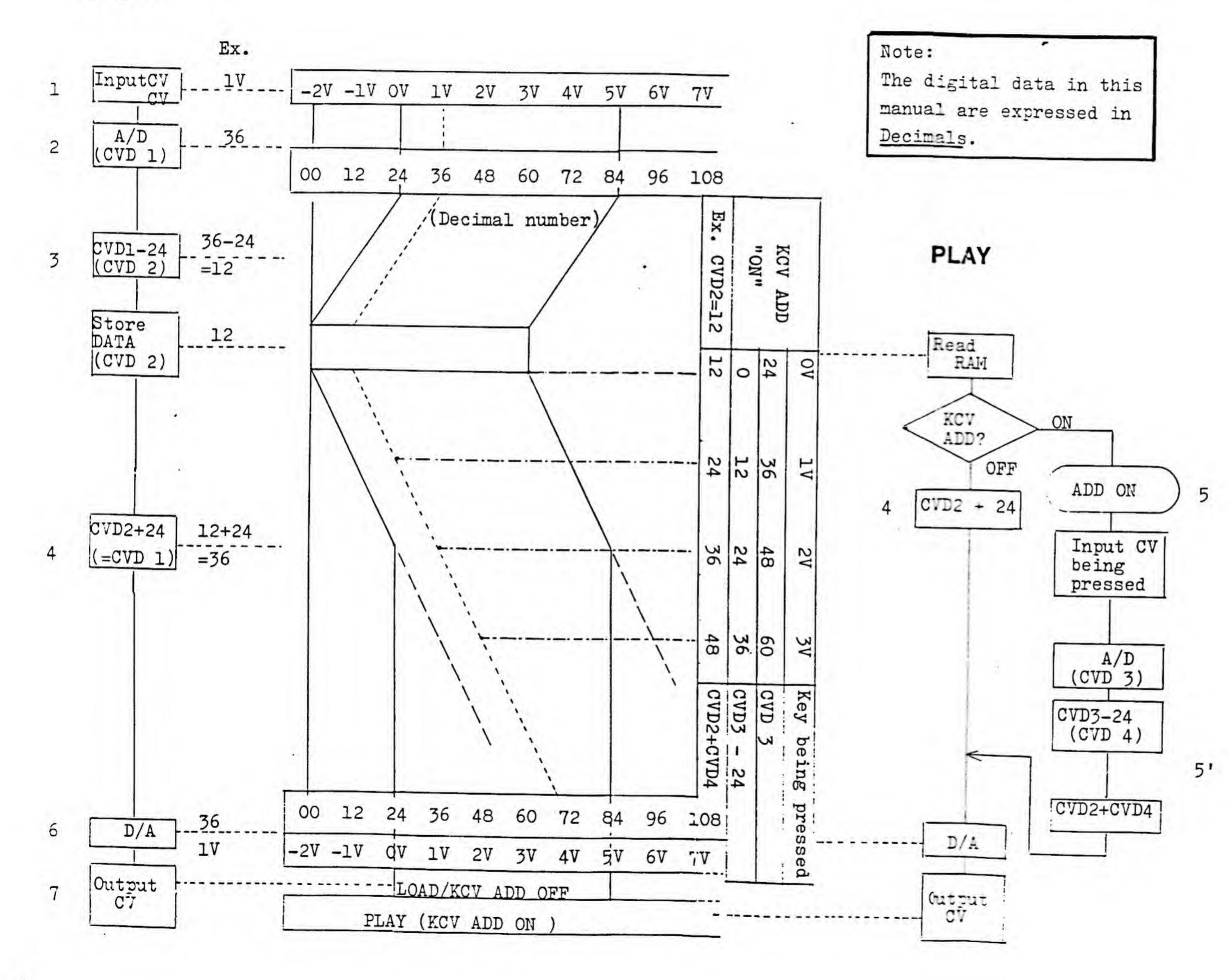

Since in the CSQ-100, the key voltage which are analog quantum are first converted to digital for storing in RAM and again afterward are converted to analog for CV OUT, these A/D and D/A conversions are just as important as the heart is to man. It might be said that without understanding of these conversion principles and pertinent analog vs digital data relationship, all adjustment services which are related to key voltage circuits become difficult to perform correctly. With this in mind, our description will proceed along with the line as numbered in the figure on the left page.

- 1. In the CSQ-100, the CV storage range runs from OV to +5V, 61 notes. or

- 3. The voltages that can be stored in RAM are 0 to -5V, which form to make OV = OO.( in decimal) The key voltage to correspond to th about 83.3mV.

- 4. Reproduction of CV in " \_\_\_\_\_ ] - LOAD or PT ..

which is the same as subtracted before storing, into the data of RAM, the same digital analog voltage can be reproduced after D/A conversion.

2. Due to the reason to be touched on later, the lowest CV which is provided by this CSQ-100 is -2V. Therefore the digital data are made to correspond to 00 = -2V.

makes the number of pitches to be 61 if taken in the ratio of lV/oct. Although, in handling them, 6 bits ( $2^{6} = 64$ ) are enough, 7 bits would become necessary for the key voltage on the upper range if started from OV = 24. For this reason, numbers 24 are being subtracted after conversion to digital

tal value "l" is

. ADD "off" ) -

CSQ-100 has the function to have a desired transposition of notes in PLAY mode by adding an external key voltage to the CV in memory. But, if transposition is required up or down, KCV must be varied also up or down from the center referenced by the key which produces on this mode the same orginal tones in pitch from the Memory. Also, because the CSQ-100 has set this shift down range to be within 2V, the key to produce KCV=2V is made the reference key. For instance, when OV is stored in Memory, pressing a OV key, the lowest, will produce transposed output voltage -2V. For this, the following must be true:

Digital data for OV stored in RAM (CV2 = 00 ) + KCV digital data of OV (CVD3 = 24 ) = 00 (-2V)

To satisfy the above, " CVD2 + CVD3 - 24 = output data"

Reproduction of CV in Memory -----2

5.

- Transpose under PLAY mode, with KCV ADD "on"

CSQ-100

TIME

A/D and D/A CONVERSION - details-

When MSB is first set on, the signal "1" is output to DB6. When D/A converted, the analog voltage (VDA) here must be 3.333V which, after shifted down by 41mV, secomes 3.392V (VDC). This time VDC goes into noninverting input of the comparator and is compared with CV IN. In the case shown in figure left, this

CV is 5V, so CV IN> VDC bringing the comparator's output to L (0), to have DB6 remainded as has been set to "1".

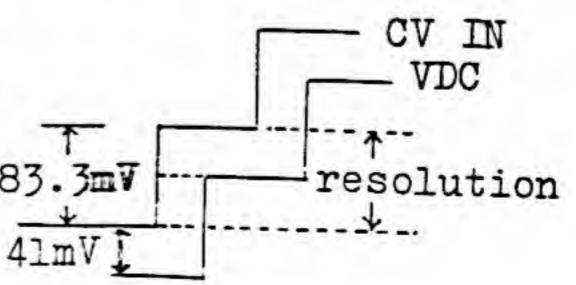

VDC = VDA - 4lmV(precisely, 41.7mV, and voltage differences between notes are 83.3mV or 84mV in turn)

Although 37 IN is in fact an analog voltage, steps up or down like a stircase wave as the note changes. Therefore, if VDC is shifted down by an amount equal to about one-half of the voltage difference per key (step rate. or resolution), a voltage fluctuation within CV IN the resolution value of the - VDC comparator does not bring --\*--83.3m▼ effect on the digital data, ----\*--as shown in the figure. 41mVI

# MAY 31,1979

Next, DB5 is set to "1". This time the digital data is the sum of DB6 and DB5, and the comparison becomes CT IN < VDC, to output H and to "reset" signal of TO and to have DB5 return to "O".

This kind of comparison is repeated 7 times down to DBO (LSB). The sum of the digital data of the bits remained "unreset", then, is made to be the data of this CV IN, with which the CV IN is stored in the

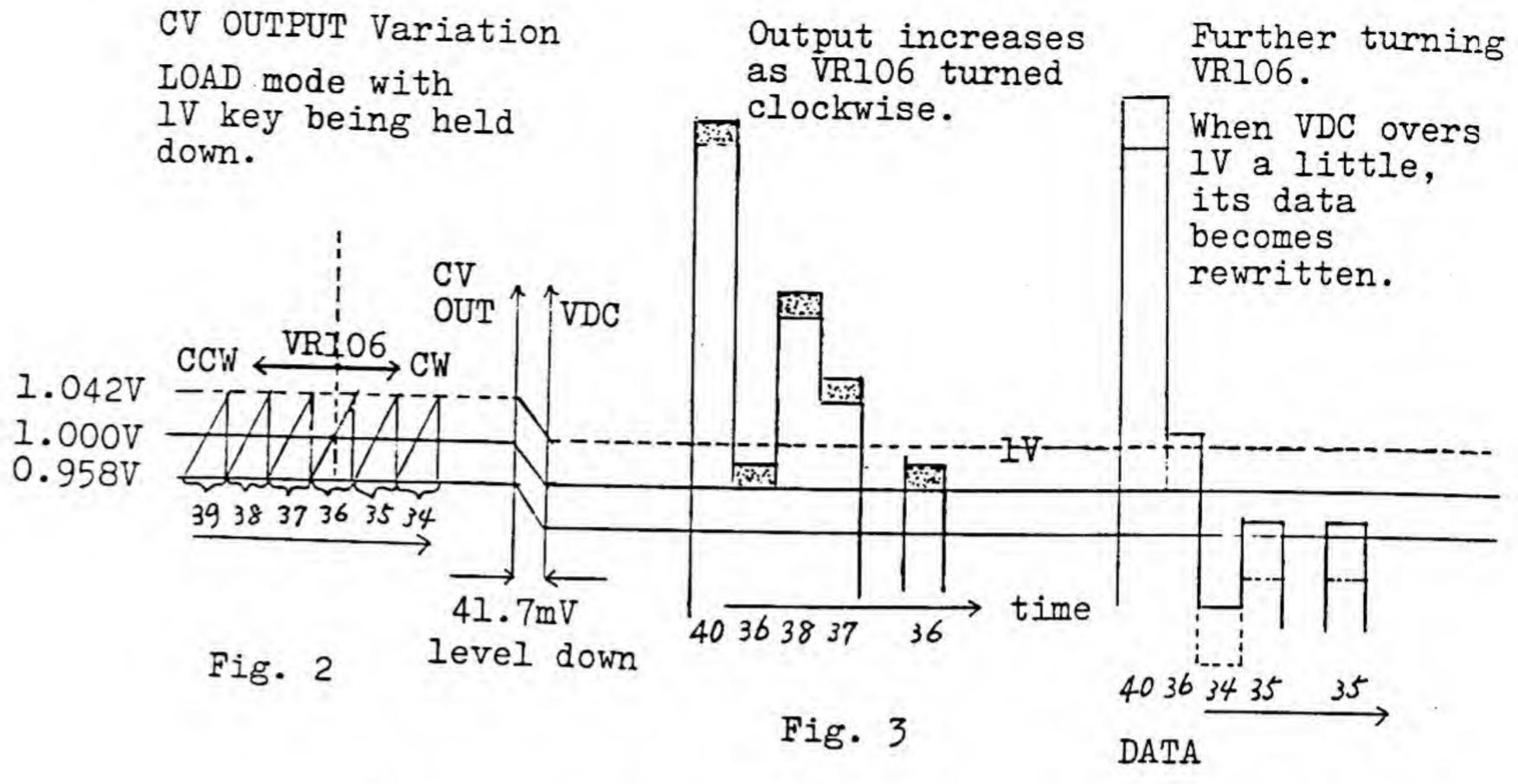

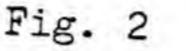

RELATIONSHIP BETWEEN CV ADJ (VR106) and CV DATA

In LOAD mode and with the converter that is correctly adjusted, suppose that we turn VR106 (CV ADJ) slowly clockwise while holding 1V key depressed on the keyboard. Then you can observe VDA (i.e. CV OUT) increases gradually, and likewise VDC (VDA - 41.7mV) ascends along the dotted area as shown in Fig. 3. That is to say, although the digital data is unchanged, the voltage for that data is increased. But, still kept on turning VR106 to have VDC overcome 1V line for the digital data 36 as shown in Fig. 4, it causes the output of the comparator to be turned to "H" and the digital data re-written to 35. Fig. 5 shows that state as being adjusted by turning VR106 clockwise to have CV OUT again to 1.000V.

Still turning VR106 further will repeat the same as above and to rewrite to 34. But, when turned counterclockwise, the data will be rewritten to a larger number each time.

down.

When watching this on a digital voltmeter connected for observation, the display will be as illustrated in Fig. 2. Now, suppose that we have turned VR106 a little too far to have the digital data 35 for CV IN of 1V (as in Fig. 5). It is all right and causes no problem as long as we have KCV ADD turned off, because under these circumstance, any shortage or excess of voltage could be compensated for by biasing thru this CV ADJ. potenticmeter. But once we have turned KCV ADD on, the whole matter would become different, to be explained on next page.

. . .

# CSQ-100

Fig. 4

WHEN DIGITAL DATA IS INCORRECT, ERROR WILL BE PRODUCED on CV OUT. with KCV ADD "ON"

Taking for instance the case of each having CV IN 1V converted into digital 35 ( B and C, table below) in place of 36, we will explain as follows:

Note: The topmost numbers in the table refer to those on page 6.

|   |                  | 2    | 3                 |      | 4. 5'                 | 6            | 7         |

|---|------------------|------|-------------------|------|-----------------------|--------------|-----------|

|   | MODE             | CVD1 | substrac-<br>tion | CVD2 | addition              | D/A<br>INPUT | CV<br>OUT |

| A | LOAD<br>(normal) | 36   | 24                | 12   | 24                    | 36           | 1V        |

| в | KCV ADD<br>"off" | 35   | 24                | 11   | 24                    | . 35         | ענ        |

| C | KCV ADD<br>"on"  | 35   | 24                | 11   | *(CVD-24)<br>47-24=23 | 34           | 0.9167V   |

Case B is when VR106 is adjusted to reprodece CV OUT of 1V even if in earlier stage the digital data lacks 1. In this case, since the numbers in preceding subtraction. and subsequent addition are both the same (24), the analog amount at the output receives no effect to differ after A-D-A conversions.

In C, however, despite the fact that the KCV (being pressed ) is converted to digital data number short of 1, it is added to RAM-stored-data after subtracting 24. This means that there is a double shortage, bringing after all the shortage by 2 before D/A conversion prior to CV OUT. Through this D/A once again, 1 out of these 2 can be compensated for by VR106, but there is still remained of 1, which brings lack in pitch of a semitone ( "1" in digital data) on tone reproduction. Thus, a maladjustment of VR106 produces a deviation on reproduction when played with KCV ADD "on". Or, it can be said conversely that, through finding such deviation on analog voltage, it is possible to check digital data errors.

WIDTH ADJUSTMENT with VR105

This potentiometer VR105 is for use to correct the gain of IC113 so as to have D/A in proper relation of 1V/oct, that is, when the data changes by 1, CV OUT changes by 83.3mV. When VR105 is required for readjustment, it may also be necessary to readjust VR106, since turning either VR results in interaction between adjustments, therefore, both VRs need to be adjusted in turn.

Also care must be exercised to avoid an excessive turn of the VRs which will bring difficulty in performing this adjustment.

-

This potentiometer is for the gain If this step deviates adjustment of the D/A amp, and it from normal, deviation is carried through the is in particular for DB6. This upper steps. DB6 is for the data weighing the most significant bit, so its 3.333V adjustment is the most critical one 3.250V and warrants the careful atten-CV OUT tion. Sources of fluctuation and 62 63 64 65 66 deviation such as those coming from the preceding stage of IC103, IC104, on impedance or on output voltage, and resistance variation in resistor, etc. are to be compensated for by this VR104. Since the digital data that makes DB6 active is in number over 64 or 3.333V in CV, fluctuation brought through DB6 data will effect all CV of higher voltages as shown in the figure. In practice, it will be best to adjust VR104 as follows: Set the LOAD mode and complete both CV ADJ and WIDTH ADJ, then, holding down the key for 4V. Set VR104 so that CV OUT equals 4.000V.

# MAY 31,1979

D/A ADJUSTMENT with VR104

-

####

Improvement on RESET SENSE

Increasing ClO4 capacitance from 1 mfd to 10 mfd may make RESET pulse more stable.

Note: 82k is unnecessary when existing Cl06 is 0.47/50.

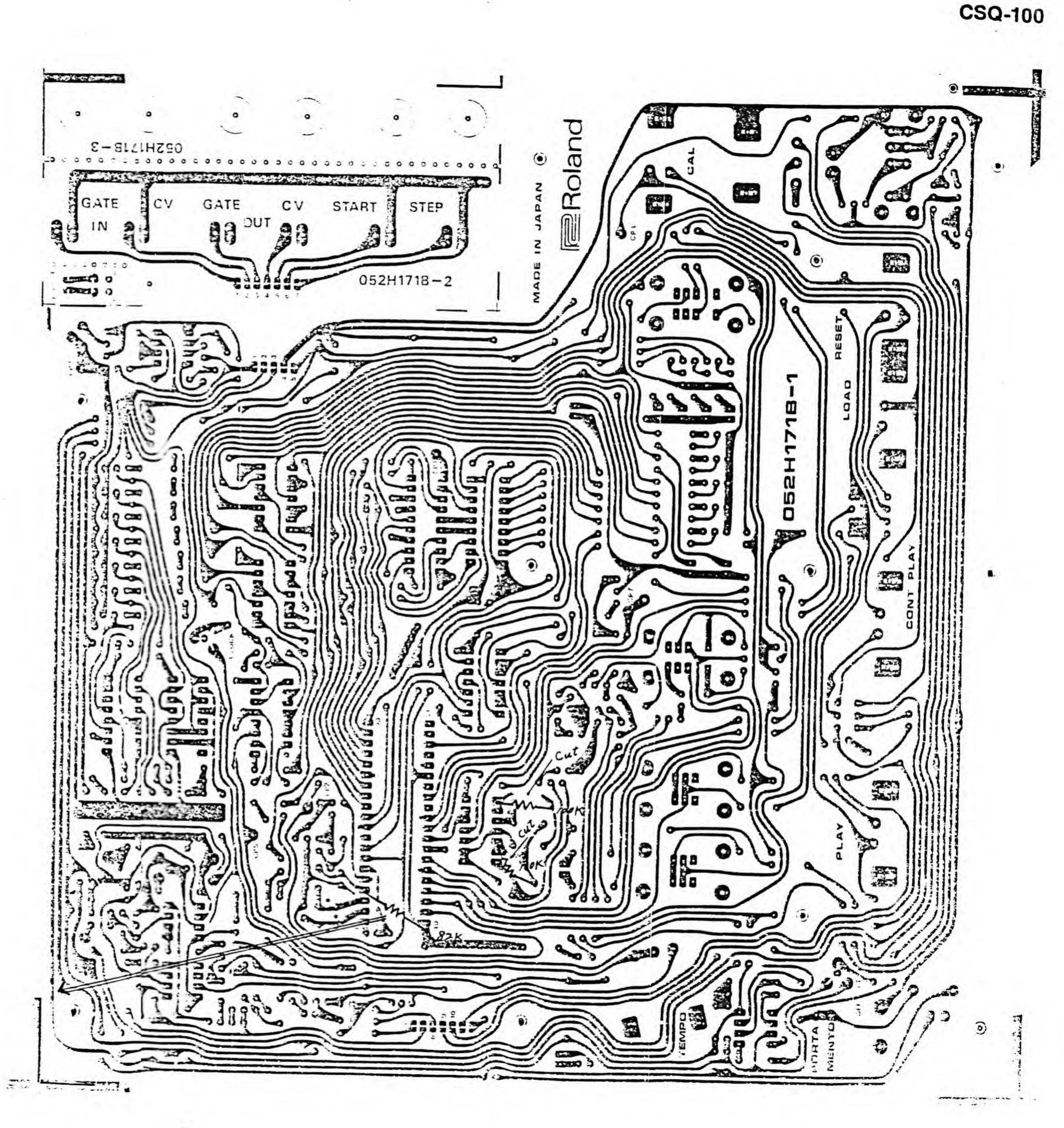

OPH31B(149H031B) (052H171B-1) OPH70B(149H070B) (052H171B-2)

9.0

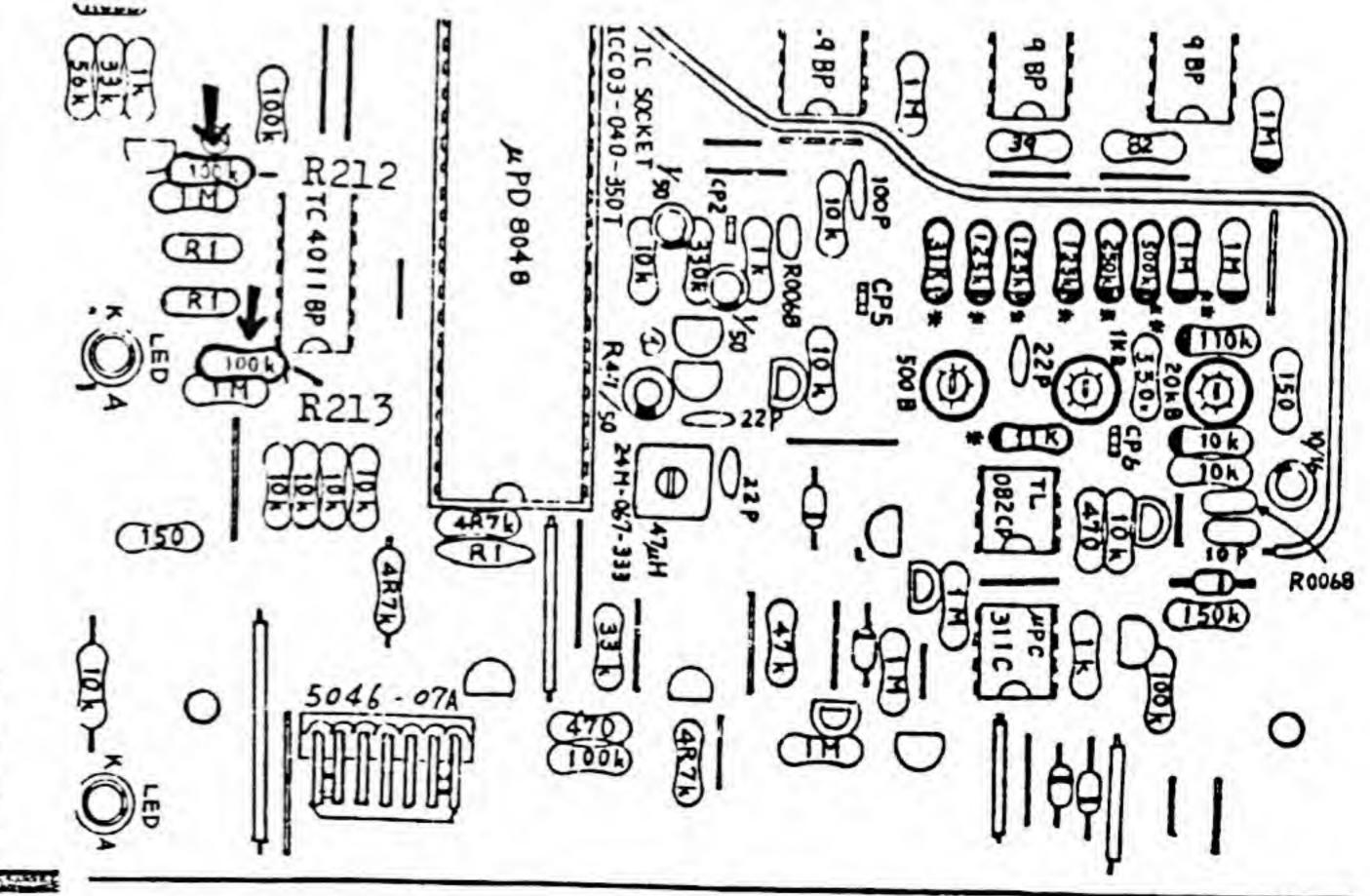

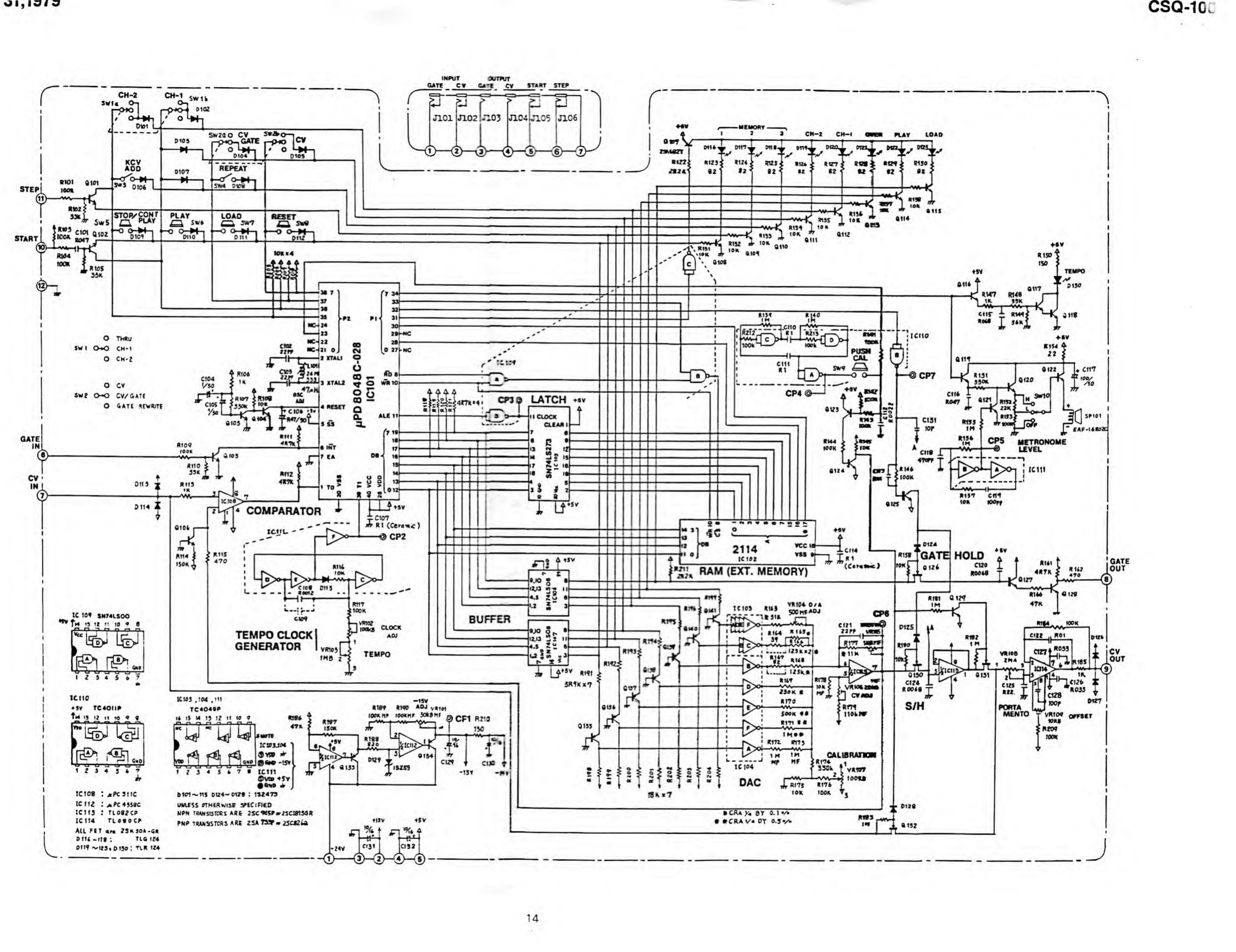

Difference between OPH31's:

OPH31D - R212, R213 (100K) are mounted on the component side with the pattern provided

OPH31B - Both 100Ks are attached on the foil side with pertinent pattern cut

MAY 31,1979

0

#### WAI 31,13/3

Ч

2

16 17 15 H 0 200 0 0 0 T315m (008-( PSH41 F301 Hant O and the second 4 H 303 -13 20 0. 12 m H 10 -400100 3SI 1.2 10 0 CS. 9 **A**--0 40) 0 Õ θ 5 Q 0 The second second 301 139 (008 0 0 0-0 MGP ISI m 1053 4 5 9 5

÷.

#### ADJUSTMENTS

The adjustment is composed of 2 parts: Section I and Section II. It is recommended that the adjustment which is necessitated after the replacement of failing component or others are, as a rule, to be conducted as described in Section I.

Definitions In this adjustment, the following terms have following meanings,

DVM ------ Digital Voltmeter <u>LOAD, PLAY, etc. ----- Key on the CSQ-100 control panel</u> 2V key, 3V key, etc. ---- A key on the synthsizer being used, which

provides that KCV

TEMPO, CAL, FAST, etc. --- Control, switch, jack, legend on the CSQ-(capital letters) 100 SCOPE ----- Oscilloscope CP1, CP2, etc. ----- Check point on the PCB.

Note: Before attempting adjustment, warm-up period for no less than 10 minutes should be given.

CAUTION: Care must be taken not to turn the adjusting potentiometers excessively.

#### Adjustment is usually necessary only after replacing parts.

#### CALIBRATION PROCEDURES

| After<br>replacement of                                    | Connect,-                                                            | Adjust<br>or Check | for (remark)                                                                                                                   |

|------------------------------------------------------------|----------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------|

| IC101 (µPD8048<br>L101 (47uH)                              | 3) Frequency<br>counter,<br>CP3                                      | LIOI               | 365kHz ± 10kHz<br>(8048 Clock frequency)                                                                                       |

| IC110<br>(TC4011P)                                         | Scope,<br>CP4                                                        |                    | (waveform check)                                                                                                               |

| (TC4049P, 1_                                               | . Frequency<br>counter,<br>CP2                                       |                    | (Tempo clock frequency)<br>$4.7 \text{kHz} \pm 5\%$ with TEMPO at FAST                                                         |

| If this rang<br>the range of                               | requency is C<br>e deviates, r<br>4.7kHz <u>+</u> 5%.<br>capacitance | eadjust VR10       | with TEMPO set at SLOW.<br>02 with TEMPO at FAST within                                                                        |

| IC114<br>(TLOSOCP)                                         | No connec-<br>tion at CV<br>IN jack<br>CV OUT,                       | VR109<br>Offset    | (Depress <u>RESET</u> )                                                                                                        |

| 4                                                          | · DVM                                                                |                    | 0 ± 0.5mV                                                                                                                      |

| IC112 5<br>(µPD4558) 5<br>D129<br>(1SZ59)                  | DVM,<br>CP1                                                          | VR101<br>-15V Adj. | -15V <u>+</u> 2mV                                                                                                              |

| pronou                                                     |                                                                      | n the DA con       | supplies will have the most<br>werter, check CV OUT for error                                                                  |

| IC103, IC104<br>(TC4049)<br>IC113 (TL082-P)<br>CV GATE out |                                                                      | VR106<br>CV Adj.   | (DA Adj.)<br>CAUTION: Adjustment of the DA<br>converter is very subtle.<br>Always rotate ADJ. pots by                          |

| 6                                                          | . DVM,<br>CV OUT                                                     |                    | slow degrees, excessive turn<br>will bring great difficulty<br>into the subsequent adjustment<br>attempts, requring a waste of |

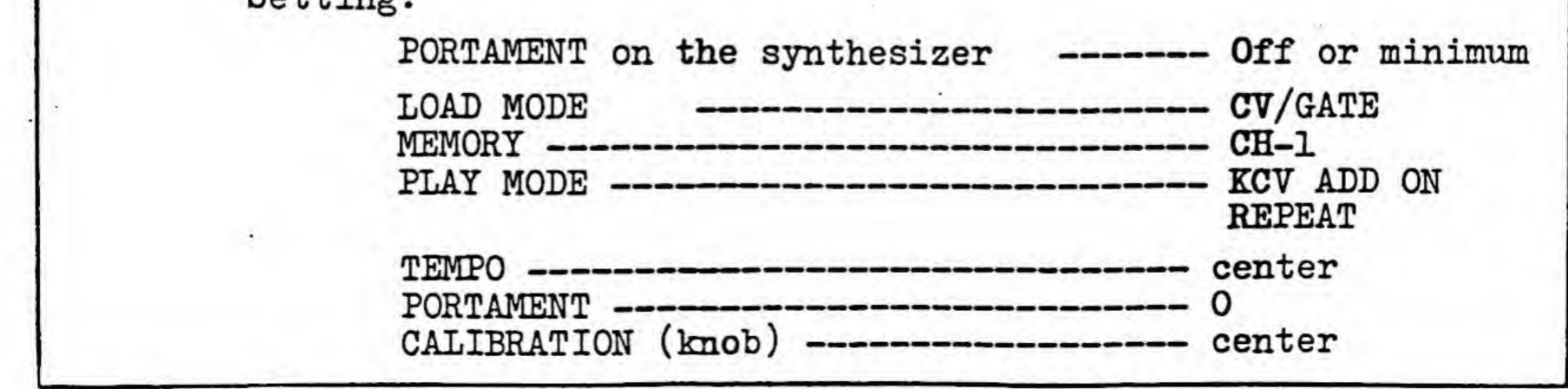

Setting:

(Continuation of Step 6 from previous page)

6-1. Press RESET and LOAD.

6-2. Depress the 2V key, DVM must read 2.000V <u>+</u> 3mV. When DVM reads within 3mV, adjust CALIBRATION pot for 2V CV OUT with <u>PUSH CAL</u> depressed. Then proceed to 6-3, 6-4. If reading is outside <u>+</u> 3mV range, set CALIBRATION pot at center, and adjust VR106 (CV Adj.) for 2.000V <u>+</u> 3mV reading.

**CSQ-100**

- 6-3. Verification of KCV ADD function While depressing the 2V key, push <u>PLAY</u>. DVM must read the same.

- A. If reading changes, it means that VR106 (CV Adj.) has been set at incorrect point. Proceed to Section II

- B. When the reading is steady, make sure that DVM readings are within the ranges in the table shown below with respective key depressed.(<u>RESET-LOAD-2V key-PLAY-2V key-3V key-4V key</u>)

| key being depres | sed DVM reading (CV OUT) |  |

|------------------|--------------------------|--|

| 2V               | $2.000V \pm 2mV$         |  |

| 3V               | $3.000 \pm 2mV$          |  |

| 4V               | $4.000V \pm 2mV$         |  |

If any of the readings exists outside the limit, make asjustment under SECTION II, 1-6.

6-4. Press <u>RESET</u> and <u>LOAD</u>. While depressing 4V key, press PLAY. DVM must read 6.0COV <u>+</u> 3mV. If not, proceed to SECTION II, 1-7.

# MAY 31,1979

#### SECTION II

#### 1. ADJUSTING DA CONVERTER

Some procedures are the same as described under Section I. In the following steps, adjustment should be made with specified key being depressed.

- 1-1. Connection and Settings: Follow the instruction "6" in Section I. 1-2. Press <u>RESET</u> and <u>LOAD</u>.

- 1-3. While depressing 2V key, adjust VR106 (CV Adj.) for 2.000V reading. then, press <u>PLAY</u>.

A. If the reading stays unchanged, proceed to step 1-6. B. If it changes, proceed to step 1-4. (note the reading)

1-4. Press RESET, LOAD and 2V key.

While depressing the 2V key, adjust VR106 for a following "2"V according to the deviation noted at step 1-3,B. As discussed earlier (RELATIONSHIP, CV ADJ and DATA), DVM reading will repeat the cycle of  $2V \pm 4 \text{lmV}$  as VR106 being turned. Ordinal number in the right colum of the table below shows number of repetition.

| DVM reading<br>at step<br>1-3,B<br>(approx) | Turn VR106<br>in this direction | Stop turning<br>when DVM reads<br>2.000V of |

|---------------------------------------------|---------------------------------|---------------------------------------------|

| 2.0831                                      | clockwise                       | lst                                         |

| 2.167V                                      | clockwise                       | 2nd                                         |

| 2.250V                                      | clockwise                       | 3rd                                         |

| 1.917V                                      | counterclockwise                | lst .                                       |

| 1.833V                                      | counterclockwise                | 2nd                                         |

| 1.750V                                      | counterclockwise                | 3rd                                         |

- 1-5. Press <u>RESET</u>, <u>LOAD</u>, 2V key and <u>PLAY</u>. ( 2V key held down) DVM must keep the same reading.

- 1-6. Press RESET and LOAD.

|      | key to be<br>pressed | adjust        | for<br>reading |                         |

|------|----------------------|---------------|----------------|-------------------------|

| 1-61 | 3V                   | VR105(WIDTH)  | 3.000V         | repeat until DVM reads  |

| 1-62 | 2V                   | VR106(CV Adj) | 2.0007         | 3.000V and 2.000V       |

| 1-63 | 4V                   | VR104(DA Adj) | 4.000V         | repeat until respective |

| 1-64 | 2V                   | VR106         | 2.000V         | voltages are displayed  |

| 1-65 | 30                   | VR105         | 3.000V         | on DVM                  |

# **CSQ-100**

- 1-7. Press RESET, LOAD, 4V key (holding down) and PLAY. DVM should read 6.000V + 2mV.

- If DVM proves that deviation is outside this range, it may be 1-8. cured by turning VR105, but this adjustment will affect steps 1-64,1-65.

Turn VR105 within the limit of  $2.000V \pm 2mV$  and  $3.000V \pm 2mV$ .

CHECKING CV OUT 2.

> With DVM connected to CV OUT and LOAD pressed. Check the DVM readings for 1V/oct through entire keyboard.

> > View from panel side

Note: When difficulties arise in relation to WIDTH and CV adjustment, VR104, VR105 and/or VR106 might have been set too far from their proper position. Reset them to the approximate positions illustrated in figure right. Adjust again from appropriate step.

VR106 CV ADJ

VR105 WIDTH

VR104 DA ADJ

56253.55

# PARTS LIST

rear

front

# MAY 31,1979

| 072H049  | Fanel H49                        |

|----------|----------------------------------|

| 06611021 | Side block H21<br>set of L and R |

| 061H080  | Chassis H80                      |

| 068-020  | Bushing no.20 panel              |

| 111-021  | Rubber Foot G-5 rear             |

| 111-023  | Rubber Foot G-7 from             |

- 016-008 Button no.8 gray power switch

- 016-057 Knob no.57 TEMPO

- 016-033 Knob no.33 PORTAMENTO

- 063-012 Strip no.12 knob no.33

POWER TRANSFORMERS

100V/117V 022H024C

#### PCBs

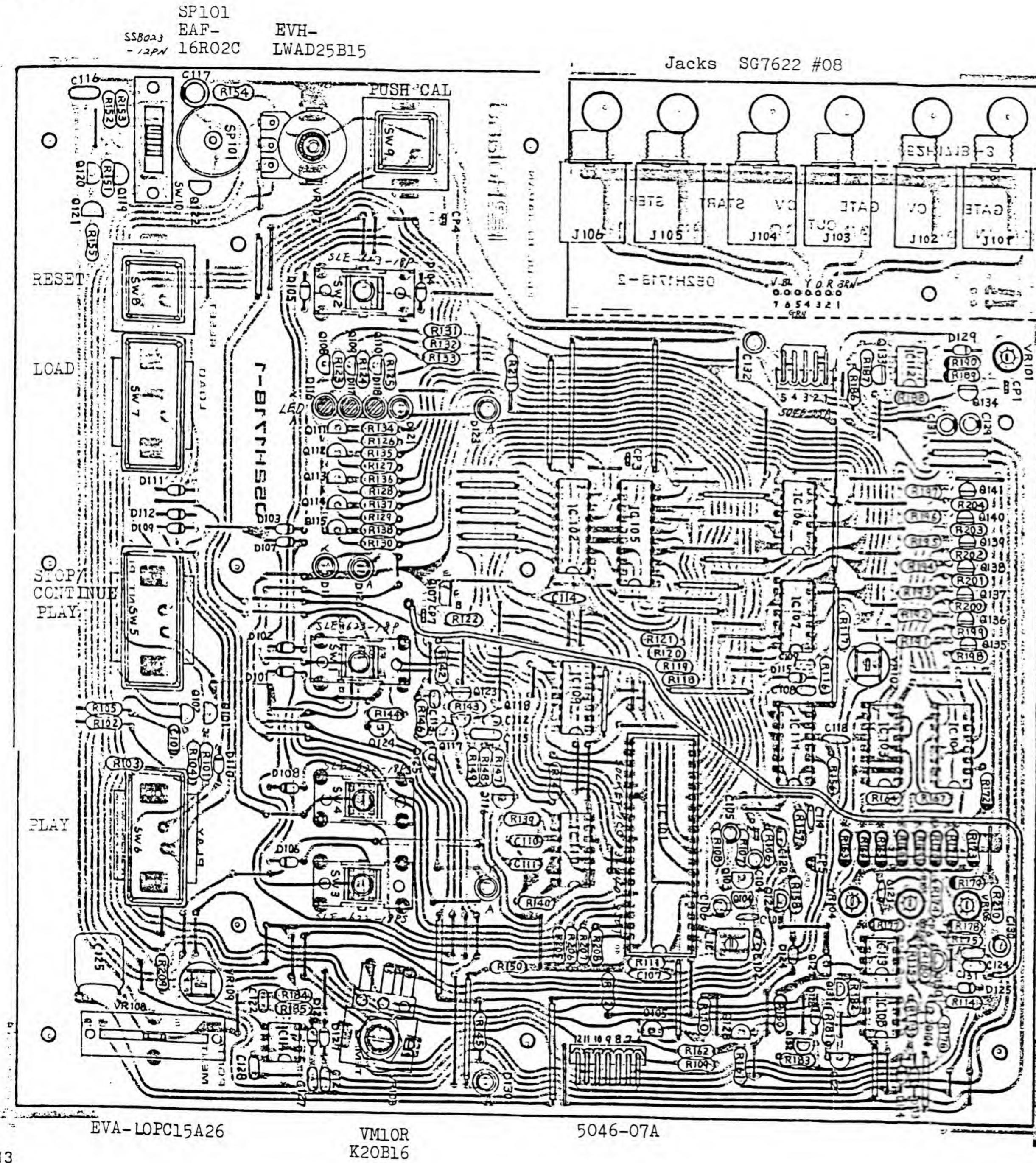

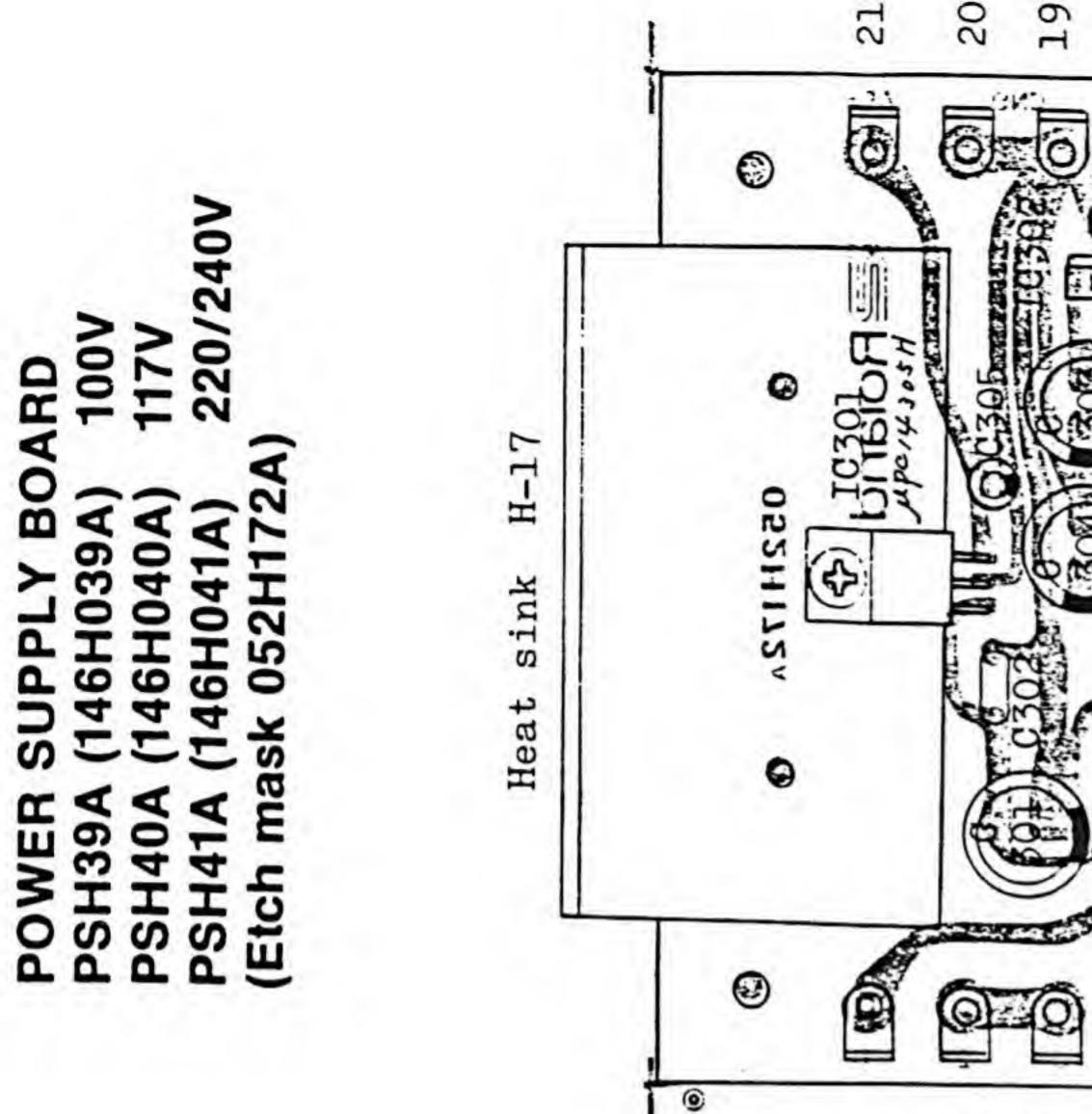

149H031D OPH31D (052H171D-1) 149H070D OPH70D (052H171D-2) 146H039A PSH39A (052H172A) 100V 146H040A PSH40A (052H172A) 117V 146H041A PSH41A (052H172A) 220/240V 048H017 Heat sink H17 PSH-042-039 Check point 59BS8806

#### POTENTIOMETERS

029-577 EVALOPC15A26 2MA slide PORTAMENTO 030-951 EVHLWAD25B15 10CKB CALIBRATION 028-766 VM10RK20B16 1MB TEMPO

| 02200240 | 1000/11/0                      |

|----------|--------------------------------|

| 022H024D | 220V/240V                      |

| 022-136  | Coil 24M-067-033 47µH          |

| 009-012  | Jack SG7622 no.8 mono          |

| 068-018  | Bushing no.18 red jack         |

| 068-005  | Bushing no.5 jack              |

| 121-005  | Washer no.5 jack               |

| FUSES    |                                |

| 008-040  | MGP 0.500 CSA prim 117V        |

| 008-061  | SEMKO T315mA prim.<br>220/240V |

| 008-056  | SEMKO T100mA sec.              |

| 008-066  | SEMKO TIA .sec.                |

| 012-003  | Fuse clip TF758                |

|          |                                |

SWITCHES

SDG5P 001-1 power 100V 001-215

030-465 SR19R 10KB 030-471 SR19R 100KB 030-644 RJ-6P 500B 030-645 RJ-6P IKB 030-646 RJ-6P 50KB

# trimmer trimmer trimmer trimmer trimmer

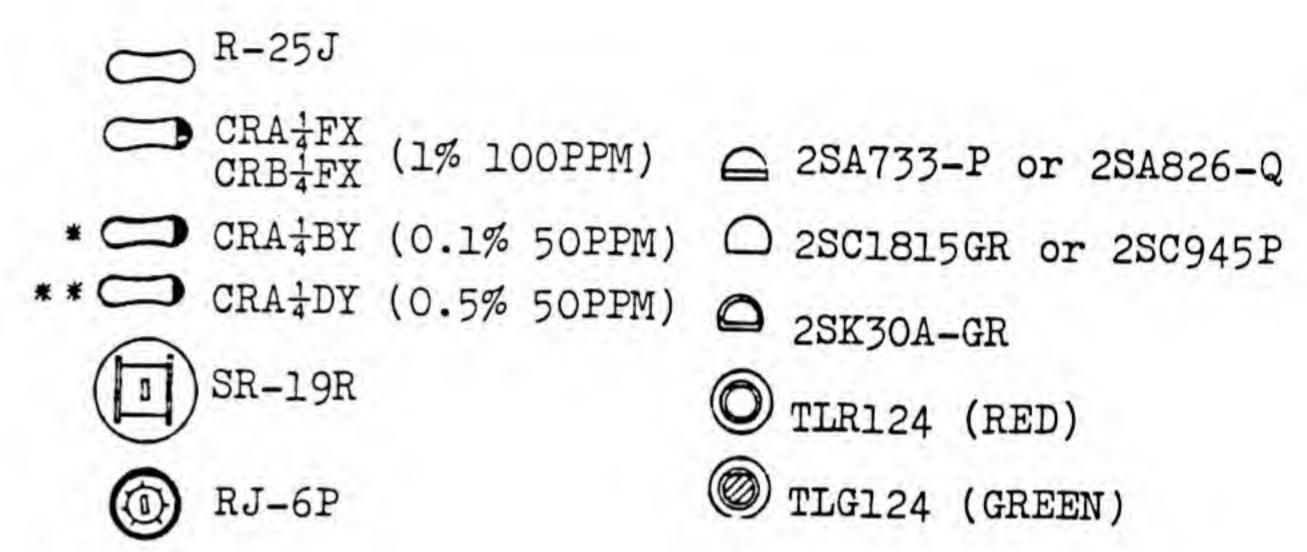

#### RESISTORS

| 044-927 | CRA4BY                             | llK  | 0.1% | 50PPM |  |

|---------|------------------------------------|------|------|-------|--|

| 044-932 | CRA4BY                             | 31K  | 0.1% | 5CPPM |  |

| 044-929 | CRA4BY                             | 125K | 0.1% | 50PPM |  |

| 044-930 | CRA +BY                            | 250K | 0.1% | 50PPM |  |

| 044-972 | CRA+DY                             | 500K | 0.5% | 50PPM |  |

| 044-973 | CRA <sup>1</sup> / <sub>4</sub> DY | lM   | 0.5% | 50PPM |  |

| 044-838 | CRB4FX                             | lok  | 1%   |       |  |

| 044-846 | CRB <sup>1</sup> FX                | 100K | 1%   |       |  |

| 044-860 | CRA <sup>1</sup> / <sub>4</sub> FX | lM   | 1%   |       |  |

|         |                                    |      |      |       |  |

CAPACITOR

SDG5P 001-2 power 117V 001-216 037-035 Disk seramic 0.1 mfd +80 % SDG5P 502 power 220/240V 001-217 12V -20 001-068 SLE-622-18PS lever 001-201 SLE-623-18PS lever 001-183 SSB-023-12PN slide 001-276 SCK41167 key 001-275 SCK41168 key 21

#### SEMICONDUCTORS

#### LSIS

179-028 µPD8048C-028 8-bit microcomputer or µPD8048C-077 can be interchanged

020-202 µPD2114LC RAM

#### ICs

| 020-203 | SN74LSOON  |

|---------|------------|

| 020-204 | SN74LS273N |

| 020-120 | SN74LSO8N  |

| 020-040 | TC4011BP   |

| 020-075 | TC4049BP   |

| 020-199 | uPC311C    |

| 020-100 | TLO82CP    |

# WAFER TERMINALS, TERMINAL, WIRING ASSEMBLIES

| 010-195 | Terminal 5046-05A                 |

|---------|-----------------------------------|

| 010-196 | Ternimal 5046-07A                 |

| 042-032 | Terminal TT 501-D01<br>line cable |

| 053H046 | Wiring Assy A                     |

| 053H047 | Wiring Assy B                     |

| 053H048 | Wiring Assy C                     |

#### MISCELLANEOUS

| 065H050 | Dust | cover H50 |      |        |  |

|---------|------|-----------|------|--------|--|

| 120-001 | Long | nut       | no.l | 3xlOmm |  |

| 120-003 | Long | nut       | no.3 | 3x18mm |  |

# CSQ-100

22

| 020-200 | TLOSOCP                 |  |

|---------|-------------------------|--|

| 020-097 | µPC4558C                |  |

| 020-205 | µPC14305 +5V regulator  |  |

| 020-206 | µPC78L15 +15V regulator |  |

|         |                         |  |

# (stand-off or spacer)

- 012-043 IC Socket ICC030-040-350T (uPD8048)

- 064H076 Holder H76

### TRANSISTORS

- 017-016 2SK30A-GR FET

- 017-106 2SC1815-GR

- 017-024 2SA733-P

- 017-034 2SA682-Y

#### DIODES

- 018-014 152473

- 018-097 1SZ59 zener temperatue compensated 018-089 1B4B41 rectifier stack 018-1B4B1 rectifier stack

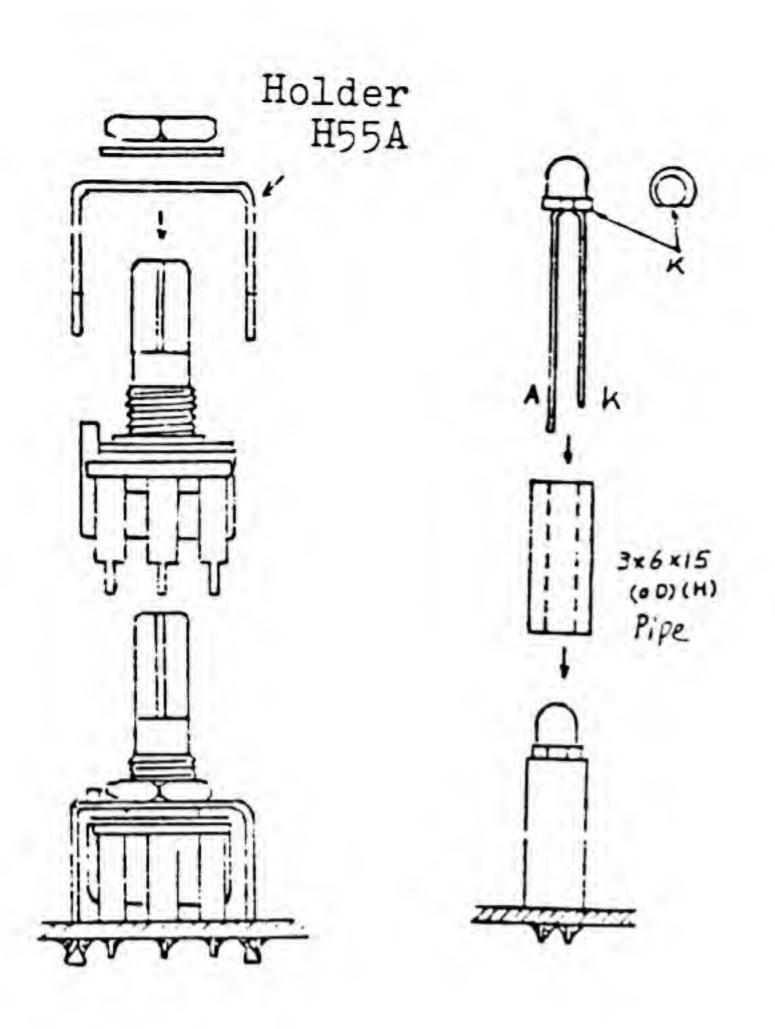

# 064H055A Holder H55A

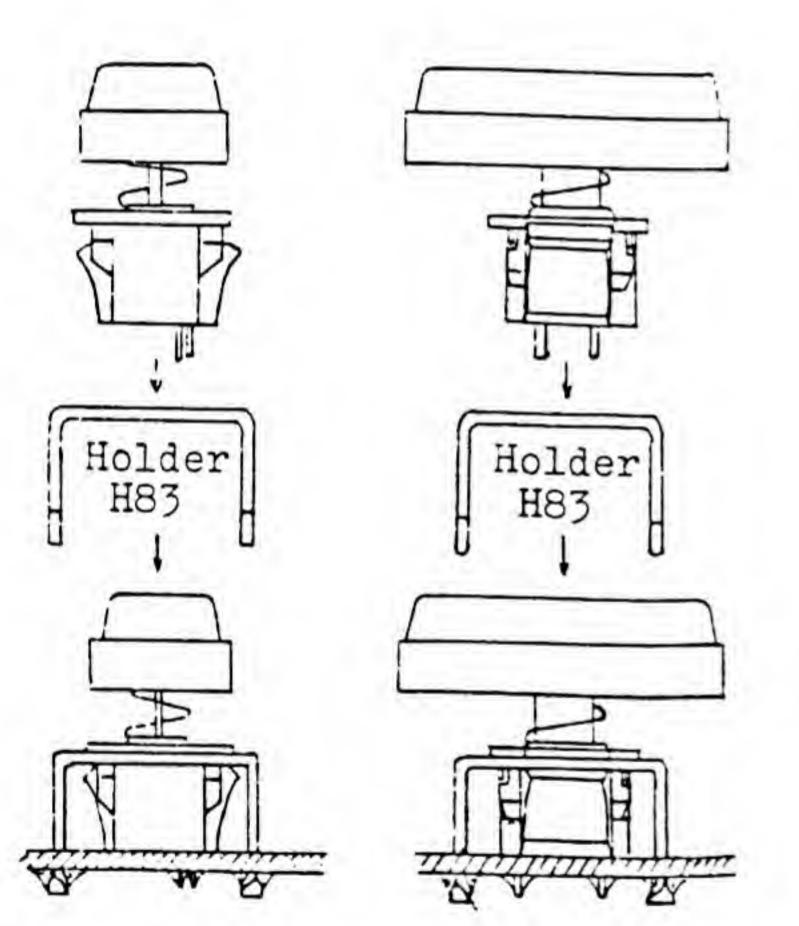

064H083 Holder H83

Commonly available parts: Resistors of 1/4W, 5%, Mylars, Electrolytics are omitted.

LEDs

#### 019-028 TLR-124 red TLG-124 green 019-029 019-009 LRO601R red