# **Application Note AN-1129**

## IRS20954S and IRS20955S Comparison

By, Connie Huang, Jun Honda, Xiao-chang Cheng

## Table of Contents

| Introduction                          | <b>Page</b><br>1 |

|---------------------------------------|------------------|

| Block Diagram                         | 2                |

| Electrical Characteristic Differences | 3                |

| Logic Status Differences              | 5                |

| Summary                               | 5                |

## Introduction

The IRS20955S is a high voltage, high speed MOSFET driver with a floating PWM input designed for Class D audio amplifier applications. The IRS20955S is an improved version of the IRS20954S. This application note describes the differences between the IRS20954S and IRS20955S.

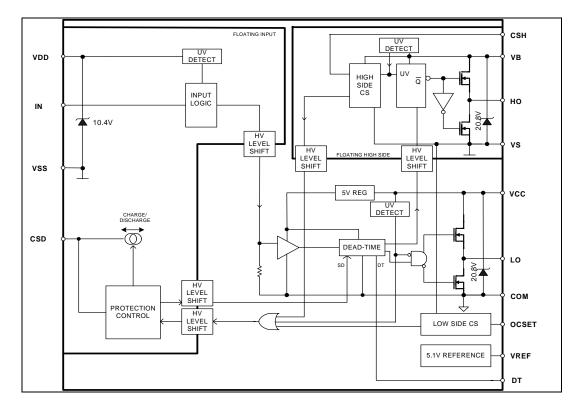

## **Block Diagram**

The IRS20954S and the IRS20955S share the same functional structure. In normal operating condition, there are no functional changes between corresponding part numbers.

## APPLICATION NOTE

## **Electrical Characteristic Differences**

All measurement conditions are the same for both the IRS20954S and IRS20955S.

#### **Absolute Maximum Ratings**

There are no changes in the Dynamic Electrical Characteristics.

#### **Recommended Operating Conditions**

There are no changes in the Recommended Operating Conditions.

#### **Dynamic Electrical Characteristics**

There are no changes in the Dynamic Electrical Characteristics.

#### **Static Electrical Characteristics**

The zener clamp voltages and high level output voltage are different for the IRS20954S and IRS20955S.

|                     |                                                    | IRS20954S |      | IRS20955S |      |      |      |       |

|---------------------|----------------------------------------------------|-----------|------|-----------|------|------|------|-------|

| Symbol              | Definition                                         | Min       | Тур  | Max       | Min  | Тур  | Max  | Units |

| V <sub>CLAMPL</sub> | Low-side zener<br>diode clamp<br>voltage           | 19.8      | 20.8 | 21.8      | 19.6 | 20.4 | 21.6 |       |

| V <sub>CLAMPH</sub> | High-side zener<br>diode clamp<br>voltage          | 19.8      | 20.8 | 21.8      | 19.6 | 20.4 | 21.6 | V     |

| V <sub>CLAMPM</sub> | Floating Input<br>zener diode clamp<br>voltage     | 9.9       | 10.4 | 10.9      | 9.8  | 10.2 | 10.8 | v     |

| V <sub>OH</sub>     | High level output<br>voltage, VCC –<br>LO, VB – HO | -         | -    | 1.2       | -    | -    | 1.4  |       |

|                     |                                                                                       | IRS20954S           |                     | IRS20955S           |                     |                     |                     |       |

|---------------------|---------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-------|

| Symbol              | Definition                                                                            | Min                 | Тур                 | Max                 | Min                 | Тур                 | Max                 | Units |

| V <sub>REF</sub>    | Reference output voltage                                                              | 4.6                 | 5.1                 | 5.6                 | 4.8                 | 5.1                 | 5.4                 |       |

| V <sub>th,OCL</sub> | Low-side OC<br>threshold in Vs                                                        | 1                   | 1.2                 | 1.4                 | 1.1                 | 1.2                 | 1.3                 | V     |

| $V_{\text{th,OCH}}$ | High-side OC<br>threshold in V <sub>CSH</sub>                                         | 1.0+ V <sub>s</sub> | 1.2+ V <sub>s</sub> | 1.4+ V <sub>s</sub> | 1.1+ V <sub>s</sub> | 1.2+ V <sub>s</sub> | 1.3+ V <sub>s</sub> |       |

| I <sub>CSD+</sub>   | CSD pin discharge<br>current                                                          | 50                  | 100                 | 150                 | 70                  | 100                 | 130                 | uΔ    |

| I <sub>CSD-</sub>   | CSD pin charge<br>current                                                             | 50                  | 100                 | 150                 | 70                  | 100                 | 130                 | μA    |

| t <sub>SD</sub>     | Shutdown<br>propagation delay<br>from $V_{CSD} > V_{SS} +$<br>$Vth_{OCH}$ to shutdown | -                   | 200                 | 500                 | -                   | -                   | 250                 |       |

| t <sub>осн</sub>    | Propagation delay time from $V_{CSH} > V_{th_{OCH}}$ to shutdown                      | -                   | -                   | 600                 | -                   | -                   | 500                 | ns    |

| t <sub>OCL</sub>    | Propagation delay<br>time from Vs><br>Vth <sub>OCL</sub> to shutdown                  | -                   | -                   | 600                 | -                   | -                   | 500                 |       |

#### Static Electrical Characteristics (Cont'd)

The minimum and maximum limits for V<sub>REF</sub>, V<sub>th,OCL</sub> and V<sub>th,OCH</sub> are tightened in the IRS20955S for improved over-current threshold accuracy.

The minimum and maximum limits for  $I_{CSD+}$  and  $I_{CSD-}$  are tightened in the IRS20955S for improved protection control timer accuracy.

The minimum and maximum limits for  $t_{SD}$ ,  $t_{OCH}$  and  $t_{OCL}$  are shortened in the IRS20955S for faster OCP reaction time.

## **Logic Status Differences**

#### Initial Output Logic Status

In the IRS20954S, the order in which power is supplied to the IC can affect the output logic states of LO and HO. When power is supplied to  $V_{DD}$  before power is supplied to  $V_{CC}$ , the logic states of LO and HO are opposite but independent from the input until the first logic transition occurs at the input.

In the IRS20955S, the logic states of HO and LO correspond to the input of the IC after shutdown release to ensure switching action is not affected by the power up sequence.

#### HO Logic at Initial Startup

In the IRS20954S, the initial state of HO could be low or high when  $V_{BS}$  is powered up before  $V_{CC}$ , i.e. HO logic is unknown during startup if  $V_{BS}$  reaches the UV threshold before  $V_{CC}$  does.

In the 20955S, HO stays low in the same scenario.

| Issue Addressed                | Condition                                             | IRS20954S                                                                                                                                                    | IRS20955S                                                                                                          |

|--------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Initial Output Logic<br>Status | Power is supplied to V <sub>DD</sub>                  | - HO = LO                                                                                                                                                    | - HO = LO                                                                                                          |

|                                | before power is supplied to V <sub>CC</sub> .         | <ul> <li>The output logic<br/>states of HO and<br/>LO are unknown<br/>until the first logic<br/>transition at the<br/>input of the IC<br/>occurs.</li> </ul> | <ul> <li>The output logic<br/>states of HO and<br/>LO corresponds<br/>to the logic input<br/>to the IC.</li> </ul> |

| HO Logic at Initial            | $V_{CC} < UV_{CC}$ and                                | The logic status of                                                                                                                                          | HO = low                                                                                                           |

| Startup                        | V <sub>BS</sub> > UV <sub>BS</sub><br>during start up | HO is unknown.                                                                                                                                               |                                                                                                                    |

| Table 1 Summary of L | ogic Status Difference | s between the IRS2095 | 4S and the IRS20955S |

|----------------------|------------------------|-----------------------|----------------------|

|                      | ogio otatus Dinerenee  |                       |                      |

### Summary

The IRS20955S is an improved version of the IRS20954S in terms of over-current protection accuracy. Applications using a self-oscillating PWM topology that includes the gate driver IC should use the IRS20955S.