# CHAPTER 1 Op Amp Basics

- Section 1-1: Introduction

- Section 1-2: Op Amp Topologies

- Section 1-3: Op Amp Structures

- Section 1-4: Op Amp Specifications

- Section 1-5: Precision Op Amps

- Section 1-6: High Speed Op Amps

This page intentionally left blank

# CHAPTER 1 Op Amp Basics James Bryant, Walt Jung, Walt Kester

Within Chapter 1, discussions are focused on the basic aspects of op amps. After a brief introductory section, this begins with the fundamental *topology* differences between the two broadest classes of op amps, those using *voltage feedback* and *current feedback*. These two amplifier types are distinguished more by the nature of their internal circuit topologies than anything else. The voltage feedback op amp topology is the classic structure, having been used since the earliest vacuum tube based op amps of the 1940s and 1950s, through the first IC versions of the 1960s, and includes most op amp models produced today. The more recent IC variation of the current feedback amplifier has come into popularity in the mid-to-late 1980s, when higher speed IC op amps were developed. Factors distinguishing these two op amp types are discussed at some length.

Details of op amp input and output *structures* are also covered in this chapter, with emphasis on how such factors potentially impact application performance. In some senses, it is logical to categorize op amp types into performance and/or application classes, a process that works to some degree, but not altogether.

In practice, once past those obvious application distinctions such as "high speed" versus "precision," or "single" versus "dual supply," neat categorization breaks down. This is simply the way the analog world works. There is much crossover between various classes, i.e., a high speed op amp can be either single or dual-supply, or it may even fit as a precision type. A low power op amp may be precision, but it need not necessarily be single-supply, and so on. Other distinction categories could include the input stage type, such as FET input (further divided into JFET or MOS, which, in turn, are further divided into NFET or PFET and PMOS and NMOS, respectively), or bipolar (further divided into NPN or PNP). Then, all of these categories could be further described in terms of the type of input (or output) stage used.

So, it should be obvious that categories of op amps are like an infinite set of analog gray scales; *they don't always fit neatly into pigeonholes, and we shouldn't expect them to.* Nevertheless, it is still very useful to appreciate many of the aspects of op amp design that go into the various structures, as these differences directly influence the optimum op amp choice for an application. Thus structure differences are application drivers, since we choose an op amp to suit the nature of the application—for example, single-supply.

In this chapter various op amp performance *specifications* are also discussed, along with those specification differences that occur between the broad distinctions of voltage or current feedback topologies, as well as the more detailed context of individual structures. Obviously, op amp specifications are also application drivers; in fact, they are the most important since they will determine system performance. We choose the best op amp to fit the application, based on the required bias current, bandwidth, distortion, and so forth. This page intentionally left blank

# SECTION 1-1 Introduction Walt Jung

As a precursor to more detailed sections following, this introductory chapter portion considers the most basic points of op amp operation. These initial discussions are oriented around the more fundamental levels of op amp applications. They include: *Ideal Op Amp Attributes, Standard Op Amp Feedback Hookups, The Non-Ideal Op Amp, Op Amp Common-Mode Dynamic Range(s),* the various *Functionality Differences of Single and Dual-Supply Operation,* and the *Device Selection* process.

Before op amp applications can be developed, some requirements are in order. These include an understanding of how the fundamental op amp operating modes differ, and whether dual-supply or single-supply device functionality better suits the system under consideration. Given this, then device selection can begin and an application developed.

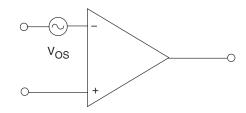

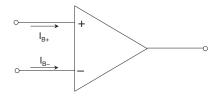

First, an *operational amplifier* (hereafter simply op amp) is a differential input, single-ended output amplifier, as shown symbolically in Figure 1-1. This device is an amplifier intended for use with *external feedback elements*, where these elements determine the resultant function, or *operation*. This gives rise to the name "operational amplifier," denoting an amplifier that, by virtue of different feedback hookups, can perform a variety of operations.<sup>1</sup> At this point, note that there is no need for concern with any actual technology to implement the amplifier. Attention is focused more on the behavioral nature of this building block device.

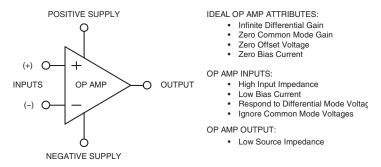

Figure 1-1: The ideal op amp and its attributes

An op amp processes small, differential mode signals appearing between its two inputs, developing a single-ended output signal referred to a power supply common terminal. Summaries of the various ideal op amp attributes are given in Figure 1-1. While real op amps will depart from these ideal attributes, it is very helpful for first-level understanding of op amp behavior to consider these features. Further, although these initial discussions talk in idealistic terms, they are also flavored by pointed mention of typical "real world" specifications—for a beginning perspective.

<sup>&</sup>lt;sup>1</sup> The actual *naming* of the operational amplifier occurred in the classic Ragazinni, et al paper of 1947 (see Reference 1). However, analog computations using op amps as we know them today began with the work of the Clarence Lovell-led group at Bell Labs, around 1940 (acknowledged generally in the Ragazinni paper).

It is also worth noting that this op amp is shown with five terminals, a number that happens to be a minimum for real devices. While some single op amps may have more than five terminals (to support such functions as frequency compensation, for example), none will ever have fewer. By contrast, those elusive ideal op amps don't require power, and symbolically function with just four pins.<sup>2</sup>

## Ideal Op Amp Attributes

An ideal op amp has infinite gain for *differential* input signals. In practice, real devices will have quite high gain (also called *open-loop gain*) but this gain won't necessarily be precisely known. In terms of specifications, gain is measured in terms of  $V_{OUT}/V_{IN}$ , and is given in V/V, the dimensionless numeric gain. More often, however, gain is expressed in decibel terms (dB), which is mathematically dB = 20 • log (numeric gain). For example, a numeric gain of 1 million (10<sup>6</sup> V/V) is equivalent to a 120 dB gain. Gains of 100 dB – 130 dB are common for precision op amps, while high speed devices may have gains in the 60 dB – 70 dB range.

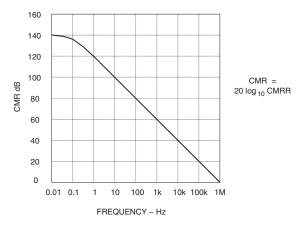

Also, an ideal op amp has zero gain for signals *common* to both inputs, that is, *common-mode* (CM) signals. Or, stated in terms of the rejection for these common-mode signals, an ideal op amp has infinite *CM rejection* (CMR). In practice, real op amps can have CMR specifications of up to 130 dB for precision devices, or as low as 60 dB–70 dB for some high speed devices.

The ideal op amp also has zero *offset voltage* ( $V_{os} = 0$ ), and draws zero *bias current* ( $I_B = 0$ ) at both inputs. Within real devices, actual offset voltages can be as low as 1  $\mu$ V or less, or as high as several mV. Bias currents can be as low as a few fA, or as high as several  $\mu$ A. This extremely wide range of specifications reflects the different input structures used within various devices, and is covered in more detail later in this chapter.

The attribute headings within Figure 1-1 for INPUTS and OUTPUT summarize the above concepts in more succinct terms. In practical terms, another important attribute is the concept of *low source impedance*, at the output. As will be seen later, low source impedance enables higher useful gain levels within circuits.

To summarize these idealized attributes for a signal processing amplifier, some of the traits might at first seem strange. However, it is critically important to reiterate that op amps simply are never intended for use without overall feedback. In fact, as noted, the connection of a suitable *external* feedback loop defines the *closed-loop* amplifier's gain and frequency response characteristics.

Note also that all real op amps have a positive and negative power supply terminal, but rarely (if ever) will they have a separate ground connection. In practice, the op amp output voltage becomes referred to a power supply common point. *Note: This key point is further clarified with the consideration of typically used op amp feedback networks.*

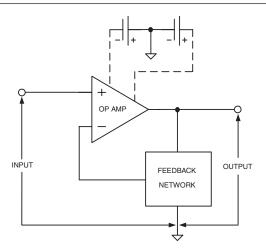

The basic op amp hookup of Figure 1-2 applies a signal to the (+) input, and a (generalized) network delivers a fraction of the output voltage to the (-) input terminal. This constitutes *feedback*, with the op amp operating in *closed-loop* fashion. The feedback network (shown here in general form) can be resistive or reactive, linear or nonlinear, or any combination of these. More detailed analysis will show that the circuit gain characteristic as a whole follows the inverse of the feedback network transfer function.

The concept of feedback is both an essential and salient point concerning op amp use. With feedback, the net closed-loop gain characteristics of a stage such as Figure 1-2 become primarily dependent upon a set of *external components* (usually passive). Thus behavior is less dependent upon the relatively unstable amplifier open-loop characteristics.

<sup>&</sup>lt;sup>2</sup> Such an op amp generates its own power, has two input pins, an output pin, and an output common pin.

Figure 1-2: A generalized op amp circuit with feedback applied

Note that within Figure 1-2, the input signal is applied between the op amp (+) input and a *common* or *reference point*, as denoted by the ground symbol. It is important to note that this reference point is also common to the output and feedback network. By definition, the op amp stage's output signal appears between the output terminal/feedback network input, and this common ground. This single relevant fact answers the "Where is the op amp grounded?" question so often asked by those new to the craft. The answer is simply that it is grounded *indirectly*, by virtue of the commonality of its input, the feedback network, and the power supply, as is shown in Figure 1-2.

To emphasize how the input/output signals are referenced to the power supply, dual supply connections are shown dotted, with the  $\pm$  power supply midpoint common to the input/output signal ground. But do note, while all op amp application circuits may not show full details of the power supply connections, every *real* circuit will always use power supplies.

## Standard Op Amp Feedback Hookups

Virtually all op amp feedback connections can be categorized into just a few basic types. These include the two most often used, *noninverting* and *inverting* voltage gain stages, plus a related *differential* gain stage. Having discussed above just the attributes of the ideal op amp, at this point it is possible to conceptually build basic gain stages. Using the concepts of infinite gain, zero input offset voltage, zero bias current, and so forth, standard op amp feedback hookups can be devised. For brevity, a full mathematical development of these concepts isn't included here (but this follows in a subsequent section). The end-of-section references also include such developments.

#### The Noninverting Op Amp Stage

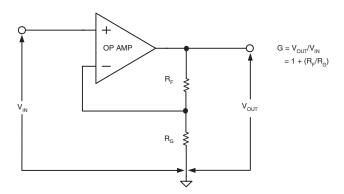

The op amp noninverting gain stage, also known as a *voltage follower with gain*, or simply *voltage follower*, is shown in Figure 1-3.

Figure 1-3: The noninverting op amp stage (voltage follower)

This op amp stage processes the input  $V_{IN}$  by a gain of G, so a generalized expression for gain is:

$$G = \frac{V_{OUT}}{V_{IN}}$$

Eq. 1-1

Feedback network resistances  $R_F$  and  $R_G$  set the stage gain of the follower. For an ideal op amp, the gain of this stage is:

$$G = \frac{R_F + R_G}{R_G}$$

Eq. 1-2

For clarity, these expressions are also included in the figure. Comparison of this figure and the more general Figure 1-2 shows  $R_F$  and  $R_G$  here as a simple feedback network, returning a fraction of  $V_{OUT}$  to the op amp (–) input. (*Note that some texts may show the more general symbols*  $Z_F$  and  $Z_G$  for these feedback components—both are correct, depending upon the specific circumstances.)

In fact, we can make some useful general points about the network  $R_F - R_G$ . We will define the transfer expression of the network as seen from the top of  $R_F$  to the output across  $R_G$  as  $\beta$ . Note that this usage is a general feedback network transfer term, *not* to be confused with bipolar transistor forward gain.  $\beta$  can be expressed mathematically as:

$$\beta = \frac{R_G}{R_F + R_G}$$

Eq. 1-3

So, the feedback network returns a fraction of  $V_{OUT}$  to the op amp (-) input. Considering the ideal principles of zero offset and infinite gain, this allows some deductions on gain to be made. The voltage at the (-) input is forced by the op amp's feedback action to be equal to that seen at the (+) input,  $V_{IN}$ . Given this relationship, it is relatively easy to work out the ideal gain of this stage, which in fact turns out to be simply the inverse of  $\beta$ . This is apparent from a comparison of Eqs. 1-2 and 1-3.

Thus an ideal noninverting op amp stage gain is simply equal to  $1/\beta$ , or:

$$G = \frac{1}{\beta}$$

Eq. 1-4

This noninverting gain configuration is one of the most useful of all op amp stages, for several reasons. Because  $V_{IN}$  sees the op amp's high impedance (+) input, it provides an ideal interface to the driving source. Gain can easily be adjusted over a wide range via  $R_F$  and  $R_G$ , with virtually no source interaction.

A key point is the interesting relationship concerning  $R_F$  and  $R_G$ . Note that to satisfy the conditions of Eq. 1-2, only their *ratio* is of concern. In practice this means that stable gain conditions can exist over a range of actual  $R_F - R_G$  values, so long as they provide the same ratio.

If  $R_F$  is taken to zero and  $R_G$  open, the stage gain becomes unity, and  $V_{OUT}$  is then exactly equal to  $V_{IN}$ . This special noninverting gain case is also called a *unity gain follower*, a stage commonly used for buffering a source.

Note that this op amp example shows only a simple resistive case of feedback. As mentioned, the feedback can also be reactive, i.e.,  $Z_F$ , to include capacitors and/or inductors. In all cases, however, it must include a dc path, if we are to assume the op amp is being biased by the feedback (which is usually the case).

To summarize some key points on op amp feedback stages, we paraphrase from Reference 2 the following statements, which will always be found useful:

The summing point idiom is probably the most used phrase of the aspiring analog artificer, yet the least appreciated. In general, the inverting (-) input is called the summing point, while the noninverting (+) input is represented as the reference terminal. However, a vital concept is the fact that, within linear op amp applications, the inverting input (or summing point) assumes the same absolute potential as the noninverting input or reference (within the gain error of the amplifier). In short, the amplifier tries to servo its own summing point to the reference.

## The Inverting Op Amp Stage

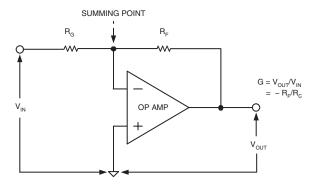

The op amp inverting gain stage, also known simply as the *inverter*, is shown in Figure 1-4. As can be noted by comparison of Figures 1-3 and 1-4, the inverter can be viewed as similar to a follower, but with a transposition of the input voltage  $V_{IN}$ . In the inverter, the signal is applied to  $R_G$  of the feedback network and the op amp (+) input is grounded.

Figure 1-4: The inverting op amp stage (inverter)

The feedback network resistances  $R_F$  and  $R_G$  set the stage gain of the inverter. For an ideal op amp, the gain of this stage is:

$$G = -\frac{R_{\rm F}}{R_{\rm G}}$$

Eq. 1-5

For clarity, these expressions are again included in the figure. Note that a major difference between this stage and the noninverting counterpart is the input-to-output sign reversal, denoted by the minus sign in Eq. 1-5. Like the follower stage, applying ideal op amp principles and some basic algebra can derive the gain expression of Eq. 1-5.

The inverting configuration is also one of the more useful op amp stages. Unlike a noninverting stage, however, the inverter presents a relatively low impedance input for  $V_{IN}$ , i.e., the value of  $R_G$ . This factor provides a finite load to the source. While the stage gain can in theory be adjusted over a wide range via  $R_F$  and  $R_G$ , there is a practical limitation imposed at high gain, when  $R_G$  becomes relatively low. If  $R_F$  is zero, the gain becomes zero.  $R_F$  can also be made variable, in which case the gain is linearly variable over the dynamic range of the element used for  $R_F$ . As with the follower gain stage, the gain is ratio dependent, and is relatively insensitive to the exact  $R_F$  and  $R_G$  values.

The inverter's gain behavior, due to the principles of infinite op amp gain, zero input offset, and zero bias current, gives rise to an effective node of zero voltage at the (-) input. The input and feedback currents sum at this point, which logically results in the term *summing point*. It is also called a *virtual ground*, because of the fact it will be at the same potential as the grounder efference input.

Note that, technically speaking, *all* op amp feedback circuits have a summing point, whether they are inverters, followers, or a hybrid combination. The summing point is always the feedback junction at the (-) input node, as shown in Figure 1-4. However in follower type circuits this point isn't a virtual ground, since it follows the (+) input.

A special gain case for the inverter occurs when  $R_F = R_G$ , which is also called a *unity gain inverter*. This form of inverter is commonly used for generating complementary  $V_{OUT}$  signals, i.e.,  $V_{OUT} = -V_{IN}$ . In such cases it is usually desirable to match  $R_F$  to  $R_G$  accurately, which can readily be done by using a well-specified matched resistor pair.

A variation of the inverter is the *inverting summer*, a case similar to Figure 1-4, but with input resistors  $R_{G2}$ ,  $R_{G3}$ , etc (not shown). For a summer individual input resistors are connected to additional sources  $V_{IN2}$ ,  $V_{IN3}$ , and so forth, with their common node connected to the summing point. This configuration, called a *summing amplifier*, allows linear input current summation in  $R_{F}$ .<sup>3</sup>  $V_{OUT}$  is proportional to an inverse sum of input currents.

## The Differential Op Amp Stage

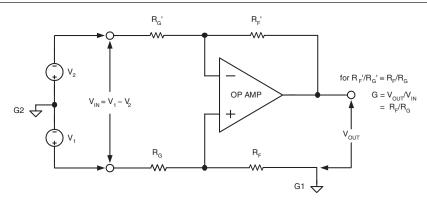

The op amp differential gain stage (also known as a differential amplifier, or subtractor) is shown in Figure 1-5.

Paired input and feedback network resistances set the gain of this stage. These resistors,  $R_F-R_G$  and  $R_F'-R_G'$ , *must be matched as noted*, for proper operation. Calculation of individual gains for inputs  $V_1$  and  $V_2$  and their linear combination derives the stage gain.

<sup>&</sup>lt;sup>3</sup> The very first general-purpose op amp circuit is described by Karl Swartzel in Reference 3, and is titled "Summing Amplifier." This amplifier became a basic building block of the M9 gun director computer and fire control system used by Allied Forces in World War II. It also influenced many vacuum tube op amp designs that followed over the next two decades.

Figure 1-5: The differential amplifier stage (subtractor)

Note that the stage is intended to amplify the *difference* of voltages  $V_1$  and  $V_2$ , so the net input is  $V_{IN} = V_1 - V_2$ . The general gain expression is then:

$$G = \frac{V_{OUT}}{V_1 - V_2}$$

Eq. 1-6

For an ideal op amp and the resistor ratios matched as noted, the gain of this differential stage from  $V_{IN}$  to  $V_{OUT}$  is:

$$G = \frac{R_F}{R_G}$$

Eq. 1-7

The great fundamental utility that an op amp stage such as this allows is the property of rejecting voltages *common* to  $V_1-V_2$ , i.e., common-mode (CM) voltages. For example, if noise voltages appear between grounds G1 and G2, the noise will be suppressed by the common-mode rejection (CMR) of the differential amp. The CMR however is only as good as the matching of the resistor ratios allows, so in practical terms it implies precisely trimmed resistor ratios are necessary. Another disadvantage of this stage is that the resistor networks load the  $V_1-V_2$  sources, potentially leading to additional errors.

## The Nonideal Op Amp—Static Errors Due to Finite Amplifier Gain

One of the most distinguishing features of op amps is their staggering magnitude of dc voltage gain. Even the least expensive devices have typical voltage gains of 100,000 (100 dB), while the highest performance precision bipolar and chopper stabilized units can have gains as high 10,000,000 (140 dB), or more. Negative feedback applied around this much voltage gain readily accomplishes the virtues of closed-loop performance, making the circuit dependent only on the feedback components.

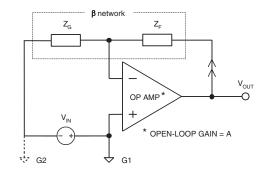

As noted above in the discussion of ideal op amp attributes, the behavioral assumptions follow from the fact that negative feedback, coupled with high open-loop gain, constrains the amplifier input error voltage (and consequently the error current) to infinitesimal values. The higher this gain, the more valid these assumptions become. In reality, however, op amps *do* have finite gain and errors exist in practical circuits. The op amp gain stage of Figure 1-6 will be used to illustrate how these errors impact performance. In this circuit the op amp is ideal except for the finite open-loop dc voltage gain, A, which is usually stated as A<sub>VOL</sub>.

Figure 1-6: Nonideal op amp stage for gain error analysis

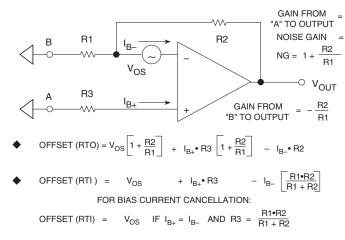

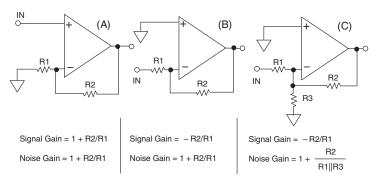

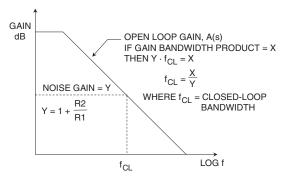

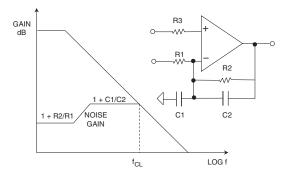

#### Noise Gain (NG)

The first aid to analyzing op amps circuits is to differentiate between *noise gain* and *signal gain*. We have already discussed the differences between noninverting and inverting stages as to their signal gains, which are summarized in Eqs. 1-2 and 1-4, respectively. But, as can be noticed from Figure 1-6, the difference between an inverting and noninverting stage can be as simple as where the reference ground is placed. For a ground at point G1, the stage is an inverter; conversely, if the ground is placed at point G2 (with no G1) the stage is noninverting.

Note, however, that in terms of the feedback path, *there are no real differences*. To make things more general, the resistive feedback components previously shown are replaced here with the more general symbols  $Z_F$  and  $Z_G$ , otherwise they function as before. The feedback attenuation,  $\beta$ , is the same for both the inverting and noninverting stages:

$$\beta = \frac{Z_G}{Z_G + Z_F}$$

Eq. 1-8

Noise gain can now be simply defined as: *The inverse of the net feedback attenuation from the amplifier output to the feedback input.* In other words, the inverse of the  $\beta$  network transfer function. This can ultimately be extended to include frequency dependence (covered later in this chapter). Noise gain can be abbreviated as NG.

As noted, the inverse of  $\beta$  is the ideal noninverting op amp stage gain. Including the effects of finite op amp gain, a modified gain expression for the noninverting stage is:

$$G_{CL} = \frac{1}{\beta} \times \left[ \frac{1}{1 + \frac{1}{A_{VOL}\beta}} \right]$$

Eq. 1-9

where  $G_{CL}$  is the finite-gain stage's closed-loop gain, and  $A_{VOL}$  is the op amp open-loop voltage gain for loaded conditions.

It is important to note that this expression is identical to the ideal gain expression of Eq. 1-4, with the addition of the bracketed multiplier on the right side. Note also that this right-most term becomes closer and closer to unity, as  $A_{VOL}$  approaches infinity. Accordingly, it is known in some textbooks as the *error multiplier* term, when the expression is shown in this form.<sup>4</sup>

It may seem logical here to develop another finite gain error expression for an inverting amplifier, but in actuality there is no need. Both inverting and noninverting gain stages have a common feedback basis, which is the noise gain. So Eq. 1-9 will suffice for gain error analysis for both stages. Simply use the  $\beta$  factor as it applies to the specific case.

It is useful to note some assumptions associated with the rightmost error multiplier term of Eq. 1-9. For  $A_{VOL}\beta >> 1$ , one assumption is:

$$\frac{1}{1 + \frac{1}{A_{\text{VOL}}\beta}} \approx 1 - \frac{1}{A_{\text{VOL}}\beta}$$

Eq. 1-10

This in turn leads to an estimation of the percentage error,  $\varepsilon$ , due to finite gain A<sub>VOL</sub>:

$$\varepsilon(\%) \approx \frac{100}{A_{VOL}\beta}$$

Eq. 1-11

#### Gain Stability

The closed-loop gain error predicted by these equations isn't in itself tremendously important, since the ratio  $Z_F/Z_G$  could always be adjusted to compensate for this error.

But note however that closed-loop gain *stability* is a very important consideration in most applications. Closed-loop gain instability is produced primarily by variations in open-loop gain due to changes in temperature, loading, and so forth.

$$\frac{\Delta G_{\rm CL}}{G_{\rm CL}} \approx \frac{\Delta A_{\rm VOL}}{A_{\rm VOL}} \times \frac{1}{A_{\rm VOL}\beta}$$

Eq. 1-12

From Eq. 1-12, any variation in open-loop gain  $(\Delta A_{VOL})$  is reduced by the factor  $A_{VOL}\beta$ , insofar as the effect on closed-loop gain. This improvement in closed-loop gain stability is one of the important benefits of negative feedback.

### Loop Gain

The product  $A_{VOL}\beta$ , which occurs in the above equations, is called *loop gain*, a well-known term in feedback theory. The improvement in closed-loop performance due to negative feedback is, in nearly every case, proportional to loop gain.

The term "loop gain" comes from the method of measurement. This is done by breaking the closed feedback loop at the op amp output, and measuring the total gain around the loop. In Figure 1-6 for example, this could be done between the amplifier output and the feedback path (see arrows). To a first

<sup>&</sup>lt;sup>4</sup> Some early discussions of this finite gain error appear in References 4 and 5. Terman uses the open-loop gain symbol of A, as we do today. West uses Harold Black's original notation of  $\mu$  for open-loop gain. The form of Eq. 1-9 is identical to Terman's (or to West's, substituting  $\mu$  for A).

approximation, closed-loop output impedance, linearity, and gain stability are all reduced by  $A_{VOL}\beta$  with the use of negative feedback.

Another useful approximation is developed as follows. A rearrangement of Eq. 1-9 is:

$$\frac{A_{VOL}}{G_{CL}} = 1 + A_{VOL}\beta$$

Eq. 1-13

So, for high values of  $A_{VOL}\beta$ ,

$$\frac{A_{VOL}}{G_{CL}} \approx A_{VOL}\beta$$

Eq. 1-14

Consequently, in a given feedback circuit the loop gain,  $A_{VOL}\beta$ , is approximately the numeric ratio (or difference, in dB) of the amplifier open-loop gain to the circuit closed-loop gain.

This loop gain discussion emphasizes that, indeed, loop gain is a very significant factor in predicting the performance of closed-loop operational amplifier circuits. The open-loop gain required to obtain an adequate amount of loop gain will, of course, depend on the desired closed-loop gain.

For example, using Eq. 1-14, an amplifier with  $A_{VOL} = 20,000$  will have an  $A_{VOL}\beta \approx 2000$  for a closed-loop gain of 10, but the loop gain will be only 20 for a closed-loop gain of 1000. The first situation implies an amplifier-related gain error on the order of  $\approx 0.05\%$ , while the second would result in about 5% error. Obviously, the higher the required gain, the greater will be the required open-loop gain to support an  $A_{VOL}\beta$  for a given accuracy.

### Frequency Dependence of Loop Gain

Thus far, it has been assumed that amplifier open-loop gain is independent of frequency. Unfortunately, this isn't the case. Leaving the discussion of the effect of open-loop response on bandwidth and dynamic errors until later, let us now investigate the general effect of frequency response on loop gain and static errors.

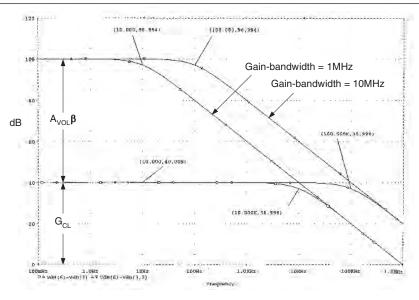

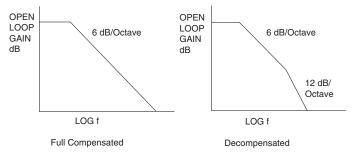

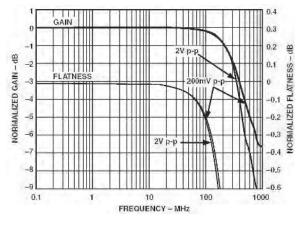

The open-loop frequency response for a typical operational amplifier with superimposed closed-loop amplifier response for a gain of 100 (40 dB), illustrates graphically these results in Figure 1-7. In these Bode plots, subtraction on a logarithmic scale is equivalent to normal division of numeric data.<sup>5</sup> Today, op amp openloop gain and loop gain parameters are typically given in dB terms, thus this display method is convenient.

A few key points evolve from this graphic figure, which is a simulation involving two hypothetical op amps, both with a dc/low frequency gain of 100 dB (100 kV/V). The first has a gain-bandwidth of 1 MHz, while the gain-bandwidth of the second is 10 MHz.

- The open-loop gain  $A_{VOL}$  for the two op amps is noted by the two curves marked 1 MHz and 10 MHz, respectively. Note that each has a -3 dB corner frequency associated with it, above which the open-loop gain falls at 6 dB/octave. These corner frequencies are marked at 10 Hz and 100 Hz, respectively, for the two op amps.

- At any frequency on the open-loop gain curve, the numeric product of gain A<sub>VOL</sub> and frequency, f, is a constant (10,000 V/V at 100 Hz equates to 1 MHz). This, by definition, is characteristic of a constant gain-bandwidth product amplifier. All *voltage feedback* op amps behave in this manner.

<sup>&</sup>lt;sup>5</sup> The log-log displays of amplifier gain (and phase) versus frequency are called *Bode* plots. This graphic technique for display of feedback amplifier characteristics, plus definitions for feedback amplifier stability were pioneered by Hendrick W. Bode of Bell Labs (see Reference 6).

Figure 1-7: Op amp closed-loop gain and loop gain interactions with typical open-loop responses

- $A_{VOL}\beta$  in dB is the difference between open-loop gain and closed-loop gain, as plotted on log-log scales. At the lower frequency point marked,  $A_{VOL}\beta$  is thus 60 dB.

- $A_{VOL}\beta$  decreases with increasing frequency, due to the decrease of  $A_{VOL}$  above the open-loop corner frequency. At 100 Hz for example, the 1 MHz gain-bandwidth amplifier shows an  $A_{VOL}\beta$  of only 80 db 40 db = 40 dB.

- $A_{VOL}\beta$  also decreases for higher values of closed-loop gain. Other, higher closed-loop gain examples (not shown) would decrease  $A_{VOL}\beta$  to less than 60 dB at low frequencies.

- $G_{CL}$  depends primarily on the ratio of the feedback components,  $Z_F$  and  $Z_G$ , and is relatively independent of  $A_{VOL}$  (apart from the errors discussed above, which are inversely proportional to  $A_{VOL}\beta$ ). In this example 1/ $\beta$  is 100, or 40 dB, and is so marked at 10 Hz. Note that  $G_{CL}$  is flat with increasing frequency, up until that frequency where  $G_{CL}$  intersects the open-loop gain curve, and  $A_{VOL}\beta$  drops to zero.

- At this point where the closed-loop and open-loop curves intersect, the loop gain is by definition zero, which implies that beyond this point there is no negative feedback. Consequently, closed-loop gain is equal to open-loop gain for further increases in frequency.

- Note that the 10 MHz gain-bandwidth op amp allows a 10× increase in closed-loop bandwidth, as can be noted from the -3 dB frequencies; that is 100 kHz versus 10 kHz for the 10 MHz versus the 1 MHz gain-bandwidth op amp.

Figure 1-7 illustrates that the high open-loop gain figures typically quoted for op amps can be somewhat misleading. As noted, beyond a few Hz, the open-loop gain falls at 6 dB/octave. Consequently, closed-loop gain stability, output impedance, linearity and other parameters dependent upon loop gain are degraded at higher frequencies. One of the reasons for having dc gain as high as 100 dB and bandwidth as wide as several MHz, is to obtain adequate loop gain at frequencies even as low as 100 Hz.

#### Chapter One

A direct approach to improving loop gain at high frequencies, other than by increasing open-loop gain, is to increase the amplifier open-loop bandwidth. Figure 1-7 shows this in terms of two simple examples. It should be borne in mind however that op amp gain-bandwidths available today extend to the hundreds of MHz, allowing video and high-speed communications circuits to fully exploit the virtues of feedback.

## Op Amp Common-Mode Dynamic Range(s)

As a point of departure from the idealized circuits above, some practical basic points are now considered. Among the most evident of these is the allowable input and output dynamic ranges afforded in a real op amp. This obviously varies with not only the specific device, but also the supply voltage. While we can always optimize this performance point with device selection, more fundamental considerations come first.

Any real op amp will have a finite voltage range of operation, at both input and output. In modern system designs, supply voltages are dropping rapidly, and 3 V - 5 V total supply voltages are now common. This is a far cry from supply systems of the past, which were typically  $\pm 15 V$  (30 V total). Obviously, if designs are to accommodate a 3 V - 5 V supply, careful consideration must be given to maximizing dynamic range, by choosing a correct device. Choosing a device will be in terms of exact specifications, but first and foremost it should be in terms of the basic topologies used within it.

### **Output Dynamic Range**

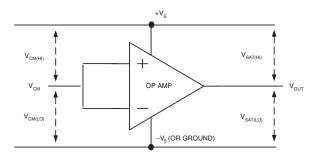

Figure 1-8 is a general illustration of the limitations imposed by input and output dynamic ranges of an op amp, related to both supply rails. Any op amp will always be powered by two supply potentials, indicated by the positive rail,  $+V_s$ , and the negative rail,  $-V_s$ . We will define the op amp's input and output CM range in terms of how closely it can approach these two rail voltage limits.

Figure 1-8: Op amp input and output common-mode ranges

At the output,  $V_{OUT}$  has two rail-imposed limits, one high or close to  $+V_s$ , and one low, or close to  $-V_s$ . Going high, it can range from an upper saturation limit of  $+V_s - V_{SAT(HI)}$  as a positive maximum. For example if  $+V_s$  is 5 V, and  $V_{SAT(HI)}$  is 100 mV, the upper  $V_{OUT}$  limit or positive maximum is 4.9 V. Similarly, going low it can range from a lower saturation limit of  $-V_s + V_{SAT(LO)}$ . So, if  $-V_s$  is ground (0 V) and  $V_{SAT(HI)}$  is 50 mV, the lower limit of  $V_{OUT}$  is simply 50 mV.

Obviously, the internal design of a given op amp will impact this output CM dynamic range, since, when so necessary, the device itself must be designed to minimize both  $V_{SAT(HI)}$  and  $V_{SAT(LO)}$ , to maximize the output dynamic range. Certain types of op amp structures are so designed, and these are generally associated with designs expressly for *single-supply* systems. This is covered in detail later within the chapter.

#### Input Dynamic Range

At the input, the CM range useful for  $V_{IN}$  also has two rail-imposed limits, one high or close to  $+V_s$ , and one low, or close to  $-V_s$ . Going high, it can range from an upper CM limit of  $+V_s - V_{CM(HI)}$  as a positive maximum. For example, again using the  $+V_s = 5$  V example case, if  $V_{CM(HI)}$  is 1 V, the upper  $V_{IN}$  limit or positive CM maximum is  $+V_s - V_{CM(HI)}$ , or 4 V.

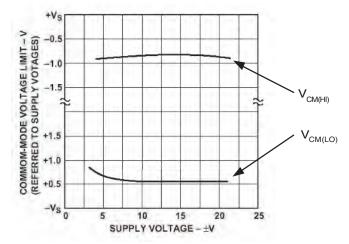

Figure 1-9 illustrates by way of a hypothetical op amp's data how  $V_{CM(HI)}$  could be specified, as shown in the upper curve. This particular op amp would operate for  $V_{CM}$  inputs *lower* than the curve shown.

Figure 1-9: A graphical display of op amp input common mode range

In practice the input CM range of real op amps is typically specified as a *range of voltages*, not necessarily referenced to  $+V_s$  or  $-V_s$ . For example, a typical  $\pm 15$  V operated dual supply op amp would be specified for an operating CM range of  $\pm 13$  V. Going low, there will also be a lower CM limit. This can be generally expressed as  $-V_s + V_{CM(LO)}$ , which would appear in a graph such as Figure 1-9 as the lower curve, for  $V_{CM(LO)}$ . If this were again a  $\pm 15$  V part, this could represent typical performance.

To use a single-supply example, for the  $-V_s = 0$  V case, if  $V_{CM(LO)}$  is 100 mV, the lower CM limit will be 0 V + 0.1 V, or simply 0.1 V. Although this example illustrates a lower CM range within 100 mV of  $-V_s$ , it is actually much more typical to see single-supply devices with lower or upper CM ranges, which *include* the supply rail.

In other words,  $V_{CM(LO)}$  or  $V_{CM(HI)}$  is 0 V. There are also single-supply devices with CM ranges that include *both* rails. More often than not, however, single-supply devices will not offer graphical data such as Figure 1-9 for CM limits, but will simply cover performance with a tabular range of specified voltage.

## Functionality Differences of Dual-Supply and Single-Supply Devices

There are two major classes of op amps, the choice of which determines how well the selected part will function in a given system. Traditionally, many op amps have been designed to operate on a dual power supply system, which has typically been  $\pm 15$  V. This custom has been prevalent since the earliest IC op amps days, dating back to the mid-sixties. Such devices can accommodate input/output ranges of  $\pm 10$  V (or slightly more), but when operated on supplies of appreciably lower voltage, for example  $\pm 5$  V or less, they suffer either loss of performance, or simply don't operate at all. This type of device is referenced here as a *dual-supply* op amp design. This moniker indicates that it performs optimally on dual voltage systems only, typically  $\pm 15$  V. It may or may not also work at appreciably lower voltages.

Figure 1-10 illustrates in a broad overview the relative functional performance differences that distinguish the dual-supply versus single-supply op amp classes. This table is arranged to illustrate various general performance parameters, with an emphasis on the contrast between single-and dual-supply devices. Which particular performance area is more critical will determine which type of device will be the better system choice.

| PERFORMANCE<br>PARAMETER | DUAL SUPPLY  | SINGLE SUPPLY                      |

|--------------------------|--------------|------------------------------------|

|                          |              |                                    |

| SUPPLY                   | Best >10V,   | Best <10V,                         |

| LIMITATIONS              | Limited <10V | Limited >10V                       |

| OUTPUT V                 | - Limited    | + Greatest                         |

| RANGE                    |              |                                    |

| INPUT V                  | - Limited    | + Greatest                         |

| RANGE                    |              |                                    |

| TOTAL                    | + Greatest   | - Least                            |

| DYNAMIC                  |              |                                    |

| RANGE                    |              |                                    |

| V & I OUTPUT             | + Greater    | – Less                             |

| PRECISION                | + Greatest   | <ul> <li>Less (growing)</li> </ul> |

| LOAD                     | + Greatest   | - Least                            |

| IMMUNITY                 |              |                                    |

| VARIETY                  | + Greater    | <ul> <li>Less (growing)</li> </ul> |

| AVAILABLE                |              |                                    |

|                          |              |                                    |

# Figure 1-10: Comparison of relative functional performance differences between single and dual-supply op amps

More recently, with increasing design attention to lower overall system power and the use of single rail power, the single-supply op amp has come into vogue. This has not been without good reason, as the virtues of using single supply rails can be quite compelling. A review of Figure 1-10 illustrates key points of the dual versus single supply op amp question.

In terms of *supply voltage limitations*, there is a crossover region in terms of overall utility, which occurs around 10 V of total supply voltage.

For example, single-supply devices tend to excel in terms of their *input and output voltage dynamic ranges*. Note that in Figure 1-10 a maximum range is stated as a percentage of available supply. Single-supply parts operate better in this regard, because they are internally designed to maximize these respective ranges. For example, it is not unusual for a device operating from 5 V to swing 4.8 V at the output, and so on.

But, rather interestingly, such devices are also usually restricted to lower supply ranges (only), so their upper dynamic range in absolute terms is actually more limited. For example, a traditional  $\pm 15$  V

dual-supply device can typically swing 20 V p-p, or more than four times that of a 5 V single-supply part. If the *total dynamic range* is considered (assuming an identical input noise), the dual-supply operated part will have four times (or 12 dB) greater dynamic range than that of the 5 V operated part. Or, stated in another way, the input errors of a real part such as noise, drift, and so forth, become four times more critical (relatively speaking), when the output dynamic range is reduced by a factor of 4. Note that these comparisons do not involve any actual device specifications, *they are simply system-based observations*. Device specifications are covered later in this chapter.

In terms of total *voltage and current output*, dual-supply parts tend to offer more in absolute terms, since single-supply parts are usually designed not just for low operating voltage ranges, but also for more modest current outputs.

In terms of *precision*, the dual-supply op amp has long been favored by designers for highest overall precision. However, this status quo is now beginning to be challenged, by such single-supply parts as the truly excellent chopper-stabilized op amps. With more and more new op amps being designed for single-supply use, high precision is likely to become an ever-increasing strength of this category.

*Load immunity* is often an application problem with single-supply parts, as many of them use commonemitter or common-source output stages, to maximize signal swing. Such stages are typically much more load sensitive than the classic common-collector stages generally used in dual-supply op amps.

There is now a greater *variety* of dual-supply op amps available. However, this is at least in part due to the ~30-year head start they have been enjoying. Currently, new op amp designs are increasingly oriented around one or more aspects of single-supply compatibility, with strong trends toward lower supply voltages, smaller packages, and so forth.

## **Device Selection Drivers**

As the op amp design process is begun, it is useful to keep in mind the fact that there are several selection *drivers*, which can dictate priorities. This is illustrated by Figure 1-11.

| FUNCTION      | PERFORM     | PACKAGE   | MARKET       |

|---------------|-------------|-----------|--------------|

|               |             |           |              |

| Single, Dual, | Precision   | Туре      | Cost         |

| Quad          |             |           |              |

| Single Or     | Speed       | Size      | Availability |

| Dual Supply   |             |           |              |

| Supply        | Distortion, | Footprint |              |

| Voltage       | Noise       |           |              |

|               | Low Bias    |           |              |

|               | Current     |           |              |

|               | Power       |           |              |

Actually, any *single* heading along the top of this chart can, in fact, be the dominant selection driver and take precedence over all of the others. In the early days of op amp design, when such things as supply range, package type, and so forth, were fairly narrow in spread, performance was usually the major driver. Of course, it is still very much so and will always be. But, today's systems are much more compact and lower in power, so things like package type, size, supply range, and multiple devices can often be major drivers of selection. As one example, if the only available supply voltage is 3 V, look at 3 V compatible devices first, and then fill other performance parameters as you can.

#### Chapter One

As another example, one coming from another perspective, sometimes all-out performance can drive everything else. An ultralow, non-negotiable input current requirement can drive not only the type of amplifier, but also its package (a FET input device in a glass-sealed hermetic package may be optimum). Then, everything else follows from there. Similarly, high power output may demand a package capable of several watts dissipation; in which case, find the power handling device and package first, and then proceed accordingly.

At this point, the concept of these "selection drivers" is still quite general. The following sections of the chapter introduce device types, which supplement this with further details of a realistic selection process.

## Classic Cameo Ray Stata Publications Establish ADI Applications Work

In January of 1965 Analog Devices Inc. (ADI) was founded by Matt Lorber and Ray Stata. Operating initially from Cambridge, MA, modular op amps were the young ADI's primary product. In those days, Ray Stata did more than administrative tasks. He served in sales and marketing roles, and wrote many op amp applications articles. Even today, some of these are still available to ADI customers.

One very early article set was a two part series done for **Electromechanical Design**, which focused on clear, down-to-earth explanation of op amp principles.<sup>1</sup>

A second article for the new ADI publication **Analog Dialogue** was titled "Operational Integrators," and outlined various errors that plague integrators (including capacitor errors).<sup>2</sup>

A third impact article was also done for **Analog Dialogue**, titled "User's Guide to Applying and Measuring Operational Amplifier Specifications."<sup>3</sup> As the title denotes, this was a comprehensive guide to aid the understanding of op amp specifications, and also showed how to test them.

Ray authored an Applications Manual for the 201, 202, 203 and 210 series of chopper op amps.<sup>4</sup>

Ray was also part of the **EEE** "Speaks Out" series of article-interviews, where he outlined some of the subtle ways that op amp specs and behavior can trap unwary users (above photo from that article).<sup>5</sup>

Although ADI today makes many other products, those early op amps were the company's roots.

<sup>&</sup>lt;sup>1</sup> Ray Stata, "Operational Amplifiers – Parts I and II," Electromechanical Design, Sept., Nov., 1965.

<sup>&</sup>lt;sup>2</sup> Ray Stata, "Operational Integrators," Analog Dialogue, Vol. 1, No. 1, April, 1967. See also ADI AN357.

<sup>&</sup>lt;sup>3</sup> Ray Stata, "User's Guide to Applying and Measuring Operational Amplifier Specifications," **Analog Dialogue,** Vol. 1, No. 3, September 1967. See also ADI AN356.

<sup>&</sup>lt;sup>4</sup> Ray Stata, Applications Manual for 201, 202, 203 and 210 Chopper Op Amps, ADI, 1967.

<sup>&</sup>lt;sup>5</sup> "Ray Stata Speaks Out on 'What's Wrong with Op Amp Specs'," EEE, July 1968.

### **References: Introduction**

- 1. John R. Ragazzini, Robert H. Randall and Frederick A. Russell, "Analysis of Problems in Dynamics by Electronic Circuits," **Proceedings of the IRE**, Vol. 35, May 1947, pp. 444–452.

- 2. Walter Borlase, **An Introduction to Operational Amplifiers (Parts 1–3)**, September 1971, Analog Devices Seminar Notes, Analog Devices, Inc.

- 3. Karl D. Swartzel, Jr. "Summing Amplifier," US Patent 2,401,779, filed May 1, 1941, issued June 11, 1946.

- 4. Frederick E. Terman, "Feedback Amplifier Design," **Electronics**, Vol. 10, No. 1, January 1937, pp. 12–15, 50.

- 5. Julian M. West, "Wave Amplifying System," US Patent 2,196,844, filed April 26, 1939, issued April 9, 1940.

- Hendrick W. Bode, "Relations Between Attenuation and Phase In Feedback Amplifier Design," Bell System Technical Journal, Vol. 19, No. 3, July, 1940. See also: "Amplifier," US Patent 2,173,178, filed June 22, 1937, issued July 12, 1938.

- 7. Ray Stata, "Operational Amplifiers-Parts I and II," **Electromechanical Design**, September, November 1965.

- Dan Sheingold, Ed., Applications Manual for Operational Amplifiers for Modeling, Measuring, Manipulating, and Much Else, George A. Philbrick Researches, Inc., Boston, MA, 1965. See also Applications Manual for Operational Amplifiers for Modeling, Measuring, Manipulating, and Much Else, 2<sup>nd</sup> Ed., Philbrick/Nexus Research, Dedham, MA, 1966, 1984.

- 9. Walter G. Jung, IC Op Amp Cookbook, 3<sup>rd</sup> Ed., Prentice-Hall PTR, 1986, 1997, ISBN: 0-13-889601-1.

- 10. Walt Kester, Editor, Linear Design Seminar, Analog Devices, Inc., 1995, ISBN: 0-916550-15-X.

- 11. Sergio Franco, **Design With Operational Amplifiers and Analog Integrated Circuits**, 2<sup>nd</sup> Ed. (Sections 1.2 1.4), McGraw-Hill, 1998, ISBN: 0-07-021857-9.

This page intentionally left blank

## SECTION 1-2

## **Op Amp Topologies** Walt Kester, Walt Jung, James Bryant

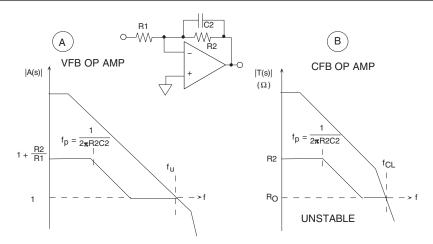

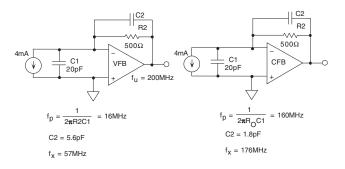

The previous section examined op amps without regard to their internal circuitry. In this section the two basic op amp topologies—voltage feedback (VFB) and current feedback (CFB)—are discussed in more detail, leading up to a detailed discussion of the actual circuit structures in Section 1-3.

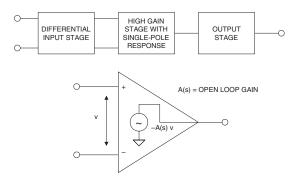

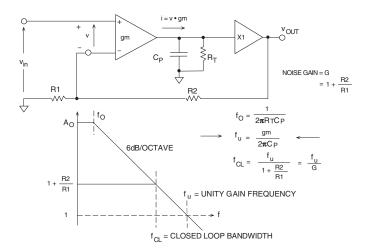

Figure 1-12: Voltage feedback (VFB) op amp

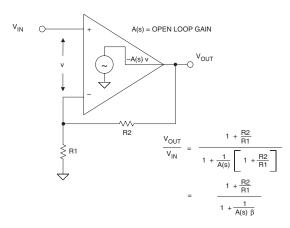

Although not explicitly stated, the previous section focused on the voltage feedback op amp and the related equations. In order to reiterate, the basic voltage feedback op amp is repeated here in Figure 1-12 (without the feedback network) and in Figure 1-13 (with the feedback network).

Figure 1-13: Voltage feedback op amp with feedback network connected

It is important to note that the error signal developed because of the feedback network and the finite openloop gain A(s) is in fact a small voltage, v.

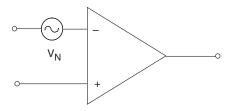

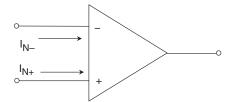

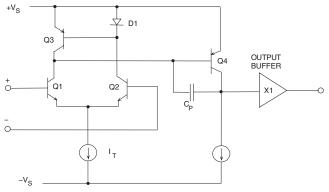

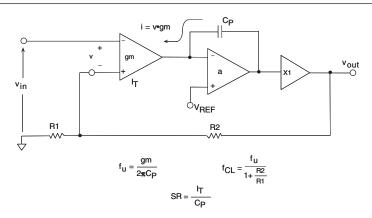

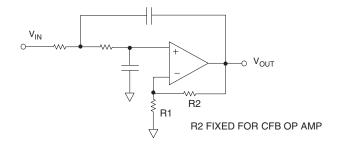

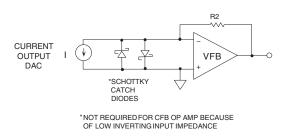

## **Current Feedback Amplifier Basics**

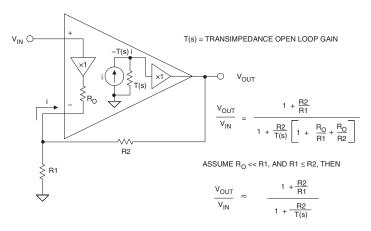

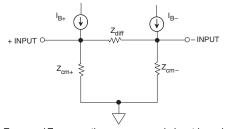

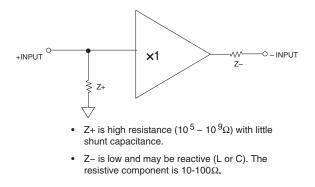

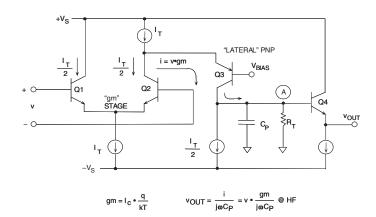

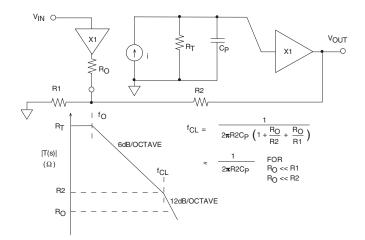

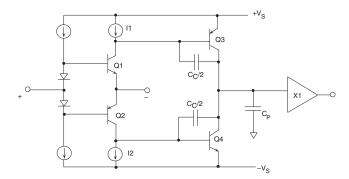

The basic *current feedback* amplifier topology is shown in Figure 1-14. Notice that within the model, a unity gain buffer connects the noninverting input to the inverting input. In the ideal case, the output impedance of this buffer is zero ( $R_0 = 0$ ), and the error signal is a small current, i, which flows into the inverting input. The error current, i, is mirrored into a high impedance, T(s), and the voltage developed across T(s) is equal to T(s)  $\cdot$  i. (The quantity T(s) is generally referred to as the *open-loop transimpedance gain*.)

This voltage is then buffered and connected to the op amp output. If  $R_0$  is assumed to be zero, it is easy to derive the expression for the closed-loop gain,  $V_{OUT}/V_{IN}$ , in terms of the R1-R2 feedback network and the *open-loop* transimpedance gain, T(s). The equation can also be derived quite easily for a finite  $R_0$ , and Figure 1-14 gives both expressions.

Figure 1-14: Current feedback (CFB) op amp topology

At this point it should be noted that current feedback op amps are often called *transimpedance* op amps, because the *open-loop* transfer function is in fact an impedance as described above. However, the term *transimpedance amplifier* is often applied to more general circuits such as current-to-voltage (I/V) converters, where either CFB or VFB op amps can be used. Therefore, some caution is warranted when the term *transimpedance* is encountered in a given application. On the other hand, the term *current feedback op amp* is rarely confused and is the preferred nomenclature when referring to op amp topology.

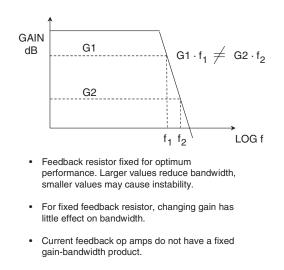

From this simple model, several important CFB op amp characteristics can be deduced.

- Unlike VFB op amps, CFB op amps *do not have balanced inputs*. Instead, the noninverting input is high impedance, and the inverting input is low impedance.

- The open-loop gain of CFB op amps is measured in units of  $\Omega$  (transimpedance gain) rather than V/V as for VFB op amps.

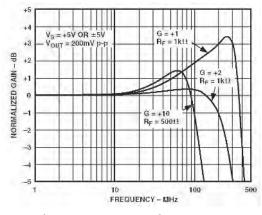

- For a fixed value feedback resistor R2, the closed-loop gain of a CFB can be varied by changing R1, without significantly affecting the closed-loop bandwidth. This can be seen by examining the simplified equation in Figure 1-14. The denominator determines the overall frequency response; and if R2 is constant, then R1 of the numerator can be changed (thereby changing the gain) without affecting the denominator—hence the bandwidth remains relatively constant.

The CFB topology is primarily used where the ultimate in high speed and low distortion is required. The fundamental concept is based on the fact that in bipolar transistor circuits currents can be switched faster than voltages, all other things being equal. A more detailed discussion of CFB op amp ac characteristics can be found in Section 1-5.

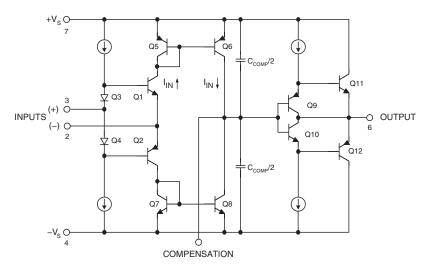

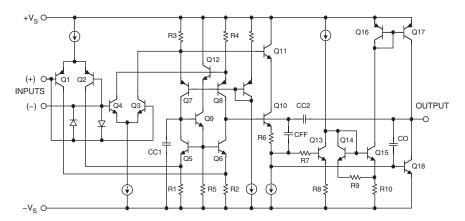

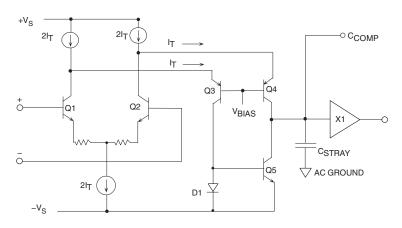

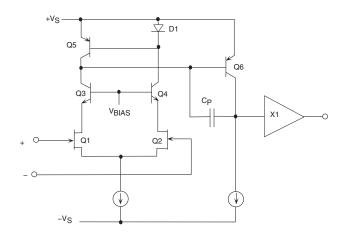

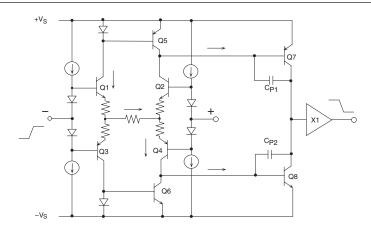

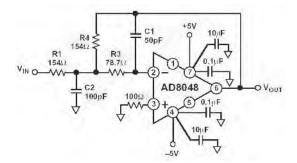

Figure 1-15 shows a simplified schematic of an early IC CFB op amp, the AD846—introduced by Analog Devices in 1988 (see Reference 1). Notice that full advantage is taken of the complementary bipolar (CB) process which provides well matched high f<sub>t</sub> PNP and NPN transistors.

Figure 1-15: AD846 current feedback op amp (1988)

Transistors Q1–Q2 buffer the noninverting input (Pin 3) and drive the inverting input (Pin 2). Q5–Q6 and Q7–Q8 act as current mirrors that drive the high impedance node. The  $C_{COMP}$  capacitor provides the dominant pole compensation; and Q9, Q10, Q11, and Q12 comprise the output buffer. In order to take full advantage of the CFB architecture, a high speed complementary bipolar (CB) IC process is required. With modern IC processes, this is readily achievable, allowing direct coupling in the signal path of the amplifier.

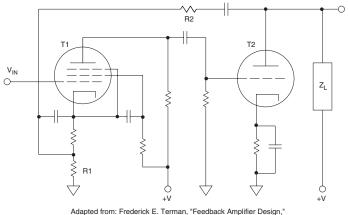

However, the basic concept of current feedback can be traced all the way back to early vacuum tube feedback circuitry, which used negative feedback to the input tube cathode. This use of the cathode for feedback would be analogous to the CFB op amp's low impedance (–) input, in Figure 1-15.

## **Current Feedback Using Vacuum Tubes**

Figure 1-16 is an adaptation from a 1937 article on feedback amplifiers by Frederick E. Terman (see Reference 2). Notice that the ac-coupled R2 feedback resistor for this two-stage amplifier is connected to the low impedance cathode of T1, the pentode vacuum tube input stage. Similar examples of early tube circuits using cathode feedback can be found in Reference 3.

Electronics , January 1937, pp. 12-15, 50.

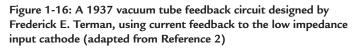

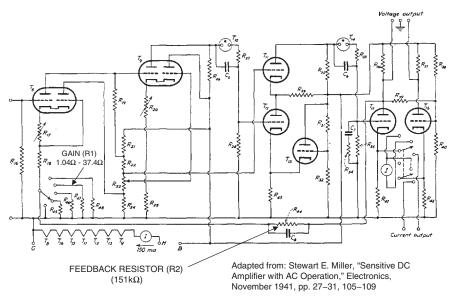

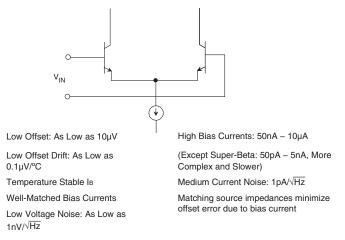

Dc-coupled op amp design using vacuum tubes was difficult for numerous reasons. One reason was a lack of suitable level shifters. Multistage op amps either required extremely high supply voltages or suffered gain loss because of resistive level shifters. In a 1941 article, Stewart E. Miller describes how to use gas discharge tubes as level shifters in several vacuum tube amplifier circuits (see Reference 4). A circuit of particular interest is shown in Figure 1-17.

In the Figure 1-17 reproduction of Miller's circuit, the R2 feedback resistor and the R1 gain setting resistor are labeled for clarity, and it can be seen that feedback is to the low impedance cathode of the input tube. The author suggests that the closed-loop gain of the amplifier can be adjusted from 72 dB–102 dB, by varying the R1 gain-setting resistor from 37.4  $\Omega$  to 1.04  $\Omega$ .

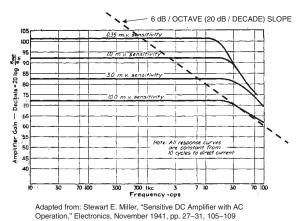

What is really interesting about the Miller circuit is its frequency response, which is reproduced in Figure 1-18. Notice that the closed-loop bandwidth is nearly independent of the gain setting, and the circuit certainly does not exhibit a constant gain-bandwidth product as would be expected for a traditional VFB op amp.

For a gain of 72 dB, the bandwidth is about 30 kHz, and for a gain of 102 dB (30 dB increase), the bandwidth only drops to ~15 kHz. With a 72 dB gain at 30 kHz VFB op amp, bandwidth would be expected to drop 5 octaves to ~0.9 kHz for 102 dB of gain.

Figure 1-17: A 1941 vacuum tube feedback circuit using current feedback

To clarify this point on bandwidth, a standard VFB op amp 6 dB/octave (20 dB/decade) slope has been added to Figure 1-18 for reference.

Although there is no mention of the significance of this within the text of the actual article, it nevertheless illustrates a popular application of CFB behavior, in the design of high speed programmable gain amplifiers with relatively constant bandwidth.

Figure 1-18: A 1941 feedback circuit shows

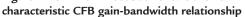

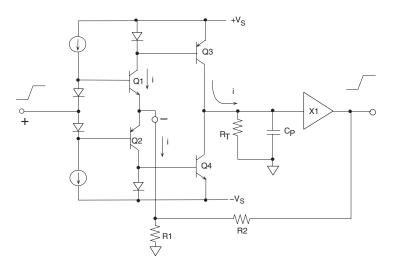

When transistor circuits ultimately replaced vacuum tube circuits between the late 1950s and the mid-1960s, the current feedback architecture became popular for certain high speed op amps. Figure 1-19 shows a fast-settling op amp designed at Bell Labs in 1965, for use as a building block in high speed A/D converters (see Reference 5).

Figure 1-19: A 1965 solid- state current feedback op amp design from Bell Labs

The circuit shown is a composite amplifier containing a high speed ac amplifier (shown inside the dotted outline) and a separate dc servo amplifier loop (not shown). The feedback resistor R2 is ac coupled to the low impedance emitter of transistor Q1. The circuit design was somewhat awkward because of the lack of good high frequency PNP transistors, and it also required zener diode level shifters, and nonstandard supplies.

Hybrid circuit manufacturing technology, which was well established by the 1980s, allowed the use of fast, relatively well-matched NPN and PNP transistors, to realize CFB op amps. The Analog Devices' AD9610 and AD9611 hybrids were good examples of these devices introduced in the mid-1980s.

With the development of high speed complementary bipolar IC processes in the 1980s (see Reference 6) it became possible to realize completely dc-coupled current feedback op amps using PNP and NPN transistors such as the Analog Devices' AD846, introduced in 1988 (Figure 1-15). Device matching and clever circuit design techniques give these modern IC CFB op amps excellent ac and dc performance without a requirement for separate level shifters, awkward supply voltages, or separate dc servo loops.

Various patents have been issued for these types of designs (see References 7 and 8, for example), but it should be remembered that the fundamental concepts were established decades earlier.

### **References: Op Amp Topologies**

- 1. Wyn Palmer, Barry Hilton, "A 500 V/μs 12-Bit Transimpedance Amplifier," **ISSCC Digest**, February 1987, pp. 176–177, 386.

- 2. Frederick E. Terman, "Feedback Amplifier Design," Electronics, January 1937, pp. 12–15, 50.

- 3. Edward L. Ginzton, "DC Amplifier Design Techniques," Electronics, March 1944, pp. 98–102.

- 4. Stewart E. Miller, "Sensitive DC Amplifier with AC Operation," **Electronics**, November 1941, pp. 27–31, 105–109.

- 5. J. O. Edson and H. H. Henning, "Broadband Codecs for an Experimental 224Mb/s PCM Terminal," Bell System Technical Journal, Vol. 44, No. 9, November 1965, pp. 1887–1950.

- 6. "Op Amps Combine Superb DC Precision and Fast Settling," **Analog Dialogue**, Vol. 22, No. 2, pp. 12–15.

- David A. Nelson, "Settling Time Reduction in Wide-Band Direct-Coupled Transistor Amplifiers," US Patent 4,502,020, Filed October 26, 1983, Issued February 26, 1985.

- 8. Royal A. Gosser, "DC-Coupled Transimpedance Amplifier," **US Patent 4,970,470**, Filed October 10, 1989, Issued November 13, 1990.

This page intentionally left blank

## SECTION 1-3

## **Op Amp Structures** Walt Kester, Walt Jung, James Bryant

This section describes op amps in terms of their *structures*, and Section 1-4 discusses op amp *specifications*. It is hard to decide which to discuss first, since discussion of specifications, to be useful, entails reference to structures, and discussion of structures likewise requires reference to the performance feature that they are intended to optimize.

Since the majority of readers will have at least some familiarity with operational amplifiers and their specifications, we shall discuss structures first, and assume that readers will have at least a first-order idea of the definitions of the various specifications. Where this assumption proves ill-founded, the reader should look ahead to the next section to verify any definitions required.

Because single-supply devices permeate practically all modern system designs, the related design issues are integrated into the following op amp structural discussions.

## Single-Supply Op Amp Issues

Over the last several years, single-supply operation has become an increasingly important requirement because of market demands. Automotive, set-top box, camera/camcorder, PC, and laptop computer applications are demanding IC vendors to supply an array of linear devices that operate on a single-supply rail, with the same performance of dual supply parts. Power consumption is now a key parameter for line or battery-operated systems, and in some instances, more important than cost. This makes low voltage/low supply current operation critical; at the same time, however, accuracy and precision requirements have forced IC manufacturers to meet the challenge of "doing more with less" in their amplifier designs.

In a single-supply application, the most immediate effect on the performance of an amplifier is the reduced input and output signal range. As a result of these lower input and output signal excursions, amplifier circuits become more sensitive to internal and external error sources. Precision amplifier offset voltages on the order of 0.1 mV are less than a 0.04 LSB error source in a 12-bit, 10 V full-scale system. In a single-supply system, however, a "rail-to-rail" precision amplifier with an offset voltage of 1 mV represents a 0.8 LSB error in a 5 V full-scale system (or 1.6 LSB for 2.5 V full-scale).

To keep battery current drain low, larger resistors are usually used around the op amp. Since the bias current flows through these larger resistors, they can generate offset errors equal to or greater than the amplifier's own offset voltage.

Gain accuracy in some low voltage single-supply devices is also reduced, so device selection needs careful consideration. Many amplifiers with ~120 dB open-loop gains typically operate on dual supplies—for example OP07 types. However, many single-supply/rail-to-rail amplifiers for precision applications typically have open-loop gains between 25,000 and 30,000 under light loading (>10 k $\Omega$ ). Selected devices, like the OP113/OP213/OP413 family, do have high open-loop gains (>120 dB), for use in demanding applications. Another example would be the AD855x chopper-stabilized op amp series.

Many trade-offs are possible in the design of a single-supply amplifier circuit—speed versus power, noise versus power, precision versus speed and power, and so forth. Even if the noise floor remains constant (highly unlikely), the signal-to-noise ratio will drop as the signal amplitude decreases.

Besides these limitations, many other design considerations that are otherwise minor issues in dual-supply amplifiers now become important. For example, signal-to-noise (SNR) performance degrades as a result of reduced signal swing. "Ground reference" is no longer a simple choice, as one reference voltage may work for some devices, but not others. Amplifier voltage noise increases as operating supply current drops, and bandwidth decreases. Achieving adequate bandwidth and required precision with a somewhat limited selection of amplifiers presents significant system design challenges in single-supply, low power applications.

Most circuit designers take "ground" reference for granted. Many analog circuits scale their input and output ranges about a ground reference. In dual-supply applications, a reference that splits the supplies (0 V) is very convenient, as there is equal supply headroom in each direction, and 0 V is generally the voltage on the low impedance ground plane.

In single-supply/rail-to-rail circuits, however, the ground reference can be chosen anywhere within the supply range of the circuit, since there is no standard to follow. The choice of ground reference depends on the type of signals processed and the amplifier characteristics. For example, choosing the negative rail as the ground reference may optimize the dynamic range of an op amp whose output is designed to swing to 0 V. On the other hand, the signal may require level shifting in order to be compatible with the input of other devices (such as ADCs) that are not designed to operate at 0 V input.

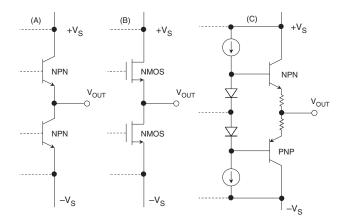

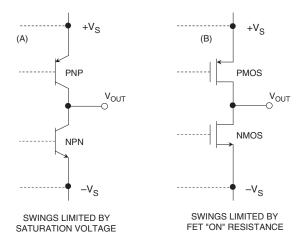

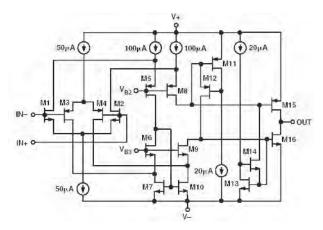

Very early single-supply "zero-in, zero-out" amplifiers were designed on bipolar processes, which optimized the performance of the NPN transistors. The PNP transistors were either lateral or substrate PNPs with much less bandwidth than the NPNs. Fully complementary processes are now required for the new breed of single-supply/rail-to-rail operational amplifiers. These new amplifier designs don't use lateral or substrate PNP transistors within the signal path, but incorporate parallel NPN and PNP input stages to accommodate input signal swings from ground to the positive supply rail. Furthermore, rail-to-rail output stages are designed with bipolar NPN and PNP common-emitter, or N-channel/P-channel common-source amplifiers whose collector-emitter saturation voltage or drain-source channel on resistance determine output signal swing as a function of the load current.

The characteristics of a single-supply amplifier input stage (common-mode rejection, input offset voltage and its temperature coefficient, and noise) are critical in precision, low voltage applications. Rail-rail input operational amplifiers must resolve small signals, whether their inputs are at ground, or in some cases near the amplifier's positive supply. Amplifiers having a minimum of 60 dB common-mode rejection over the entire input common-mode voltage range from 0 V to the positive supply are good candidates. It is not necessary that amplifiers maintain common-mode rejection for signals beyond the supply voltages. *But, what* is *required is that they do not self-destruct for momentary overvoltage conditions*. Furthermore, amplifiers that have offset voltages less than 1 mV and offset voltage drifts less than 2  $\mu$ V/°C are also very good candidates for precision applications. Since *input* signal dynamic range and SNR are equally if not more important than *output* dynamic range and SNR, precision single-supply/rail-to-rail operational amplifiers should have noise levels referred-to-input (RTI) less than 5  $\mu$ V p-p in the 0.1 Hz to 10 Hz band.

The need for rail-to-rail amplifier output stages is also driven by the need to maintain wide dynamic range in low supply voltage applications. A single-supply/rail-to-rail amplifier should have output voltage swings that are within at least 100 mV of either supply rail (under a nominal load). The output voltage swing is very dependent on output stage topology and load current.

Generally, the voltage swing of a good rail-to-rail output stage should maintain its rated swing for loads down to 10 k $\Omega$ . The smaller the V<sub>OL</sub> and the larger the V<sub>OH</sub>, the better. System parameters, such as "zero-scale" or "full-scale" output voltage, should be determined by an amplifier's V<sub>OL</sub> (for zero-scale) and V<sub>OH</sub> (for full-scale).

- Single Supply Offers:

- Lower Power

- Battery-Operated Portable Equipment

- Requires Only One Voltage

- Design Trade-Offs:

- Reduced Signal Swing Increases Sensitivity to Errors Caused by Offset Voltage, Bias Current, Finite Open-Loop Gain, Noise, etc.

- Must Usually Share Noisy Digital Supply

- Rail-to-Rail Input and Output Needed to Increase Signal Swing

- Precision Less than the best Dual Supply Op Amps but not Required for All Applications

- Many Op Amps Specified for Single Supply, but do not have Rail-to-Rail Inputs or Outputs

#### Figure 1-20: Single-supply op amp design issues

Since the majority of single-supply data acquisition systems require at least 12-to 14-bit performance, amplifiers which exhibit an open-loop gain greater than 30,000 for all loading conditions are good choices in precision applications. Single-supply op amp design issues are summarized in Figure 1-20.

## **Op Amp Input Stages**

It is extremely important to understand input and output structures of op amps in order to properly design the required interfaces. For ease of discussion, the two can be examined separately, as there is no particular reason to relate them at this point.

## **Bipolar Input Stages**

The very common and basic bipolar input stage of Figure 1-21 consists of a "long-tailed pair" built with bipolar transistors. It has a number of advantages: it is simple, has very low offset, the bias currents in the inverting and noninverting inputs are well-matched and do not vary greatly with temperature. In addition, minimizing the initial offset voltage of a bipolar op amp by laser trimming also minimizes its drift over temperature. This architecture was used in the very earliest monolithic op amps such as the  $\mu$ A709. It is also used with modern high speed types, like the AD829 and AD8021.

Although NPN bipolars are shown, the concept also applies with the use of PNP bipolars.

Figure 1-21: A bipolar transistor input stage

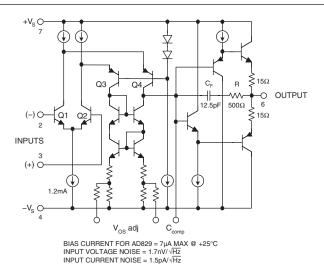

The AD829, introduced in 1990, is shown in Figure 1-22. This op amp uses a bipolar differential input stage, Q1–Q2, which drives a "folded cascode" gain stage which consists of a fast pair of PNP transistors, Q3–Q4 (see Reference 1). These PNPs drive a current mirror that provides the differential-to-single-ended conversion. The output stage is a two-stage complementary emitter follower.

The AD829 is a wideband video amplifier with a 750 MHz uncompensated gain-bandwidth product, and it operates on  $\pm 5$  V to  $\pm 15$  V supplies. For added flexibility, the AD829 provides access to the internal compensation node (C<sub>COMP</sub>). This allows the user to customize frequency response characteristics for a particular application where the closed-loop gain is less than 20. The RC network connected between the output and the high impedance node helps maintain stability, when driving capacitive loads.

Input bias current is 7  $\mu$ A maximum at 25°C, input voltage noise is 1.7 nV/ $\sqrt{Hz}$ , and input current noise is 1.5 pA/ $\sqrt{Hz}$ . Laser wafer trimming reduces the input offset voltage to 0.5 mV maximum for the "A" grade. Typical input offset voltage drift is 0.3  $\mu$ V/°C.

Figure 1-22: AD829 op amp simplified schematic

In an op amp input circuit such as Figure 1-22, the input bias current is the base current of the transistors comprising the long-tailed pair, Q1–Q2. It can be quite high, especially in high speed amplifiers, because the collector currents are high. It is typically ~3  $\mu$ A, for the AD829. In amplifiers where the bias current is *uncompensated* (as true in this case), the bias current will be equal to one-half of the Q1–Q2 emitter current, divided by the H<sub>FE</sub>.

The bias current of a simple bipolar input stage can be reduced by a couple of measures. One is by means of *bias current compensation*, to be described further below.

Another method of reducing bias current is by the use of *superbeta* transistors for Q1–Q2. Superbeta transistors are specially processed devices with a very narrow base region. They typically have a current gain of thousands or tens of thousands (rather than the more usual hundreds). Op amps with superbeta input stages have much lower bias currents, but they also have more limited frequency response.

Since the breakdown voltages of superbeta devices are quite low, they also require additional circuitry to protect the input stage from damage caused by overvoltage (for example, they wouldn't operate in the circuit of Figure 1-22).

Some examples of superbeta input bipolar op amps are the AD704/AD705/AD706 series, and the OP97/ OP297/OP497 series (single, dual, quad). These devices have typical 25°C bias currents of 100 pA or less.

## Bias Current Compensated Bipolar Input Stage

A simple bipolar input stage such as used in Figure 1-22 exhibits high bias current because the currents seen externally are in fact the base currents of the two input transistors.

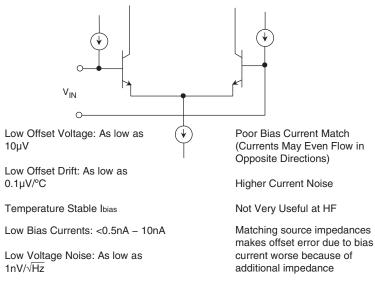

Figure 1-23: A bias current compensated bipolar input stage

By providing necessary bias currents via an internal current source, as in Figure 1-23, the only *external* current then flowing in the input terminals is the difference current between the base current and the current source, which can be quite small.

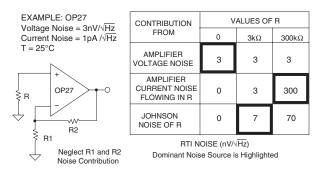

Most modern precision op amps use some means of internal bias current compensation; examples would be the familiar OP07 and OP27 series.

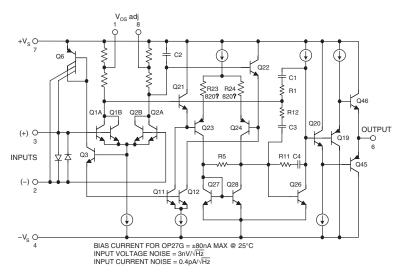

The well-known OP27 op amp family is good example of bias-compensated op amps (see References 2 and 3). The simplified schematic of the OP27, shown in Figure 1-24, shows that the multiple-collector transistor Q6 provides the bias current compensation for the input transistors Q1 and Q2. The "G" grade of the OP27

Figure 1-24: OP27 op amp uses bias current compensated input stage

has a maximum input bias current specification of ±80 nA at 25°C. Input voltage noise is 3 nV/ $\sqrt{\text{Hz}}$ , and input current noise 0.4 pA/ $\sqrt{\text{Hz}}$ . Offset voltage trimming by "Zener-zapping" reduces the input offset voltage of the OP27 to 50  $\mu$ V maximum at 25°C for the "E" grade device (see Reference 4 for details of this trim method).

Bias-current-compensated input stages have many of the good features of the simple bipolar input stage, namely: low voltage noise, low offset, and low drift. Additionally, they have low bias current which is fairly stable with temperature. However, their current noise is not very good, and their bias current matching is poor.

These latter two undesirable side effects result from the external bias current being the *difference* between the compensating current source and the input transistor base current. Both of these currents inevitably have noise. Since they are uncorrelated, the two noises add in a root-sum-of-squares fashion (even though the dc currents subtract).

Since the resulting external bias current is the difference between two nearly equal currents, there is no reason why the net current should have a defined polarity. As a result, the bias currents of a bias-compensated op amp may not only be mismatched, they can actually flow in opposite directions. In most applications this isn't important, but in some it can have unexpected effects. (For example, the droop of a sample-and-hold [SHA] built with a bias-compensated op amp may have either polarity.)

In many cases, the bias current compensation feature is not mentioned on an op amp data sheet, and a simplified schematic isn't supplied. It is easy to determine if bias current compensation is used by examining the bias current specification. If the bias current is specified as a " $\pm$ " value, the op amp is most likely compensated for bias current.

Note that this can easily be verified by examining the *offset current* specification (the difference in the bias currents). If internal bias current compensation exists, the offset current will be of the same magnitude as the bias current. Without bias current compensation, the offset current will generally be at least a factor of 10 smaller than the bias current. Note that these relationships generally hold, regardless of the exact magnitude of the bias currents.

It is also a well-known fact that, within an op amp application circuit, the effects of bias current on the output offset voltage of an op amp can often be cancelled by making the source resistances at the two inputs equal. However, there is an important caveat here. The validity of this practice holds true only for bipolar input op amps *without* bias current compensation; that is, where the input currents are well matched. In a case of an op amp using internal bias current compensation, adding an extra resistance to either input will usually make the output offset worse.

## Bias Current Compensated Superbeta Bipolar Input Stage

As mentioned above, the OP97/297/OP497-series are high performance superbeta op amps, that also use input bias current compensation. As a result, their input bias currents are  $\pm 150$  pA max at 25°C. Note that in this case the " $\pm$ " prefix to the bias current magnitude indicates that the amplifier uses internal bias current compensation.

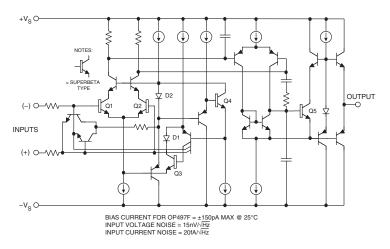

A simplified schematic of an OP97 (or one-quarter of the OP497) is shown in Figure 1-25. Note that the Q1–Q2 superbeta pair is protected against large destructive differential input voltages, by the use of both back-to-back diodes, and series current-limiting resistors. Note also that the Q1–Q2 superbeta pair is also protected against excessive collector voltage, by an elaborate bias and bootstrapping network.

As a result of these clamping and protection circuits, the input common-mode voltage of this op amp series can safely vary over the full range of the supply voltages used.

Figure 1-25: The OP97, OP297 and OP497 op amp series uses superbeta input stage transistors and bias current compensation

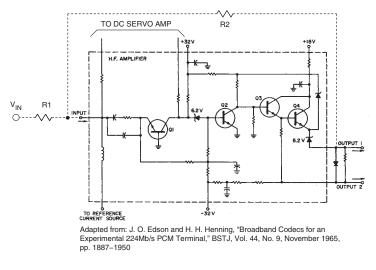

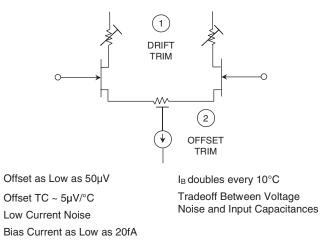

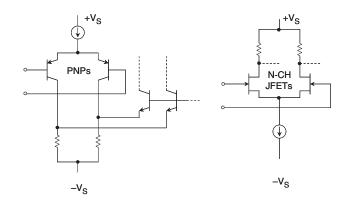

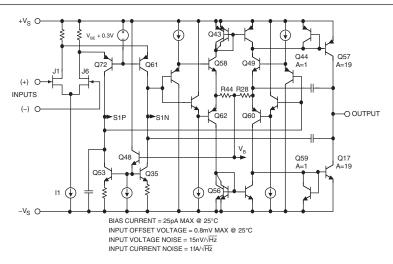

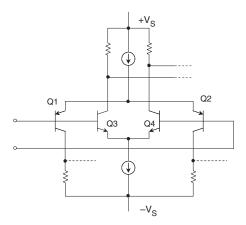

## FET Input Stages