# LM118 Op Amp Slews 70 V/μsec

National Semiconductor Linear Brief 17

One of the greatest limitations of today's monolithic op amps is speed. With unity gain frequency compensation, general purpose op amps have 1 MHz bandwidth and 0.3 Vµs slew rate. Optimized compensation as well as feed-forward compensation can improve op amp speed for some applications. Specialized devices such as fast, unity-gain buffers are available which provide partial solutions. This paper will describe a new high speed monolithic amplifier that offers an order of magnitude increase in speed with no loss in flexibility over general purpose devices.

The LM118 is constructed by the standard six mask monolithic process and features 15 MHz bandwidth and 70 V/ $\mu s$  slew rate. It operates over a  $\pm 5$  to  $\pm 18$ V supply range with little change in speed. Additionally, the device has internal unity-gain frequency compensation and needs no external components for operation. However, unlike other internally compensated amplifiers, external feedforward compensation may be added to approximately double the bandwidth and slew rate.

### **DESIGN CONCEPTS**

In general purpose amplifiers the unity-gain bandwidth is limited by the lateral PNP transistors used for level shifting. The response above 2 MHz is so poor that they cannot be used in a feedback amplifier. If the PNP transistors are used for level shifting only at DC or low frequencies and the signal is fed forward around the PNP transistors at high frequencies, wide bandwidth can be obtained without the excessive phase shift of the PNP transistors.

TL/H/6831-1

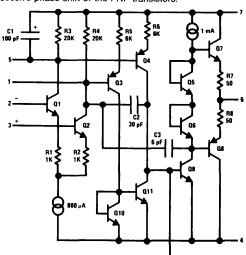

#### FIGURE 1. Simplified Circuit of the LM118

Figure 1 shows a simplified schematic of the LM118. Transistors  $Q_1$  and  $Q_2$  are a conventional differential input stage with emitter degeneration and resistive collector loads.  $Q_3$  and  $Q_4$  form the second stage which further amplify the signal and level shift the signal towards  $V^-$ . The collectors of  $Q_3$  and  $Q_4$  drive a current inverter,  $Q_{10}$  and  $Q_{11}$  to convert from differential to single ended.  $Q_9$ , which has a cur-

rent source load for high gain, drives a class B output. The collectors of the input stage and the base of  $Q_g$  are available for offset balancing and external compensation.

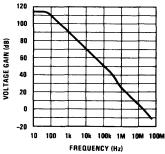

Frequency compensation is accomplished with three internal capacitors.  $C_1$  rolls off on half the differential input stage so that the high frequency signal path is single-ended. Also, at high frequencies, the signal is fed forward around the lateral PNP transistors by a 30 pF capacitor,  $C_2$ . This eliminates the excessive phase shift. Overall frequency response is then set by capacitor,  $C_3$ , which rolls off the amplifier at 6 dB/octave. As previously mentioned feedforward compensation for inverting applications can be applied to the base of  $Q_3$ . Figure 2 shows the open loop frequency response of an LM118. Table I gives typical specifications for the new amplifier.

TL/H/6831-2

FIGURE 2. Open Loop Voltage Gain as a Function of Frequency for LM118

TABLE I. Typical Specifications for the LM118

| Input Offset Voltage   | 2 mV    |

|------------------------|---------|

| Input Bias Current     | 200 nA  |

| Offset Current         | 20 nA   |

| Voltage Gain           | 200k    |

| Common Mode Range      | ± 11.5V |

| Output Voltage Swing   | ±13V    |

| Small Signal Bandwidth | 15 MHz  |

| Slew Rate              | 70 V/μs |

#### **OPERATING CONFIGURATION**

Although considerable effort was taken to make the LM118 trouble free, high frequency amplifiers are more prone to oscillations than low frequency devices such as the LM101A. Care must be taken to minimize the stray capacitance at the inverting input and at the output; however the LM118 will drive a 100 pF load. Good power supply bypassing is also in order—0.1  $\mu F$  disc ceramic capacitors should be used within a few inches of the amplifier. Additionally, a small capacitor is usually necessary across the feedback resistor to compensate for unavoidable stray capacitance.

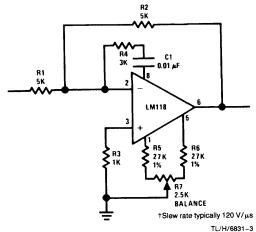

Figure 3 shows feedforward compensation of the LM118 for fast inverting applications. The signal is fed from the summing junction to the output stage driver by  $C_1$  and  $R_4$ . Re-

sistors R<sub>5</sub>, R<sub>6</sub> and R<sub>7</sub> have two purposes: they increase the internal operating current of the output stage to increase slew rate and they provide offset balancing. The current boost is necessary to drive internal stray capacitance at the higher slew rate. Mismatch of the external resistors can cause large voltage offsets so offset balancing is necessary. For supply voltages other than  $\pm\,15\text{V}$ , R<sub>5</sub> and R<sub>6</sub> should be selected to draw about 500  $\mu\text{A}$  from Pins 1 and 5.

FIGURE 3. Feedforward Compensation for Greater Inverting Slew Rate†

When using feedforward resistor  $R_4$  should be optimized for the application. It is necessary to have about 8  $k\Omega$  in the path from the output of the amplifier through the feedback resistor and through feedforward network to Pin 8 of the device. The series resistance is needed to limit the bandwidth and prevent minor loop oscillation.

At high gains, or with high value feedback resistors  $R_4$  can be quite low—but not less than  $100\Omega.$  When the LM118 is used as a fast integrator, with a large feedback capacitor or with low values of feedback resistance,  $R_4$  must be increased to 8 k $\Omega$  to insure stability over a full  $-55^{\circ}\mathrm{C}$  to  $+125^{\circ}\mathrm{C}$  temperature range.

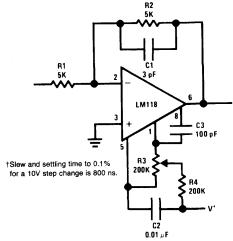

One of the more important considerations for a high speed amplifier is settling time. Poor settling time can cancel the advantages of having high slew rate and bandwidth. For example—an amplifier can have severe ringing after a step input. A relatively long time is then needed before the output voltage can be read accurately. Settling time is the time necessary for the output to slew through a defined voltage change and settle to within a defined error of its final output voltage. Figure 4 shows optimized compensation for settling

TL/H/6831-4

## FIGURE 4. Compensation for Minimum Settling† Time

to within 0.1% error. Typically the settling time is 800 ns for a simple inverter circuit as shown. Settling time is, of course, subject to operating conditions external to the IC such as closed loop gain, circuit layout, stray capacitance and source resistance. An optional offset balancing circuit,  $\rm R_3$  and  $\rm R_4$  is included.

The LM118 opens up new fields for IC operational amplifiers. It is more than an order of magnitude faster than general purpose amplifiers while retaining the ease of use features. It is ideally suited for analog to digital converters, active filters, sample and hold circuits and wide band amplification. Further, the LM118 has the same pin configuration as the LM101A or LM741 and is interchangeable with these devices when speed is of prime concern.