## Set 30: Non-linear circuits—r.m.s./log/ power laws

Familiar mathematical functions-squares, square roots (page 136), cube law, r.m.s. conversion, resolvers, logarithms, frequency doubling (page 132)-are implemented in this set using a variety of techniques, including the use of the integrated multiplier (pages 135 & 140) introduced in set 29. No pretences at high precision are made in these circuits. Typically linearity is 1 or 2%, but as the following article points out errors often vary over the dynamic range because of the non-linear nature of the circuits. Manufacturers should be consulted directly over particular solutions to problems requiring greater precision. On page 135 the output from the precision rectifier is now correctly shown as being taken from the junction of the R<sub>1</sub>-diode series combination. And in connection with Barie Gilbert's circuits, there were two additional brackets needed to enclose the last two terms in the expressions for  $I_A$  and  $I_B$ .

Background article 130 Root-law array 132 Voltage divider 133 Ramp to sinewave converter 134 R.m.s. to d.c. converter 135 D-type  $\Delta\Sigma$  converter 136 Cube-law generator 137 Logarithmic amplifier 138 Resolvers 139 Uses of i.c. multipliers 140 Computation of  $(x^2+y^2)^{\dagger}$  141 Up-date circuits 142

# Introducing non-linear circuits

Logarithmic, power and r.m.s. laws

A growing need for a variety of mathematical function generations has led to a variety of circuit solutions. The problems range from the use of resolvers in servo systems in which sine/cosine function generation is needed, to the measurement of the true r.m.s. value of non-sinusoidal waveforms.

If we restrict ourselves to one or two variables, then Fig. 1 shows a sample of the functions that might occur in practical systems - either because the output of a system is required in some particular form such as a decibel representation of a voltage gain, or to correct for some non-linear property of a transducer. Few of these functions can be obtained directly from existing devices and circuits unless limited accuracy is acceptable. For example, the field-effect transistor has a squarelaw term in its  $I_D/V_{GS}$  characteristic and this has been exploited to provide such functions as  $X_2$  and XY.

However, the circuits have been fairly complex, have resulted in significant departure from the ideal law or have drifted badly with change in temperature and/or supply.

Some of these functions can be obtained by indirect means such as the parametric techniques of Hall-effect devices or varactor diodes. Others can be obtained via modulation processes as in the multiplier/divider circuits of Circards Set 29. The most valuable tool available to the designer in this area is the transistor, not because of its amplifying properties, but because the  $I_C/V_{be}$  characteristic follows a particular non-linear law precisely and over a wide range of currents.

In its simplest form that law can be written as:  $I_{\rm C} = k \exp V_{\rm be}$ . This hides a number of inconvenient factors such as its dependence on temperature, but is an accurate representation of the shape of the characteristic. As indicated in the previous article this is the basis of logarithmic amplifiers in which the output voltage is a logarithmic function of the input voltage.

From the basic properties of logarithms various power-law operations can be implemented.

| one variable                                             | two variables                                                                                                                   |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{c}                                     $ | $ \begin{array}{c}     XY \\     \frac{X}{Y} \\     \frac{X^2}{Y} \\     \sqrt{X^2 + Y^2} \\     \sqrt{X^2 - Y^2} \end{array} $ |

Fig. 1. Common functions that can be obtained by passing X, Y through circuits with corresponding transfer functions.

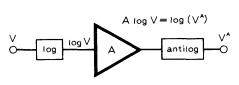

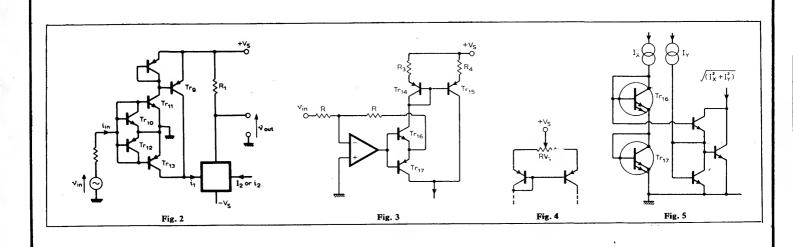

Fig. 2. Logarithmic circuits are based on natural logarithms rather than  $\log_{10}$ because of the way diode / transistor characteristics are expressed.

feedback / feedforward.

| Let $V_a = K \log_e V_1$ and $V_b = K \log_e$             | $V_2$ . |

|-----------------------------------------------------------|---------|

| Then $V_a + V_b = K \log_e (V_1 V_2)$                     | 1       |

| $V_{a} - V_{b} = K \log_{e} (V_{1} / V_{2})$              | 2       |

| $n\tilde{V}_{a} = nK\log_{e}V_{1} = K\log_{e}(V_{1}^{n})$ | 3       |

Thus adding, subtracting or amplifying the input variables all of which are within the scope of normal linear circuit design, result in outputs that involve the product, ratio or powers of those variables. The remaining problem is that the output is still a logarithmic function; if it is succeeded by an antilog circuit then the process is completed. A typical configuration is shown in Fig. 2.

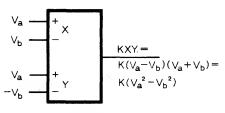

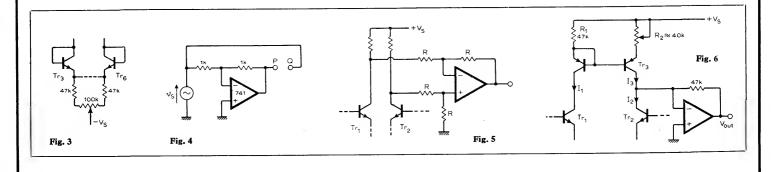

A second family of circuits makes use of existing functional blocks such as the multiplier (XY) or the multiplier/divider (XY/Z). Using various feedback and feedforward configurations, a number of the other functions such as square, square root and division can be performed. As an example, consider the circuit of Fig. 3. It illustrates how complex functions can be built up piecemeal. With care and ingenuity elegant and efficient solutions to such problems can be found using various interconnections to remove the need for additional functional blocks.

A group of four transistors in which the base-emitter voltages have a relationship of the form  $V_1 + V_2 = V_3 + V_4$ must result in a corresponding collector current relationship  $I_1I_2 = I_3I_4$  once the log characteristics are taken account of (see previous article). This leads directly to the implementation of a multiplier by making, say, I<sub>2</sub> constant and forcing I<sub>3</sub>, I. to be proportional to the two input variables. Other interconnections of these transistors can yield functions such as square, vector sum, and division.

Some novel solutions demand devices not readily available to the average user – devices developed by manufacturers for use in their own instruments.

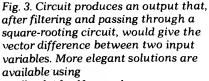

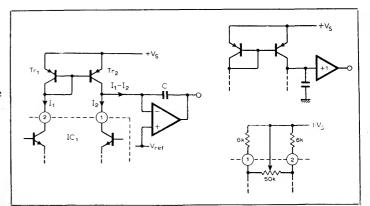

One such that shows an old idea brought very firmly up-to-date is given in Fig. 4. It uses what is effectively a balanced bridge to determine the true r.m.s. value of an input voltage. If two identical transistors are separately heated by equal resistors then they will remain in balance only if the flow of

heat to each is equal. Any unbalance is amplified by the operational amplifier forcing the direct output voltage to deliver the same power to the righthand resistor as the input delivers to the other. Hence the r.m.s. values of the two voltages are equal. A neat idea, though one that requires a very carefully constructed chip if the sensing transistors are each to respond to only one of the heat sources.

A severe problem in many of these ideas is that of identifying and neutralizing the error sources. Because of the non-linear equations involved, the relative errors are different at all parts Fig. 4. Two identical transistors are heated separately by resistors supplied from an unknown input voltage and the output of an op-amp. High gain forces the transistors into balance by increasing  $V_0$  until the power it supplies matches that delivered by  $V_{r.m.s.}$

of the range. Manufacturers of modules and i.cs directed at these applications devote a great deal of effort to this topic, and readers would be well-advised to consult them if high-precision functions are needed. 131

# Set 30: R.m.s./log/power laws—1

## **Root-law array**

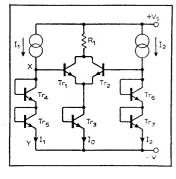

Typical data Tr<sub>1</sub>-Tr<sub>3</sub> 3/5 of CA3086 Tr<sub>4</sub>-Tr<sub>7</sub> 4/5 of CA3086 V<sub>S</sub>  $\pm$ 5V R<sub>1</sub> 33k $\Omega$ For graphs, currents I<sub>1</sub> and I<sub>2</sub> are derived from calibrated current sources.  $I_0 = \sqrt{I_1^2 + I_2^2}$ . Percentage error shown in graphs.

This circuit is a special case of a

general root law circuit<sup>1</sup>, using

bipolar transistor-array

relationship which exists

current gain a=1, then

the thermal potential. As

packages. The performance

and the  $V_{BE}$  of a transistor.

depends on the fairly precise

between the collector current Ic

Assuming that the common-base

$I_{\rm C} = k \exp V_{\rm BE} / V \varphi$ , where  $\nabla \varphi$  is

$V_{\rm BE} = V\varphi \log I_{\rm C}/k$ , then in the

because there are two diodes in

series. There is only one diode

path XY,  $V_{\rm X} = 2V\varphi \log I_1/k$

in the Tr<sub>3</sub> path and hence

written in terms of the

base-emitter voltage of

Tr<sub>1</sub>, giving

where *m* is the

$V_{\rm E} = V \varphi \log I_{\rm O}/k$ . I<sub>O</sub> can be

$I_0 = k \sum \exp((V_{\rm X} - V_{\rm E})/V\varphi)$

number of paths like XY.

**Circuit description**

Hence by substituting for  $V_{\rm X}/V\varphi$  and  $V_{\rm E}/V\varphi$

$$I_{O} = \sum_{1}^{m} k (I_{1}/k)^{2} \cdot (k/I_{O})$$

=  $\sum_{1}^{m} I_{1}^{2}/I_{O}$

giving  $I_{O} = \left[\sum_{1}^{m} (I_{1})^{2}\right]^{\dagger}$ . Above,

m=2,  $I_1=I_2$  and  $I_0=(I_1^2+I_2^2)^{\ddagger}$ . Current flow directions of  $I_1$  and  $I_2$  should be as shown. If these currents are to be derived from an alternating voltage source, then circuits must be provided to ensure the above polarities are maintained.

#### **Circuit modifications**

• The circuit has been used as a frequency doubler<sup>2</sup> dependent on a similar mathematical relationship, and in this case, a sinusoidal input voltage drives current into the circuit of Fig. 2 to obtain unidirectional current flow, which is independent of the load. Current  $i_1$  is drawn from the current mirror Tr<sub>8</sub>, Tr<sub>9</sub> in the same direction no matter the polarity of iin. When iin is positive-going, the current mirror comprising transistors Tr<sub>10</sub> and Tr<sub>11</sub> is active, and the resulting collector current of Tr<sub>11</sub> is mirrored by Tr<sub>8</sub>, Tr<sub>9</sub>. When therefore iin is negativegoing, an equivalent current is delivered by current mirror Tr<sub>12</sub>, Tr<sub>13</sub>. P-n-p transistors are required for those current mirrors and are obtained in the

CA3084 i.c. A voltage output is available via  $R_1$ .

• An alternative arrangement for obtaining unidirectional current is shown in Fig. 3 using an inverting amplifier, and a complementary pair in the feedback loop. This avoids the crossover distortion that may exist in the Fig. 1 arrangement due to the finite  $V_{BE}$  drops of transistors Tr<sub>10</sub>, Tr<sub>12</sub>, though if  $v_{in} \ge 0.6V$  this effect might be acceptable. The resistors R<sub>3</sub> and R4 must be closely matched to optimise the current mirror action.  $RV_1$  of Fig. 4 replaces  $R_3$ ,  $R_4$  and allows an alternative manual adjustment to match the collector currents.

• Another arrangement using the translinear multiplier<sup>4</sup> concept is shown in Fig. 5. While this may be a configuration more likely met in a i.c. multiplier, transistor-array packages could be used, with  $Tr_{16}$ ,  $Tr_{17}$  being implemented by paralleling transistors.

#### Further reading

- 1 Barker, R. W. J. and Hart, B. L., *Electronics Letters* vol. 10, 1974, pp. 439/40.

- 2 Barker, R. W. J., *Electronics* Letters vol. 11, 1975, pp. 106/7.

- 3 Barker, R. W. J. and Hart, B. L. *Journal of Physics E.* vol. 8, 1975, pp. 721/2.

- 4 Gilbert, B. *Electronics Letters* vol. 11, 1975, pp. 14-6.

Related circuits

Set 30, cards 10, 5.

#### Typical performance

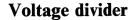

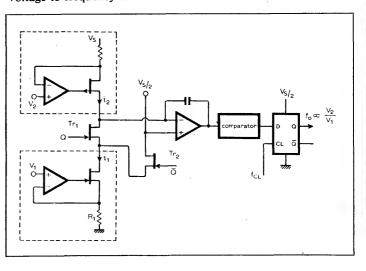

IC<sub>1</sub> 741 op-amp  $\pm$ 7.5V supplies IC<sub>2</sub>  $\frac{1}{2}$  of CD4013, D-type flip-flop IC<sub>3</sub>  $\frac{1}{4}$  of CD4016 f.e.t. switch V<sub>DD</sub> +7.5V, V<sub>SS</sub> -7.5V Clock pulses 3V pk-pk square wave, mean value zero, frequency 10kHz. V<sub>2</sub> -7.5V, V<sub>1</sub> positive R<sub>2</sub> 1M $\Omega$ , R<sub>1</sub> 100k $\Omega$ C 2.2nF

**Circuit description**

Voltage  $V_2$  is a negative voltage which will cause the integrator  $IC_1$  to ramp positively. The slope of this is slow since  $R_2$  is large. When  $I_1$  is permitted to flow to the summing junction (f.e.t. switch of  $IC_3$  closed), the op-amp will ramp downwards provided  $I_1 > I_2$ . In ramping downwards  $V_0$  will go below the threshold level of the D-type flip-flop  $IC_2$  and on the occurrence of the next negative going edge of the clock Q will go low, the switch will open;

I<sub>1</sub> is thus cut-off and the op-amp will begin to ramp positively again. This will continue until D is high on the trailing edge of a clock pulse when I<sub>1</sub> will again be switched in. The trace above shows a typical V<sub>0</sub> (IC<sub>1</sub> output). The lower level of this waveform varied somewhat (from -2V for a large V<sub>1</sub> to -0.25V for a small V<sub>1</sub>). The slope of the positive ramp is, of course, constant for constant V<sub>2</sub> but as V<sub>1</sub> is varied the negative-going slope varies.

Clearly in a complete period T the charge put in by  $V_2$  is cancelled by the charge withdrawn by  $V_1$  as the starting and finishing voltages are the same.

e.

$$I_2T = I_1 T'$$

$\frac{1}{T} = \frac{I_2}{I_1 T'} = \frac{V_2 R_1}{V_1 R_2} \frac{1}{T'}$

e.  $f_0 = \frac{V_2 R_1}{R_2} f_{CL} \frac{1}{V_1}$

Hence, if  $R_1$ ,  $R_2$ , and the clock frequency are constant we obtain a frequency proportional to  $V_2/V_1$ .

We fixed  $V_2$  at -7.5V for convenience and varied  $V_1$ . For  $V_1$  in the range 1.5V to 6.5V the frequency  $f_0$  varied from 865Hz to 3472Hz, the product  $V_1 f_0$  remaining constant within 0.2% proving the division to be accurate.

Note that T' need not be one clock period as shown but will be an integral multiple of the clock period. Furthermore, in our description we have implied that the switching level of the D-type flip-flop is zero volts and this need not be so.

#### **Component changes**

With the values of  $R_1$  and  $R_2$ quoted, C, which does not appear in the expression for  $f_0$ , can be varied over a range of about 10:1. Low values of C cause saturation of IC<sub>1</sub> before the flip-flop changes state and high values caused what appeared like subharmonic locking of some sort. This might have been obviated by use of a lower clock frequency.

Changing  $R_1$  to  $10k\Omega$ ,  $R_2$  to  $1M\Omega$  and C to 22nF made little difference to the results. One would expect  $R_2$  max to be of the order of  $1M\Omega$  to prevent

op amp input currents affecting the operation although since this is a constant effect it should not seriously affect the frequency of oscillation. The lower limit to  $R_1$  is set by the fact that the on resistance of the f.e.t. switch is approximately  $300\Omega$  i.e.  $R_1 \ge 300\Omega$ .

The max.  $V_2$  is not seriously limited but  $V_1$  is limited to be less than  $V_{DD}$ —the positive supply of the c.m.o.s. f.e.t. switch IC<sub>3</sub>.

#### Circuit modifications

• In essence we have been supplying voltage-controlled currents  $I_2$  and  $I_1$  to the integrator. There are several ways of doing this (e.g. ref. 1). One method is as shown below in which the two dotted sections are accurate voltage to current converters, i1 for example being  $V_1/R_1$ . This circuit is very similar to the one shown above with the addition of an inessential comparator but has the disadvantage that V<sub>2</sub> is referred to V<sub>s</sub>. This can be modified so that V<sub>2</sub> is referred to ground (refs 2, 3).

Note that  $f_0$  is proportional to the ratio of two voltages, the numerator one in our case being fixed. Many v-f converters operate on the same principle but keep the denominator term fixed. Such v-f converters therefore can be converted to act as divider circuits. In fact the circuit shown above is identical to the delta-sigma voltage-to-frequency converter on card 3, set 21.

• Another such v-f converter is the simple unijunction v-f converter (card 1, set 21).

Many multipliers require not only the two voltages to be multiplied but a reference voltage which appears in the denominator of the output voltage expression e.g. set 29, card 4.

#### References

- 1 Set 6, Constant-current circuits, card 1.

- 2 Ljung, E. Accurate wide range analog multiplier, *Electronic Engineering*, July 1975.

- 3 Alusten, B. and Ljung, E. Accurate voltage dividing circuit, *Int. J. Electronics*, vol. 39, pp. 353-6, 1975.

Related circuits Set 21, card 3 Set 29, card 4

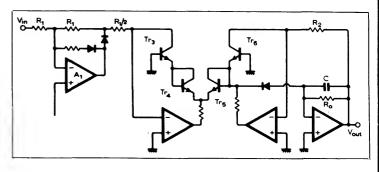

#### Ramp to sinewave converter

#### **Typical** data

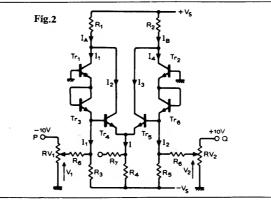

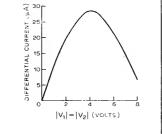

Tr<sub>1</sub>, Tr<sub>2</sub> 2/5 of CA3086 Tr<sub>3</sub>-Tr<sub>6</sub> 4/5 of CA3086 Vs  $\pm 10V$ R<sub>1</sub>, R<sub>2</sub> 47k $\Omega$ , R<sub>3</sub>-R<sub>8</sub> 100k $\Omega$ RV<sub>1</sub>, RV<sub>2</sub> 10k $\Omega$ Above values are chosen to simulate the current-source relationships indicated in Fig. 1 and provide the d.c. characteristic shown in the graph

#### **Circuit description**

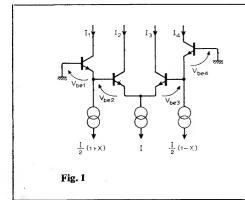

The circuit is based on the translinear circuit of Fig. 1. Currents *I*, (1+X)I/2, (1-X)I/2, are controlled current sources, and the values are chosen to have a specific relationship. It is assumed that all the transistors are matched  $(Tr_1, Tr_2 \text{ must be on the same chip, and also <math>Tr_3-Tr_6$ ). Summation of the base-emitter voltages in Fig. 1 gives

$V_{\rm BE_1} + V_{\rm BE_2} - V_{\rm BE_3} - V_{\rm BE_4} = 0.$

Because the collector currents are of the form  $I_C = I_S \exp qV_{\text{BE}/kT}$  then by substitution

$$(kT/q) \times \begin{bmatrix} \log I_1 + \log I_2 - \log I_3 - \log I_4 \\ I_5 - \log I_5 - \log I_5 \end{bmatrix} = 0$$

and hence  $I_1 I_2 = I_3 I_4$ . Hence any one current can be chosen to be a dependent output current. In Fig. 2, an extra diode in each branch means an additional V<sub>BE</sub> drop must be considered, and the current relationship is then

$$I_1^2 I_2 = I_3 I_4$$

With  $I_1 = (1 + X)I/2$ ,  $I = I_2 + I_3$ ,  $I_4 = (1 - X)I/2$  it is easily shown that

$$I_{A} = I_{1} + I/[(I_{1}/I_{4})^{2} + 1]$$

and  $I_{B} = I_{4} + I/[(I_{4}/I_{1})^{2} + 1]$ .

Hence the differential current

$$I_{\rm A} - I_{\rm B} = I X \frac{(1 - X^2)}{(1 + X^2)}$$

With -1 < X < 1, this difference-current is claimed to approximate a sine function within  $\pm 0.4\%$  full-scale. Over the range of control voltages used above ( $V_1 = V_2 = 0$  to 10V) the differential current is acceptably sinusoidal over half the range.

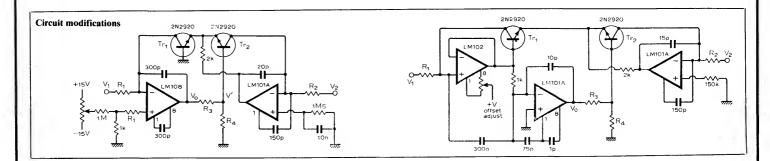

#### Circuit modifications

• Fig 3 permits zero-setting of the differential current when factor X=0.

• If terminals P and Q of Fig. 2 are driven from a ramp-function generator, via an inverting amplifier, then opposing ramp control voltages will produce a sinusoidal output in accordance with the first half of the graph over. The ramp inputs must be such a level to reach the point of inflexion of the curve, in this case about 4V.

• To obtain a single-ended voltage output from a differential current-input, a subtracting circuit such as Fig. 5 can be used, but in this case, matching of resistors R is necessary.

• An alternative differential current-to-voltage converter is achieved using the current

mirror of Fig. 6. Resistor R<sub>2</sub> must be trimmed to optimise current-mirror action. If balancing is such that  $I_1 = I_2$ , then for zero voltage output, I<sub>3</sub> must equal I<sub>1</sub>. Typical performance of this circuit provides a symmetrical 5.8V pk-pk cisoidal output for a 4V drive ramp signal. Maximum frequency 3.5kHz, when slight peak distortion may be encountered. Harmonic distortion is in fact quite small. Figures are quoted for a 1kHz drive signal

| ve a | signai. |     |       |

|------|---------|-----|-------|

| 2nd  | harmon  | ic  | -45dB |

| 3rd  | harmon  | ic  | -43dB |

| 4th  | harmon  | ic  | -70dB |

|      | 1       | • . | (E.ID |

Gilbert, B. Translinear circuits: a proposed classification, *Electronics Letters*, vol 11, pp. 14-6. Errata to above: *Electronics Letters*, vol. 11, p. 136.

Related circuit Set 29, card 8.

134

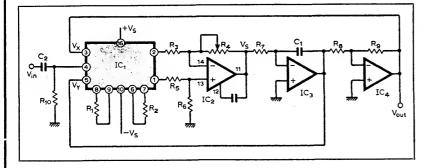

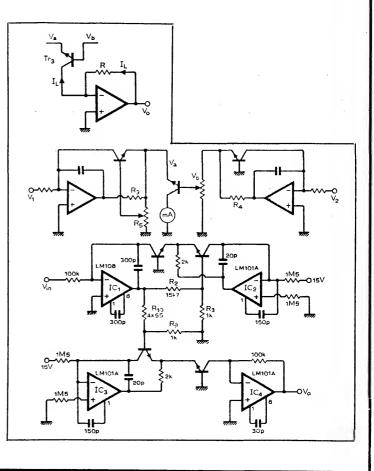

# Set 30: R.m.s./log/power laws---4

### r.m.s. to d.c. converter

Typical data IC<sub>1</sub> XR2308 V<sub>8</sub>  $\pm 10V$ IC<sub>2</sub> (included in IC<sub>1</sub>) IC<sub>3</sub>, IC<sub>4</sub> SN741, R<sub>10</sub>, R<sub>7</sub> 47k $\Omega$ R<sub>1</sub>, R<sub>2</sub>22k $\Omega$ , R<sub>8</sub>, R<sub>9</sub>10k $\Omega \pm 0.1\%$ R<sub>3</sub>, R<sub>5</sub> 56k $\Omega$ , R<sub>6</sub> 100k $\Omega$ R<sub>4</sub> 100k $\Omega$  potentiometer V<sub>in</sub> 1-5V r.m.s. C<sub>1</sub>, C<sub>2</sub> 1 $\mu$ F frequency 1kHz V<sub>out</sub>1-5V d.c.

#### Circuit description

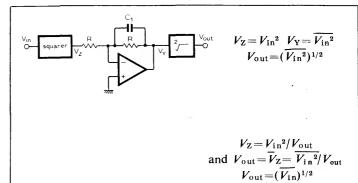

This circuit is based on an approach implemented in ref. 1. via an argument based on the explicit (Fig. 1) and implicit methods of establishing the r.m.s. value of a signal (Fig. 2). Notice that the squarer divider would require a device that would give an XY/Z output for X, Y, Z inputs (type AD433J). In each case, the integrator filters the fluctuating d.c. signal. The arrangement above is based on a i.c. multiplier. IC<sub>2</sub> is connected as a subtractor to provide a single-ended output from the differential output currents of the multiplier section of the i.c. This is then proportional to the product  $(V_{\rm in}-V_{\rm out})$   $(V_{\rm in}+V_{\rm out})$  i.e.  $(V_{\rm in}^2 - V_{\rm out}^2)$ . Under steady-state conditions, the d.c. feedback via  $V_x$  and  $V_y$  will force the mean value of this voltage, Vs, to be zero, any a.c. components being filtered by IC<sub>3</sub>. Hence  $V_{\text{out}} = (\overline{V_{\text{in}}^2})^{1/2}$ Initial setting up of the circuit to obtain the output equal to the input requires adjustment of R<sub>4</sub> which may shift the output zero level for  $V_{in} = 0$ . Zero adjustment is obtained via the circuit of Fig. 3, though further adjustment of R4 may be necessary, etc. The inverting-gain amplifier must be precisely -1, either by trimming or using accurate values of R<sub>8</sub>, R<sub>9</sub>.

#### **Circuit modifications**

• If pins 1 and 2, 3 and 5 are reversed, a negative d.c. output can be obtained without loss of accuracy.

• If terminals 1 and 2 (see Fig. 4)

are connected to a current mirror comprising transistors  $Tr_1$  and  $Tr_2$ , then the integrator may be driven directly without using the internal op amp, or this may be used as the integrator. The reference potential of the non-inverting input cannot be grounded, it must be maintained fairly positive to ensure it's within the range of potential of terminal 1.

• Another possibility is shown in Fig. 5, where because the current mirror is a current source, the capacitor can be connected directly and the output derived from a unity gain non-inverting amplifier. Fig. 6 (ref. 2) is an example of the implicit method of conversion, where A1 amplifier is arranged as an absolute rectifying circuit and transistors  $Tr_3$ - $Tr_6$  form a transconductance multiplier. To implement the circuit it is essential to optimise the frequency response and compensate for the limitations of the op-amps and transistors and some design guidance is given in the reference.

Further Reading Gilbert, B. RMS-DC Conversion, *Electronic Letters*, vol. 11, 1975, p.181. Handler, H. True r.m.s. voltage conversion, *Electronic Design*, vol. 4, 1974, pp. 66-72. Related circuits

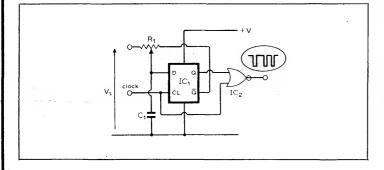

## D-type delta-sigma converter

#### **Typical performance**

IC 1 of CD4013AE IC<sub>2</sub> 1 of CD4001AE Supply +10VR<sub>1</sub>  $100k\Omega$  pot 10nF  $C_1$ Clock freq. 100kHz 0-10V  $V_i$  $\infty V_i$ fo  $\frac{f_{\rm o}}{f_{\rm clock}} \approx \frac{V_{\rm i}}{V_{\rm S}}$ Note

#### **Circuit description**

The delta-sigma modulator is a powerful tool in the processing of signals. Conceptually it requires a number of different sections: a D-type flip-flop, an analogue gate, a reference voltage, a comparator, an integrator. Previous designs have combined the functions of gate, reference and comparator into the flip-flop itself, using the facts that (i) the threshold level of the flip-flop is sharply defined, obviating the need for a comparator in simple applications (ii) the gate/ reference section is only required to define the feedback during the pulse on-state. This is achieved for a stable supply voltage by direct feedback from the Q output since c.m.o.s. outputs switch virtually to supply levels.

This leaves the op-amp integrator as the only analogue element in the system. If the feedback is taken from the Q output to the D-input with a capacitor to ground then a virtual-earth action is achieved without the need for an operational amplifier. This remarkable simplification has one drawback-the virtual earth has an offset voltage equal to the threshold voltage of the D-type flip-flop. This varies from device to device but is (i) a relatively fixed fraction of the supply (ii) varies little with temperature. Without any precautions, and setting  $R_1$

to its centre value, the output pulse rate has an average value that is a linear function of V<sub>i</sub> (typically to much better than 1%). It is possible to remove the offset by the configuration shown. If the clock pulse together with the Q output is fed to a NOR gate, then when the input voltage is low the D-input will tend to drop. Once below the threshold the clock pulses keep  $\bar{\mathbf{O}}$  high raising the D-input again. The Q output will need to be high most of the time. This implies that Q is only high occasionally and few pulses are obtained at the output-a direct representation of the low input voltage assumed. Set Vi to zero and adjust  $R_1$  until the output pulses are just barely inhibited. The setting is generally close to the centre-tap because the threshold is around V/2. This zero-setting varies the slope of the characteristic so that sensitivity controls must be adjusted after zero-setting. **Circuit modifications**

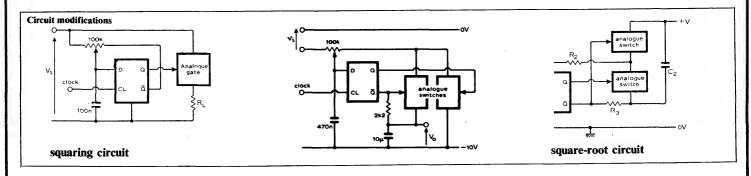

• The basic circuit is a tool that can be used to implement square, square-root and multiplier functions.

• Squaring circuit. The flip-flop is set up for  $f_0 = kV_1$  as above.  $V_1$  is also applied via an analogue gate to the load. Hence the mean load voltage is proportional to  $(V_1)^2$ —the voltage of magnitude  $V_1$  is applied to the load for a fraction of the time proportional to  $V_1$ . In this mode the output pulses are not used directly and the NOR gate is not needed unless transmission of the original variable  $V_1$  in serial form is desired.

• Square root circuit. This is achieved by the implicit method.

Q,  $\bar{Q}$  gate the analogue switches, but R<sub>3</sub> C<sub>2</sub> smooth the  $\bar{Q}$  output so it is the mean value at  $\bar{Q}$  that is gated. Hence the mean voltage applied to R<sub>2</sub> is a function of the square of the mean output. If the input is applied with respect to ground the output is obtained from  $\bar{Q}$  to the negative line. (The smoothed version across C<sub>2</sub> can be used directly if a high resistance is used).

$V_{\rm o} \propto \sqrt{V_{\rm i}}.$

• If positive supply/input operation is desired the gating is reversed and the output taken with respect to the positive rail.

• If the output is required as a pulse train, simply gate  $\bar{Q}$  and the clock pulses with a NOR gate and the output pulse rate is proportional to  $\sqrt{V_1}$ . When the initial zeroing has been correctly carried out, the square and square-root laws are followed with errors of <1% of full-scale. As noted earlier the scaling factor is affected by the zero-setting.

Related circuits Set 30, cards 1, 10 Set 29, card 3

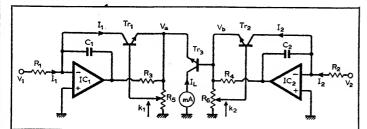

## **Cube-law generator**

#### Components

$\begin{array}{rrrr} R_{1}, \bar{R}_{2} & 10 k \varOmega \\ R_{3}, R_{4} & 220 \varOmega \\ R_{5}, R_{6} & 1 k \varOmega \\ C_{1} & 100 \mathrm{pF}, C_{2} & 1 \mathrm{nF} \end{array}$

#### Performance

With  $V_1$  at 10V,  $V_2$  was adjusted so that  $I_L=1$ mA, achieved with  $V_2=8.65$ V.  $V_1$ was then varied and produced the graph of  $I_L$  versus  $V_1^3$  shown.

#### **Circuit description**

In the following equations the subscripts 1, 2, 3 refer to transistors  $Tr_1$ ,  $Tr_2$  and  $Tr_3$  respectively

$V_{be_1} = k_1 V_a - V_a = (k_1 - 1) V_a$   $\therefore V_a = -V_{be}/(1 - k_1)$ Similarly  $V_b = -V_{be_2}/(1 - k_2)$ . Writing  $1/(1 - k_1)$  as *n* and  $1(1 - k_3)$  as *m* one obtains  $V_{be_3} = V_b - V_a = nV_{be_1} - mV_{be_2}$ In general  $V_{be} = (kT/q) \log I/I_a$ , which results in

$$I_{\rm L} = I_{\rm S} \; \frac{V_1^{\,n}}{V_2^{\,m}} \; \frac{R_2^{\,m}}{R_1^{\,n}} \; \frac{1}{I_{\rm S}^{\,n}}$$

As Is is temperature dependent one can achieve some temperature compensation by maintaining (n-m)=1. Temperature dependence due to the kT/q terms is eliminated if all the transistors are at the same temperature.

Components  $R_s$ ,  $R_4$ ,  $C_1$  and  $C_2$  do not enter into this analysis. They are used to reduce the loop gain round the i.cs so that instability, which is always a problem with these circuits, does not occur. Previous experience suggested that both  $C_1$  and  $C_2$  should be 100pF but on this occasion for reasons unknown this was not so.

Note that the transistors used obey the log law most closely at currents below 1mA. This constrains  $R_1$  and  $R_2$  to be

dependent in large measure on the values of  $V_1$  and  $V_2$ . Furthermore, the op amp input currents will have an appreciable effect if  $I_1$  and/or  $I_2$  are less than  $1\mu A$ .

Note also that for cube law generation  $V_a = 3V_{be}$  and  $V_b =$  $2V_{be}$ . As V<sub>a</sub> is the larger we examine its effect on the op-amp output current. If  $V_a = 3V_{be}$ (i.e. about 2V) then the op-amp must deliver  $I_1$  to  $Tr_1$  and current  $(=V_{a}/R_{5})$  to  $R_{5}$ . Hence to avoid current saturation R<sub>5</sub> has to be large (e.g.  $R_5 = 100\Omega$ is too low). On the other hand, if  $R_{\bullet}$  is a potentiometer one requires that the transistor base current is negligible compared with the current through  $R_5$ , otherwise the voltage on the pot. arm will not be  $k_1 V_a$ . This indicates the need for a low value of R<sub>5</sub>. If the current gain of the transistors is taken as 50 then the value of  $1k\Omega$  for  $R_5$  is about the maximum useful.

Accuracy and range of circuits such as this is much affected by operational amplifier offset voltage, bias current and offset current. Op-amps such as the LM108 or a f.e.t. input stage op-amp such as the CA3130 are preferable to 741s.

#### **Circuit modifications**

• If one requires a voltage output rather than a current output then the modification above will suffice. V<sub>0</sub> is given by  $V_0 = I_L R$  where  $I_L$  is the current in Tr<sub>3</sub>.

The circuit is described as a cube generator, but from the expression for IL it is clear that any power law can be generated, with the provisos that n-m=1for temperature compensation, and that n an m are both greater than 1. This allows one to obtain  $V_0 = V^{-2}$  but keeping  $V_1$  constant and using  $V_2$  as the input (n=3,m=2), but does not allow one to obtain fractional power laws. This can be overcome by implicit power law generation i.e. by putting a power law device  $y = x^k$ (y output, x input) in the feedback path of an op-amp so that  $V_0 = V_{in^{1/k}}$ . A partial alternative is to modify the original circuit so that instead of  $V_a = nV_{be_1}$ ,  $V_b = mV_{be_2}$

where n and m are greater than 1 one obtains the same form for  $V_a$  and  $V_b$  but with m less than 1. Such a modification is shown centre. This enables one to obtain negative fractional indices. Positive fractional indices with temperature compensation cannot be obtained in this way.

137

The circuit shown bottom is a cube law generator (Ref. 1). More generally  $V_0 = V_{in}^a$ , where  $a=16.7R_{\phi}/(R_{\phi}+R_{10})$  so that one can obtain any positive power law. Like the original circuit two transistors are fed from potentiometers ( $R_2$ - $R_3$ ,  $R_{10}$ - $R_{\phi}$ ). The circuit is very similar to the multiplier in ref. 2.

#### References

National Semiconductor application notes AN30.

Set 29, card 4

Set 30, card 7

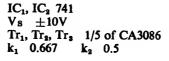

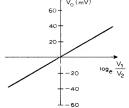

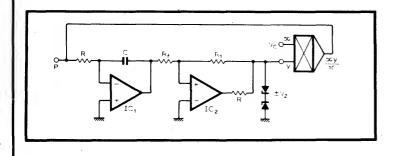

# Logarithmic amplifier $\overbrace{V_1}^{R_1} \overbrace{V_2}^{T_{r_1}} \overbrace{R_3}^{T_{r_1}} \underset{R_4}{\overset{V_2}{\underset{C_2}{\underset{C_2}{\underset{H_1}{\underset{C_1}{\underset{C_2}{\underset{C_2}{\underset{H_2}{\underset{C_2}{\underset{C_2}{\underset{H_2}{\underset{C_2}{\underset{C_2}{\underset{H_2}{\underset{C_2}{\underset{C_2}{\underset{H_2}{\underset{C_2}{\underset{C_2}{\underset{H_2}{\underset{C_2}{\underset{H_2}{\underset{C_2}{\underset{H_2}{\underset{C_2}{\underset{H_2}{\underset{C_2}{\underset{H_2}{\underset{C_2}{\underset{H_2}{\underset{C_2}{\underset{H_2}{\underset{C_2}{\underset{H_2}{\underset{H_2}{\underset{C_2}{\underset{H_2}{\underset{H_2}{\underset{C_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_2}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{\underset{H_1}{H$

#### **Circuit description**

The following equations can immediately be given

$$V_{\rm O} = V_{\rm be1} - V_{\rm be2}$$

$$V_{\rm be1} = \frac{kT}{q} \log_{\rm e} \frac{I_1}{I_{\rm S}}, V_{\rm be2} = \frac{kT}{q} \log_{\rm e} \frac{I_4}{I_{\rm S}}$$

$$I_1 = \frac{V_1}{R_1}, I_2 = \frac{V_2}{R_2}$$

Hence  $V_{\rm O} = \frac{kT}{q} \log_{\rm e} \frac{V_1}{V_2}$

i.e. if  $V_2$  is held constant then Vo is proportional to the log of V<sub>1</sub>. At room temperatures  $kT/q \approx 26$ mV and for any octave change in  $V_1/V_2$ , Vo will change by approximately 18mV.

Inclusion of R<sub>3</sub> and C<sub>1</sub> around IC<sub>1</sub> and of  $R_4$  and  $C_2$ around IC<sub>2</sub> prevents oscillation of the amplifiers. Considering  $IC_1$ , the loop gain includes the transistor gain. The transistor  $Tr_1$  is in common-base mode and hence has a voltage gain  $g_{\rm m}R_1$ ,  $R_1$ being the load on Tr<sub>1</sub> and is by superposition connected to ground. The loop gain can be very high. Resistor R<sub>3</sub> reduces the proportion of the output voltage fed to Tr<sub>1</sub> and hence reduces the gain. Likewise, high frequency gains are reduced to zero by the inclusion of  $C_1$  across the amplifier.

Despite these safeguards the

circuit does have a tendency to oscillate and care must be taken with wiring. Note that the transistor  $g_m$  is linearly related to the current so the problem is increased for high current levels. Further, at high current levels bulk resistance effects in the transistor come into play and destroy the simple logarithmic relationship. It is, therefore, important to keep  $V_1/R_1$  and  $V_2/R_2$  to levels which the transistors will accept.

#### **Circuit modifications**

Methods of temperature compensation using transistor arrays have recently been reported, refs. 1, 2. A simpler method has been devised using two of the transistors in the CA3086 package so that a controlled temperature can be achieved in this package at the same time as using two of the remainder for the logarithmic amplifier. Details will appear in a future set. The circuit shown above acts in a manner very similar to the basic circuit overleaf. It is easy to show that

$$V_0 = \frac{R_3 + R_4}{R_4} (V_{be_2} - V_{be_1})$$

from which

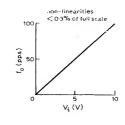

IC<sub>1</sub>, IC<sub>2</sub> 741

$$\pm$$

7.5V supplies

Tr<sub>1</sub>, Tr<sub>2</sub> 1/5 of CA3086

**Performance**

With V<sub>2</sub> set at 0.25V the grap

2.2kΩ 100pF

Components

$C_1, C_2$

$\begin{array}{rccc} R_{1}, R_{2} & 10k\Omega \\ R_{3}, R_{4} & 2.2k\Omega \end{array}$

With  $V_2$  set at 0.25V the graph shown was obtained. Origin corresponds to  $V_1$ =0.25V, slope is 17.8mV/octave and

$$V_{\rm O} = \frac{-kT}{q} \left( \frac{R_3 + R_4}{R_4} \right) \log_{\rm e} \left( \frac{V_1 R_2}{R_1 V_2} \right)$$

Note that V<sub>0</sub> is now referred to ground potential. Further, if  $R_3 \gg R_4$ , and if  $R_4$  is a temperature-controlled resistor, then compensation is possible. As T is in Kelvins, V<sub>0</sub> will change by 0.33% per deg. C.

This circuit with the bias and compensation networks shown is described in some detail in ref. 3. It is claimed to have a dynamic range of 100dB. The circuit is slow, the output typically taking several milliseconds to settle within 1% of final value. The LM108 does not have great bandwidth but does have a low input current, making it suitable as an input stage. To speed up the system by replacing the LM108 by an LM101 requires some modification, shown above right. The LM102 is connected as a voltage follower so that the combination of LM102 and LM101A with  $Tr_1$  in the feedback path is the same as that of the figure on the left expect that the LM102 effectively diode connects Tr<sub>1</sub>. This reduces the dynamic range (80dB is possible) but allows feedforward compensation on

v<sub>o</sub> (mV)

Set 30: R.m.s./log/power laws-7

range of V<sub>1</sub> two decades, from 0.03V to 4.0V. Linearity better than 1%.

the LM101A, thereby increasing the speed of response by about two orders of magnitude. Very little current will flow through the 1k $\Omega$  resistor between the output of the LM102 and the LM101A and the input terminal of that LM101A is a virtual earth so that

$$V_{\rm O} = \frac{R_3 + R_4}{R_4} \left( V_{\rm be_2} - V_{\rm be_1} \right)$$

For further details see ref. 3.

#### References

Shah, M. J. Using transistor arrays for temperature compensation, *Electronics*, April 12, 1973, p. 103.

Shah, M. J. Self-regulating temperature stabilised reference, EDN, May 20, 1974, pp. 74-6.

National Semiconductor application notes AN30.

#### **Related circuits**

Set 29, card 4 Set 30, card 6

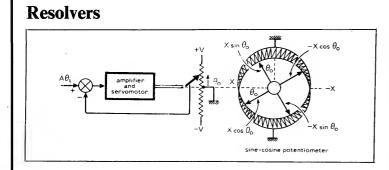

# Set 30: R.m.s./log/power laws---8

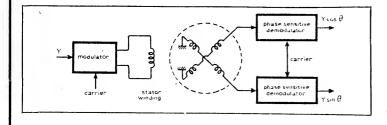

A resolver is a device which with input v produces an output proportional to sin v or cos v: frequently both outputs are available giving  $a = R \sin v$  and  $b = R\cos v$  i.e. the vector R / v is resolved into its two rectangular components. These devices are used widely in navigation and range instrumentation, where high bandwidth is not required. The circuit above left consists of a simple servomechanism which will rotate through  $\theta_0$  degrees in response to some input. If A=1 then  $\tau_0=\theta_i$  in the steady state in response to a step.

In addition to the normal feedback potentiometer there is also attached to the shaft a sine-cosine potentiometer generally wound through 360° and having four slider arms as shown. The shaft of this potentiometer will rotate through the same angle as the output shaft. Such arrangements suffer from all the usual disadvantages of potentiometers, wear, resolution, accuracy, etc. By using a gear box between motor shaft and sine-cosine potentiometer shaft one can improve the accuracy and resolution to less than 0.5%(static). Use of a gear box requires scaling of the input to

suit. Dynamic accuracy depends largely on the servomotor.

In the induction resolver (below) the sine-cosine potentiometer is replaced by an induction machine shown, having a stator winding and two mutually perpendicular rotor windings. The device is best regarded as a transformer, the output voltages being generated in the rotor windings by induction. The angle  $\theta$ shown in the output expression is the angle between the axes and is obtained by the servo arrangement shown left or by any other equivalent. The carrier frequency is usually 400Hz. Induction resolvers have the considerable advantage of being relatively

maintenance-free since there are no rubbing contacts, apart from slip rings. The main problem is the production of an accurate modulation/demodulation system.

By the addition of a second stator winding with input X, perpendicular to that shown one can obtain outputs  $U = -X\sin\theta + Y\cos\theta$  $V = X\cos\theta + Y\sin\theta$ which enable one to perform co-ordinate transformations. Electronic resolvers are not

so common as the electromechanical types. The

most compon type is that using a diode function generator as described in the quarter squares multiplier card (set 29, card 1). The cost of such a resolver depends on the range of input being considered, the simplest being that corresponding to  $0^{\circ} \rightarrow 90^{\circ}$ .

The diagram below (top) shows a different approach which conceptually is very simple. A comparator is arranged to trigger a sample and hold circuit when its sawtooth input exceeds v. It is essential that the sawtooth be synchronous with the input to the sample and hold circuit. This can be done fairly simply by generating the sawtooth from an integrator with a direct comparators, one fed from the sawtooth ramping from 0 to 2b, the other ramping from -b/2 to +3b/2. In the last case the bias voltage must be able to go negative to obtain angles in the fourth quadrant.

Other electronic methods use pulse width modulation and averaging circuits. Such a scheme is the one shown left which produces an output proportional to  $\cos X$ . The modulator produces pulses of width  $(\pi - 2X)/\omega$  symmetrically placed about the peaks of the sinusoidal input. When these are fed to the switch, e.g. CD4016AE analogue transmission gate, the output is a chopped sinusoidal waveform whose average can be shown to

input voltage. This produces a ramp output voltage which has to be reduced to zero every  $2\pi$  radians. This can be done by inserting a f.e.t. in parallel with the feedback capacitor and triggering the f.e.t. from a monostable fed from  $R\sin \omega t$  via a comparator.

If  $R\sin \pi v/b$  and  $R\cos \pi v/b$ are required simultaneously then one can use two sample and hold circuits, both fed from the same comparator if  $R\sin \omega t$  and  $R\cos \omega t$  can be generated simultaneously. Both of these signals are generated in the two integrator loop (set 26, cards 6 and 7).

If only one signal source is available then use two sample and holds, each fed with Rsin $\omega t$ , but triggered from different be proportional to  $\cos X$ . If the output pulses from the pulse width modulator are centred about the zero-crossings of the sinusoid, the output will be proportional to  $\sin X$ .

#### Reference

Schmid, H. Integrated circuits replace the electromechanical resolver, *Electronics*, Jan. 1966.

139

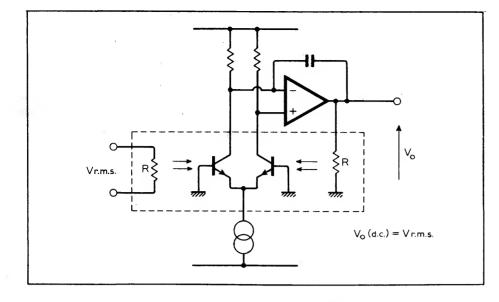

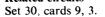

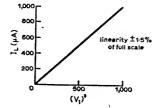

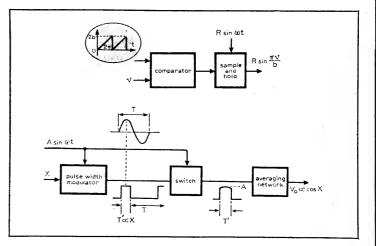

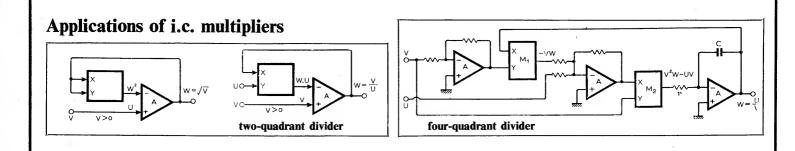

Many multiplier modules are now available on the market (e.g. MC1594L, XR2308, AD433J). The reduced cost and improved capability and accuracy of them has produced an increasing usage; unfortunately the existence of different types has produced confusion to the uninitiated. There are at least three distinct types: those having two inputs X and Y, the output being KXY, with K a scale factor; those which have two differential inputs X and Y, the output being KXY; those having three inputs X, Y and Z the output being KXY/Z - this last one is obviously a combined multiplier/divider. Adding to the confusion is the apparently magical way in which some functions are generated. It is easy to see that the final answer is correct but

answer was arrived at. Many of the uses of multipliers involve the implicit solution of some equation. This means that the output is fed back in some manner, thereby affecting itself. All of the circuits in this card involve an implicit solution.

there is never a logical thought

process shown by which the

Above left is shown a circuit for the generation of  $\sqrt{V}$ . The output W is fed to a multiplier with both input terminals connected together to form a squarer. This squarer is in the feedback path of an op-amp A. As the differential input voltage of the op-amp must be zero,  $V-W^2=0$  i.e.  $W=\sqrt{V}$ . Note that V must be positive, as otherwise negative feedback round the loop is lost and latch-up will occur.

Above centre is a multiplier connected in the feedback path

of an op-amp to provide an overall division function. Polarity inversion through the multiplier must be avoided to prevent positive feedback and this restricts U to being positive. On the other hand V can be either positive or negative so that in the U-V plane one is allowed to operate in the two quadrants for which U is positive. It is clearly impossible for U to be zero but additionally if U is very small one obtains a very small feedback signal so that offset voltages and currents can cause latch up.

Above right is a four-quadrant divider in which the output of  $M_2$  is  $V^2W-UV$ . If the inputs are d.c. then in the steady state the integrator output must be constant implying  $V^2W-UV=0$  i.e. W=U/V. It is claimed (ref. 1) that U and V can even go through zero together in this circuit. It also claimed that improved accuracy and stability are achieved. Both of these characteristics appear to reside in the action of the integrator whose output must change till the input is zero and whose output, moreover, cannot change rapidly.

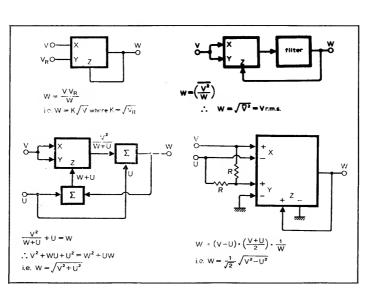

Turning now to the more complex multipliers, note the circuit simplicity of Figs 1 to 4. Fig. 1 shows a square rooting circuit, Fig. 2 an r.m.s. to d.c. converter (compare card 4) and Figs 3 and 4 show vector sum and vector differencing circuits. Note the vector sum relationship can also be obtained by mechanising the relationship  $V^{2}/(W-U)-U=W$ . The apparent simplicity vaporizes to an extent when one examines the actual implementations recommended by the module manufacturers. The modules are liberally surrounded by assorted external components the aim of which is to minimize errors. Fortunately these recommendations are fairly specific since the questions of errors and bandwidth are difficult for multipliers alone;

when combined in complex circuits the analysis really is awkward.

Another point which must be mentioned is that of scaling: it is always necessary to ensure that the design of a circuit is such that the multipliers do not saturate. This may seem obvious but with as many as six inputs, possible with the module of Fig. 4, it is all too easy to overlook this aspect or even to make a simple miscalculation.

The above circuits are intended only as a representative sample of some things that are possible with multipliers. Other applications will be found in the amplitude stabilization of oscillators (ref. 2), the design of voltage controlled oscillators, phase detectors and sample-and-hold circuits (ref. 3) and in the linearisation of a transducer output signal (ref. 4) among many.

#### References

1 Korn and Korn, Electronic analog and hybrid computers, 2nd edition, McGraw-Hill. 2 Vannerson and Smith, Fast amplitude stabilisation of an R-C oscillator, IEEE J. Solid State Circuits, vol. SC9, No. 4, Aug. 1974. 3 Ryan, C. R. Applications of a four quadrant multiplier, IEEE J. Solid State Circuits, Feb. 1970, pp. 45-8. 4 Trofimenkoff and Smallwood, Analog multiplier circuit linearises transducer output, IEEE Trans. vol. IM23, no. 3, Sept. 1974.

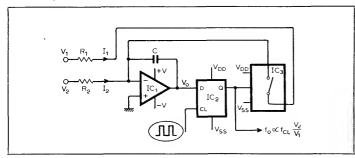

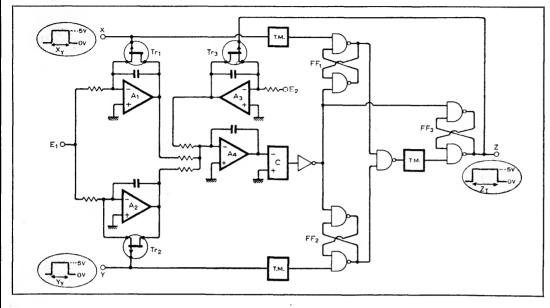

## Computation of $(x^2+y^2)^{\frac{1}{2}}$

Analogue information x and y is contained in the input pulse widths  $x_T$  and  $y_T$  respectively.

On the occurrence of the pulse x, the f.e.t. switch  $Tr_1$  opened and integrator  $A_1$ , fed from the d.c. signal E, ramps down and integrator  $A_4$  rises in a parabolic manner to a voltage

#### Performance data

All resistors  $50k\Omega$ , capacitors 10nF Tr1-Tr3 1H5012 C (comparator) SN72810 All logic SN7400 T.M. = trailing edge triggered monostable (see figure below)  $z_{\rm T} = (x_{\rm T}^2 + v_{\rm T}^2)^{\frac{1}{2}}$  within +1%for x<sub>T</sub> in range 0 to 2ms and  $y_{T}$  in range 0 to 1ms  $E_1 + 1.0V, E_2 - 1.0V$  $Ax_{T}^{2}$ , when the signal y is applied A<sub>2</sub> ramps giving an additional component  $By_{T}^{2}$  to the output of  $A_4$ . y may appear before, during or after x. Whatever the case, the output

of  $A_4$  rises to  $Ax_T^2 + By_T^2$ . At the end of this operation the R-S flip flops  $FF_1$  and  $FF_2$ combine with  $FF_3$  to open switch  $Tr_3$  allowing  $E_2$ (negative) to integrate via  $A_3$ and feed  $A_4$ . This causes the output of  $A_4$  to fall. When this fall reaches zero, the comparator C changes state and becomes high causing  $FF_3$  to become low and switching off  $Tr_3$ . The time for which  $E_2$  is applied is

$$z_{\mathrm{T}} = \left(\frac{Ax_{\mathrm{T}}^2}{C} + \frac{By_{\mathrm{T}}^2}{C}\right)^{\frac{1}{2}}$$

With the circuit elements chosen, A/C=B/C=1, giving the required relationship.

#### Reference

Ikeda, H. *Electronics Letters*, 30 Oct. 1975, vol. 11.

#### **Related circuits**

Set 19, card 4 Set 15, cards 4, 6 Set 30, card 1

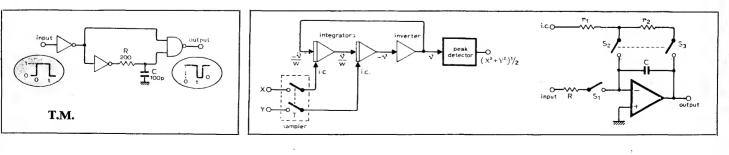

#### Alternative circuit

This circuit (middle) has the advantage that the inputs can be simple voltages, rather than pulse widths, but is restricted to two inputs (the previous scheme is readily extended to more than two inputs) and is less accurate. The circuit is an analogue

computer type circuit for the solution of  $v(t) + \omega^2 v(t) = 0$ where v(t) is the inverter output voltage,  $\omega$  is the "gain" of each integrator and the inverter gain is assumed to be -1. The solution of this equation is  $v(t) = z\sin(\omega t + \varphi)$ where  $z = (v(0)^2 + (v(0)/\omega^2)^{\frac{1}{2}}$ . Hence if the initial conditions (i.c.) on the two integrators are made equal to the analogue voltages x and y, the resulting oscillation has a peak value  $(x^2+y^2)^{\dagger}$ . Peak detectors suitable for this purpose are discussed in Set 4, card 2.

An arrangement suitable for the application of the initial conditions on the integrators is shown below right, in which the switches may be f.e.ts or analogue transmission gates such as the CD4016AE. For normal integration  $S_1$  is closed,  $S_2$  and  $S_3$  are open. When applying the i.cs,  $S_1$  is opened and S<sub>2</sub> and S<sub>3</sub> are closed. If  $r_1 = r_2$  then the integrator output rises to the i.c. voltage with time constant  $r_{2}c$  which should be made short by choice of r<sub>2</sub>. If the op-amps are capable of supplying current to  $(r_1 + r_2)$ and to the following integrator/ inverter then S3 may be dispensed with.

141

Using an integrator time constant of 1s, an inverter gain of 0.9 and a sampling period of 2s, J. S. C. Tan has reported an accuracy of  $\pm 2\%$  (approx) over a useful range of x and y, amplifier finally limiting the accuracy.

Note that the system is a two integrator loop oscillator (Set 26, cards 5, 6, 7) with no mechanism for amplitude stabilization so that continuous updating of x and y is essential i.e.  $T \gg 2\pi/\omega$  is undesirable.

#### Reference

Tan, J. S. C. *Electronic Letters*, 31 Oct. 1974, vol. 10.

Related circuit Set 30, cards 1, 5.

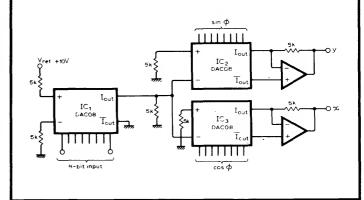

The above system employing multiplying d.a.c. converts digital polar co-ordinate information (r, sin  $\theta$ , cos  $\theta$ ) into analogue form. The output from  $IC_1$  is converted directly to a voltage through a resistive load, which is proportional to the digital value of r. This is then the source of the variable reference currents for IC<sub>2</sub> and IC<sub>3</sub> The output current is the product of the reference input current and the digital input representing the sine or cosine information. The op-amps

convert the currents into a positive-going voltages e.g. an all-ones r input provides -10V at IC<sub>1</sub> output, and hence a 2mA reference current into the next stage, the output current then depending on the digital sine or cosine entered. For all-zeros at r, the input reference current to IC<sub>2</sub>, IC<sub>3</sub>, is zero, giving zero output current and hence zero output voltage at X and Y.

Electronic Eng., Jan. 1976, Applied ideas.

142

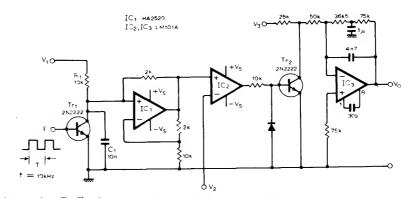

#### Charging current of $C_1$ is effectively $V_1/R_1$ which generates a ramp voltage at the input of IC<sub>2</sub>, used as a comparator. Capacitor C<sub>1</sub> periodically discharged by the pulse train into transistor Tr<sub>1</sub>. The ramp voltage at the output of IC<sub>1</sub> will reach V<sub>2</sub> after a time

$$t = CV/I = C_1 V_2 R_1/V_1.$$

Hence  $t/T = C_1 V_2 R_1 / V_1 T$ , where T is duty cycle at the output of A<sub>2</sub>. This modulates the input to the active filter IC<sub>3</sub>, which provides an output

$$V_{\rm O} = -C_1 V_2 R_1 V_3 / V_1 T.$$

If T is made equal to  $R_1C_1$ , then  $V_0 = -V_2V_3/V_1$ . If  $V_1$  is kept constant, the circuit acts as a multiplier. If  $V_2$  is maintained

constant, then an analogue divider is implemented. Input levels should be less than +10V (all signals must be positive) and

$V_2$  should be less than  $V_1$ . **Reference** Clark, R. S. *Electronic Design*, Jan. 5, 1976. p. 118.

This circuit provides a means of controlling the frequency of the square/triangle generator comprising an integrator (IC<sub>1</sub>) and Schmitt comparator (IC<sub>2</sub>). The input signal to y is constrained by the back-to-back zener diodes to be  $\pm V_z$ . This is multiplied by the control voltage  $V_c$ , and

hence multiplies the voltage at P by the same factor, which therefore modifies the charging rate of capacitor C and hence the frequency of oscillation. **Reference**

Graeme, G. J. Applications of Operational Amplifiers, Mc-

Graw Hall, 1973.

Set 30: Up-date