Originally published in the August 6, 1992, issue of EDN

## Dual op amp takes absolute difference

Lindo St Angel, Motorola General Systems Sector, Arlington Heights, IL

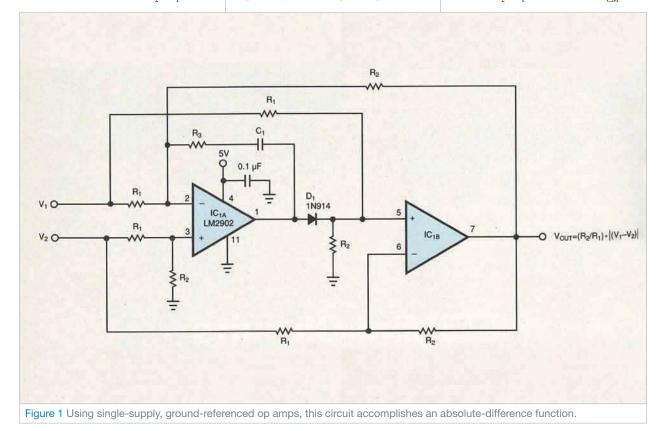

A traditional implementation of an absolute-difference function comprises a difference circuit followed by an absolute-value circuit; the entire circuit requires at least three op amps. The design problem is complicated in single-supply-only systems, which usually require an artificial ground, typically one-half of the supply. The circuit in **Figure 1** takes the absolute value of the difference of two voltages using only two single-supply, ground-referenced op amps. The circuit is designed for dc or low-speed operation.

For the case where  $V_1 > V_2$ ,  $IC_{1A}$  is disabled because diode  $D_1$  is off.  $IC_{1B}$  and its associated resistors form a classic difference circuit where  $V_{OUT} = (R_1/R_1)(V_1 - V_2)$ .

For the case where  $V_2 > V_1$ , diode

$D_1$  conducts, producing the composite amplifier system made up of both  $IC_{1A}$  and  $IC_{1B}$ , where  $V_{OUT} = (R_2/R_1)$  ( $V_2 - V_1$ ). Using these two **equations**, the overall function of the circuit for  $V_1$  and  $V_2$  greater than zero is as follows:  $V_{OUT} = (R_2/R_1)|(V_1 - V_2)|$ .

The circuit was built and tested with  $R_1$ =10 k $\Omega$  and  $R_2$ =220 k $\Omega$ . For  $V_2$ > $V_1$ , the composite amplifier system has poor phase margin and is unstable. Thus, the circuit compensates the loop with the dominant pole formed by  $R_3$  and  $C_1$ . At a gain of 22 and a desired response time of about 300 µsec (the 10 to 90% rise time when  $V_2$  becomes 0.1V greater than  $V_1$ ), values of  $R_3$ =56 k $\Omega$  and  $C_1$ =850 pF produced the best empirical results.  $R_3$  and  $C_1$  will vary, depending on the required speed of the

response and the closed-loop gain.

Also, when  $V_2 > V_1$ , the output of IC<sub>1A</sub> becomes a function of the factor  $2V_2 - V_1$ . Thus, IC<sub>1A</sub> may saturate for large values of  $V_2$ . The factor's upper limit is as follows, where  $V_{SAT}$  is the saturation voltage for IC<sub>1A</sub>:  $(2V_2 - V_1) < V_{SAT}(R_1 + R_2)/R_2$ . For the LM2902 operating from 5V,  $V_{SAT}$  is approximately 3.5V. This last **equation** also implicitly sets a common-mode voltage  $(V_{CM})$  limitation. You can see this limitation by setting  $V_1 = V_2 = V_{CM}$  and allowing the factor  $(2V_2 - V_1)$  to reduce to  $V_{CM}$ .

52 **EDN** | JUNE 7, 2012 [www.edn.com]