# Drift Compensation Techniques for Integrated DC Amplifiers

Robert J. Widlar Apartado Postal 541 Puerto Vallarta, Jalisco Mexico

## Introduction

With DC amplifiers, it is usually possible to substantially improve drift performance by using additional circuitry along with some form of adjustment. In fact, one of the reasons that discrete-component operational amplifiers have better input current specifications than monolithic amplifiers is that current compensation is used. Monolithic circuits cannot incorporate these techniques because it is not possible to select components or make adjustments. These adjustments can, however, be made external to the amplifier. This article will discuss a number of compensation methods which can substantially reduce the input currents of monolithic amplifiers, especially in limited-temperature-range applications.

Bias current compensation reduces offset and drift when the amplifier is operated from high source resistances. With low source resistances, such as a thermocouple, the drift contribution due to bias current can be made quite small. In this case, the offset voltage drift becomes important.

A technique is presented here by which offset voltage drifts better than 0.5  $\mu$ V/°C can be realized. The compensation technique involves only a single room-temperature balance adjustment. Therefore, chopper-stabilized performance can be realized, with low source resistances, in a fairly-simple amplifier without tedious cut-and-try compensation methods.

# bias current compensation

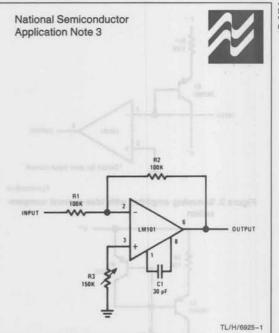

The simplest and most effective way of compensating for bias currents is shown in *Figure 1*. Here, the offset produced by the bias current on the inverting input is cancelled by the offset voltage produced across the variable resistor,  $R_3$ . The main advantage of this scheme, besides its simplicity, is that the bias currents of the two input transistors tend to track well over temperature so that low drift is also achieved. The disadvantage of the method is that a given compensation setting works only with fixed feedback resistors, and the compensation must be readjusted if the equivalent parallel resistance of  $R_1$  and  $R_2$  is changed.

## Figure 1. Summing amplifier with blas-current compensation for fixed source resistances

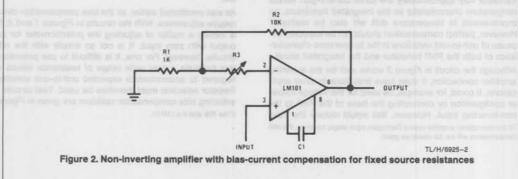

Figure 2 shows a similar circuit for a non-inverting amplifier. The offset voltage produced across the DC resistance of the source due to the input current is cancelled by the drop across R<sub>3</sub>. For proper adjustment range, R<sub>3</sub> should have a maximum value about three times the source resistance and the equivalent parallel resistance of R<sub>1</sub> and R<sub>2</sub> should be less than one-third the input source resistance.

This circuit has the same advantages as that in *Figure 1*, however, it can only be used when the input source has a fixed DC resistance. In many applications, such as long-interval integrators, sample-and-hold circuits, switched-gain amplifiers or voltage followers operating from unknown source, the source impedance is not defined. In these cases other compensation schemes must be used.

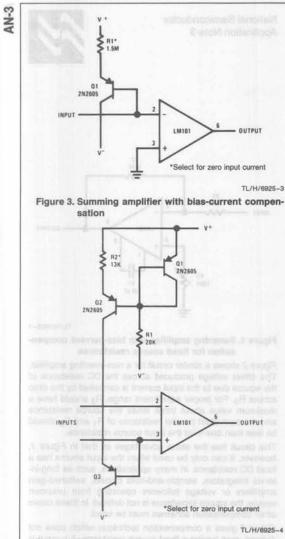

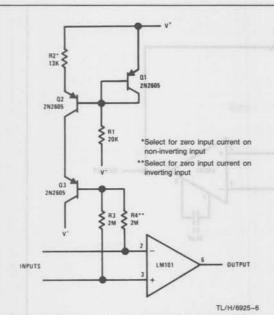

Figure 3 gives a compensation technique which does not depend upon having a fixed source resistance. A current is injected into the input terminal from the base of a PNP transistor. Since NPN input transistors are used on the integrated amplifier,\* the base current of the PNP balances out the \*This is true for all monolithic operational amplifiers presently available.

1

## Figure 4. Bias-current compensation for non-inverting amplifier operated over large common mode range

base current of the NPN. Further, since a silicon-planar PNP transistor has approximately the same current-gain versus temperature characteristic as the integrated transistors, an improvement in temperature drift will also be realized.<sup>†</sup> However, perfect compensation should not be expected because of unit-to-unit variations in the temperature characteristics of both the PNP transistor and the integrated circuit.

Although the circuit in *Figure 3* works well for the summing amplifier connection, it does have limitations in other applications. It could, for example, be used for the voltage follower configuration by connecting the base of the PNP to the non-inverting input. However, this would reduce the input 'If the operational amplifier uses a Darlington input stage, however, the drift compensation will not be nearly as good.

impedance (to about 150 M $\Omega$ ) because the current supplied by the PNP will vary with the input voltage level.

If this characteristic is objectionable, the more-complicated circuit shown in *Figure 4* can be used.

The emitter of the PNP transistor is fed from a current source so that the compensating current does not vary with input-voltage level. The design of the current source is such as to give it about the same characteristics as those on the input stage of the better monolithic amplifiers<sup>‡</sup> to give closer compensation with changes in temperature and supply voltage. The circuit makes use of the emitter base voltage differential between two transistors operated at different collector currents.<sup>1,2</sup> Although it is recommended in the references that these transistors be well matched, it is not really necessary since the devices are operated at much different collector currents.

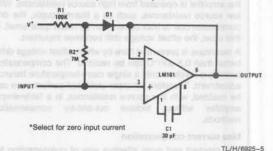

Figure 5 shows another compensation scheme for the voltage follower connection. This circuit is much simpler than that shown in Figure 4, but the temperature compensation is not quite as good. The compensating current is obtained through a resistor connected across a diode which is bootstrapped to the output. The diode acts as a regulator so that the compensating current does not change appreciably with signal level, giving input impedances about 1000 M $\Omega$ . The negative temperature coefficient of the diode voltage also provides some temperature compensation.

Figure 5. Voltage follower with bias-current compensation

All the circuits discussed thus far have been tailored for particular applications. *Figure 6* shows a completely-general scheme wherein both inputs are current compensated over the full common mode range as well as against power supply and temperature variations. This circuit is suitable for use either as a summing amplifier or as a non-inverting amplifier. It is not required that the DC impedance seen by both inputs be equal, although lower drift can be expected if they are.

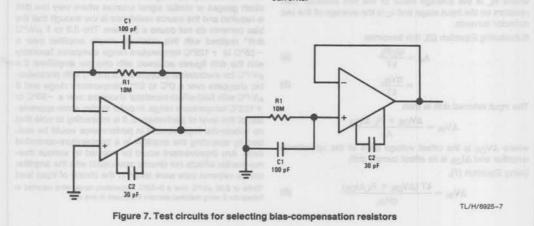

As was mentioned earlier, all the bias compensation circuits require adjustment. With the circuits in *Figures 1* and 2, this is merely a matter of adjusting the potentiometer for zero output with zero input. It is not so simple with the other circuits, however. For one, it is difficult to use potentiometers because a very wide range of resistance values are required to accommodate expected unit-to-unit variations. Resistor selection must therefore be used. Test circuits for selecting bias compensation resistors are given in *Figure 7*. <sup>4</sup>The 709 and the LM101.

Figure 6. Bias-current compensation for differential inputs

#### offset voltage compensation

The highly predictable behavior of the emitter-base voltage of transistors has suggested a unique drift compensation method; it is shown in Reference 3 that the offset voltage drift of a differential transistor pair can be reduced by about an order of magnitude by unbalancing the collector currents such that the initial offset voltage is zero. The basis for this comes from the equation for the emitter-base voltage differential of two transistors operating at the same temperature:

$$\Delta V_{BE} = \frac{kT}{q} \log_{\theta} \frac{l_{S2}}{l_{S1}} - \frac{kT}{q} \log_{\theta} \frac{l_{C2}}{l_{C1}}$$

(1)

where k is Boltzmann's constant, T is the absolute temperature, q is the charge of an electron, I<sub>S</sub> is a constant which depends only on how the transistor is made and I<sub>C</sub> is the collector current. This equation is derived in Reference 2. It is worthwhile noting here that these expressions make no assumptions about the current gain of the transistors. It is shown in References 5 and 6 that the emitter-base voltage is a function of collector current, not emitter current. Therefore, the balance will not be upset by base current (except for interaction with the DC source resistance).

AN-3

The first term in Equation (1) is the offset voltage of the two transistors for equal collector currents. It can be seen that this offset voltage is directly proportional to the absolute temperature-a fact which is substantiated by experiment.<sup>4</sup> The second term is the change of offset voltage which arises from operating the transistors at unequal collector currents. For a fixed ratio of collector currents, this is also proportional to absolute temperature. Hence, if the collector currents are unbalanced in a fixed ratio to give a zero emitter-base voltage differential, the temperature drift will also be zero.

Experiment indicates that this is indeed true. Thermal drifts less than 100  $\mu$ V over the  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature range have been realized consistently. In order to obtain these low drifts, however, it is almost necessary to use a monolithic transistor pair, since a 0.05°C temperature differential will give a 100  $\mu$ V drift. With a monolithic pair, the physical proximity of the devices as well as the high thermal conductivity of silicon holds this differential to an absolute minimum.

For low drift, the transistors must operate from a low enough source resistance that the voltage drop across the source due to base current (or base current differential if both bases see the same resistance) is insignificant. Furthermore, the transistors must be operated at a low enough collector current that the emitter-contact and base-spreading resistances are negligible, since Equation (1) assumes that they are zero.

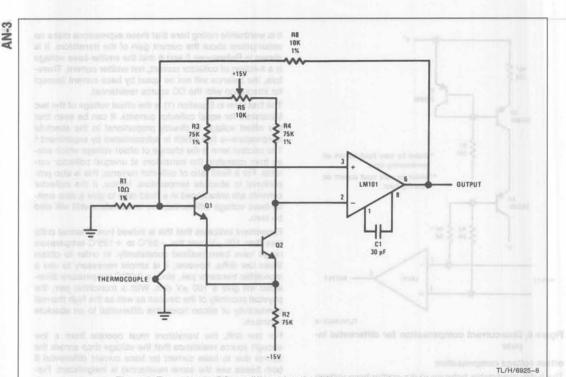

A complete amplifier using this principle is shown in *Figure* 8. A monolithic transistor pair is used as a preamplifier for a conventional operational amplifier. A null potentiometer, which is set for zero output for zero input, unbalances the collector load resistors of the transistor pair such that the collector currents are unbalanced for zero offset. This gives minimum drift. An interesting feature of the circuit is that the performance is relatively unaffected by supply voltage variations: a 1V change in either supply causes an offset voltage change of about 10  $\mu$ V. This happens because neither term in Equation (1) is affected by the magnitude of the collector currents.

3

Figure 8. Example of a DC amplifier using the drift-compensation technique

In order to get low drift, it is necessary that the gain of the preamplifier be high enough so that the drift of the operational amplifier does not degrade performance. The gain can be determined from the expression for the transconductance of the input transistors:

$$\frac{\partial I_{C}}{\partial V_{BE}} = \frac{qI_{C}}{kT}$$

(2)

The voltage gain is

$$y = \frac{\partial V_{OUT}}{\partial V_{IN}}$$

(3)

$$= \frac{\partial I_C}{\partial V_{DE}} R_L$$

(4)

where  $R_L$  is the average value of the two collector load resistors on the input stage and  $I_C$  is the average of the two collector currents.

Substituting Equation (2), this becomes

A

Δ

$$V = \frac{ql_{C}R_{L}}{kT}$$

(5)

=  $\frac{qV_{RL}}{kT}$ (6)

The input referred drift is then

$$\Delta V_{\rm IN} = \frac{\Delta V_{\rm OS} + R_{\rm L} \Delta I_{\rm OS}}{A_{\rm V}}$$

where  $\Delta V_{OS}$  is the offset voltage drive of the operational amplifier and  $\Delta I_{OS}$  is its offset current drift. Using Equation (7),

$$\Delta V_{\rm IN} = \frac{\rm kT \left( \Delta V_{\rm OS} + R_{\rm L} \Delta I_{\rm OS} \right)}{\rm qV_{\rm RL}}$$

With the circuit shown in *Figure 8*, Equation (8) gives a 25  $\mu$ V input-referred drift for every 10 mV of offset voltage drift or for every 100 nA of offset current drift. It is obvious from this that the offset current drift is most important if an operational amplifier with bipolar input transistors is used.

Another important consideration is the matching of the collector load resistors on the preamplifier stage. A 0.1-percent imbalance in the load resistors due to thermal mismatches or any other cause will produce a 25  $\mu$ V shift in offset. This includes the balancing potentiometer which can introduce a nerror that will depend on how far it is set off midpoint if it has a different temperature coefficient than the resistors.

The most obvious use of this type of low drift amplifier is with thermocouples, magnetometers, current shunts, wire strain gauges or similar signal sources where very low drift is required and the source resistance is low enough that the bias currents do not cause a problem. The 0.5 to 1 µV/°C drift\* realized with this relatively simple amplifier over a -55°C to +125°C temperature range compares favorably with the drift figures achieved with chopper amplifiers: 0.4 µV/°C for mechanical choppers, 0.5 µV/°C with photoelectric choppers over a 0°C to 55°C temperature range and 2 µV/°C with field-effect-transistor choppers over a -55°C to + 125°C temperature range. In order to give some appreciation of the level of performance, it is interesting to note that no substantial improvement in performance would be realized by operating the amplifier in a temperature-controlled oven. Any improvement would be masked by various thermo-electric effects not directly associated with the amplifier unless extreme care were taken in the choice of input lead \*Drifts of 0.05 µV/°C over a 0-50°C temperature range were reported in Reference 3 using matched discrete transistors in one can.

4

(8)

material, the method of making connections and the balancing of thermal paths. These factors are, in fact, important when making oven tests to verify the drift of the amplifier since thermoelectric effects can easily produce drift voltages larger than those of the amplifier if they are not properly handled.

# summary

A number of compensation circuits designed to increase the DC resolution of monolithic operational amplifiers have been presented. Both current compensation techniques for high impedance levels as well as methods of achieving chopper-stabilized drift performance at low impedance levels have been covered.

Fairly-simple current compensation which requires that the impedance levels be fixed have been described along with compensation which is effective in cases where the source impedance is not well defined. This latter category includes long-interval integrators, sample-and-hold circuits, switched-gain amplifiers or voltage followers which operate from an unknown source. The application of these schemes is generally limited to integrated amplifiers since modular amplifiers almost always incorporate current compensation. The drift-reduction techniques provide stabilities better than  $0.5 \ \mu V/^{\circ}C$  for low impedance sources, such as thermocouples, current shunts or strain gauges. With a properly designed circuit, compensation depends only on a single room temperature adjustment, so excellent performance can be obtained from a fairly-simple amplifier.

A DESCRIPTION

#### Equal 1. Free-cutulog multivituritor

Another educations of the occurs in thes A will always will used and cannot more up alread there in more do negative feedback then positive freedback. This can be a problem with many "feetback" realivibuitms.

Since the operational anuither is used open loop, the second frequency (comparation comparately are not required at a loop will aver alias it down Bit even without the UV pF operation the ULMOT down have speed timbations which neence the area of the strain to inequancies below about 2 why.

The large and votage tange of the UANOT (both differential and angle and/of permitte large votage extra manifest that averal time constants of the linning capacitor, it.t. format to seek With stort other amplitum. Fit must be rethand to seek form exceeding these subge, which regulate that OT be thereeved for several store when be permitten attention and D, emining polarized capacitors may be used by relating them to the polarized capacitors are no exact of ground.

#### married Scilling Physics

Frequently to the design of linear registration is increasingly to take a variage which is released to norme do term and provide an empirical acquire which is released to gravital meaning any photoward way of voltag the is to an early acquire terminal entries to the observation of Space 26. The statement terminal provide the observation of the approtion the terminal provide term the input divider RD and acquire that the termination materials from the compound material to present encreters outputs from the compound material to present encreters outputs from the compound material to present encreters outputs from the compound materials of the termination of the termination.

#### references

- R. J. Widlar, "A Unique Circuit Design for a High Performance Operational Amplifier Especially Suited to Monolithic Construction," *Proc. of NEC*, Vol. XXI, pp. 85-89, October, 1965.

- R. J. Widlar, "Some Circuit Design Techniques for Linear Integrated Circuits," *IEEE Trans. on Circuit Theory*, Vol. XII, pp. 586-590, December, 1965.

- A. H. Hoffait and R. D. Thorton, "Limitations of Transistor DC Amplifiers," *IEEE Proc.*, Vol. 52, pp. 179-184, February, 1964.

- A. Tuszynski, "Correlation Between the Base-Emitter Voltage and Its Temperature Coefficient," *Solid State De*sign, pp. 32-35, July, 1962.

- C. T. Sah, "Effect of Surface Recombination and Channel on P-N Junction and Transistor Characteristics," *IRE Trans. on Electron Devices*, Vol. ED-9, pp. 94-108, January, 1962.

- J. E. Iwersen, A. R. Bray, and J. J. Kleimack, "Low-Current Alpha in Silicon Transistors," *IRE Trans. on Electron Devices*, Vol. ED-9, pp. 474-478, November, 1962.

Although the dimetra prevented use the LM101 quantities at anythine and the LM102 scharge folds or produced by Mashard Service-relacion, most as generate recommender for allocation of anything and the manufacture in manifest comply compared in the account. A comparise result at a delines are black fold account. A comparise result are of the LM101 is given elements and many a field of the delines are a 200 otherweat and value results at 200 and a trace a 200 otherweat and value results at 200 and a trace a 200 otherweat water and the second at 200 be compared with a single are allowed and a 200 be compared with a single are allowed and a 200 be compared with a single are of a second at 200 be compared with a single are of account at 200 be compared with a single are of account at 200 be compared at the anything area of account at 200 be compared at the anything area of account at 200 be compared at the anything area of account at 200 be compared at the anything area of account at 200 be compared at the anything area of account at 200 be compared at the anything area of account at 200 be compared at the anything area of account at 200 be compared at the anything area of a 200 be compared at the anything area of account at 200 be compared at the anything area of a 200 be compared at the account at 200 be compare

#### retailigan wintermationation

The new monorphic behavior alternation of a second second