## Set 20: Transistor pairs

Tweedledum's query seems an especially appropriate way of starting the following article on transistor pairs. Not only are the advantages of each configuration not always clear, but sometimes it's difficult to see the true operational nature of the configuration. In the cards, 20 different connections of two transistors are described, excluding c.m.o.s. circuits and triple or mixed pair arrangements. This set of circuits is an important one in that many form the basic building bricks of integrated circuits-long-tailed pairs, current mirrors, and even cascode circuits and high-gain pairs. Both the article and card 4 discuss the merits of the different long-tailed pair configurations, the card giving useful formulae for gain, common-mode rejection and temperature drift. Cards 1 & 2 contain a thorough investigation of the properties of high current gain pairs-Darlington, complementary Darlington and four-terminal pairs-the results being given in the 16 graphs, all of course derived from the compiler's measurements. Various circuits can be developed by mixing various pairs and two examples are given on card 9. One uses a long-tailed pair with constantcurrent tail feeding a current mirror to produce a triangular-wave generator; the other is an operational amplifier using bipolar and m.o.s. devices with a single supply.

The complementary transistor switch of card 6 is the transistor equivalent of unijunction and thyristor switches, but has the advantage of being faster than either as high-speed transistors can be used. Other cards show how the current capability of a c.m.o.s. inverter can be simply increased (card 8); how a cascode circuit is re-arranged to avoid the need for a biasing voltage (card 3); and card 5 gives performance and descriptions of m.o.s. and bipolar current mirrors—now an integral part of operational amplifiers.

High current-gain pairs—I 1 High current-gain pairs—II 2 Cascode amplifier 3 Long-tailed pair 4 Current mirrors 5 Complementary switching transistors 6 Complementary emitter-follower 7 CMOS circuits 8 Triples and mixed pairs 9 Pot pourri 10 "Supplementary or complementary, opposites or composites?" asked Tweedledum. "Contrariwise", said Tweedledee. It is not the intention to rewrite "Alice...", but it is not always clear what the advantages are in d.c.-coupled pair configurations—voltage gain plus impedance change, super current-gains, p-n-p simulation, thermal compensation or perhaps a current source as a stabilizing network.

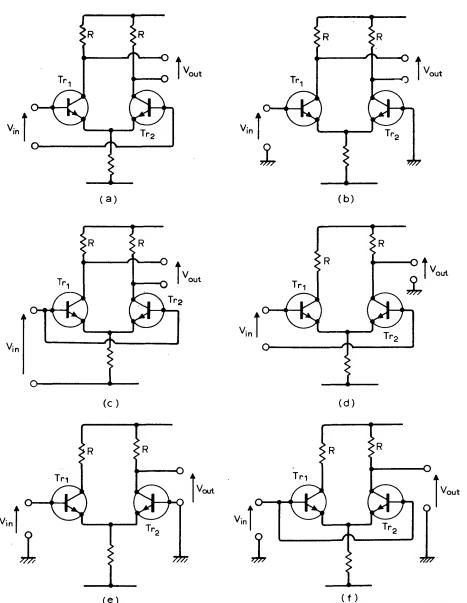

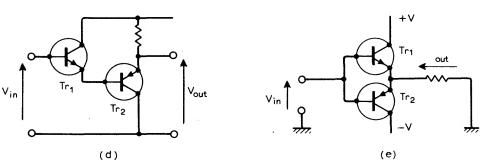

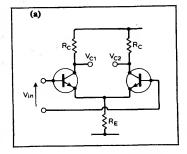

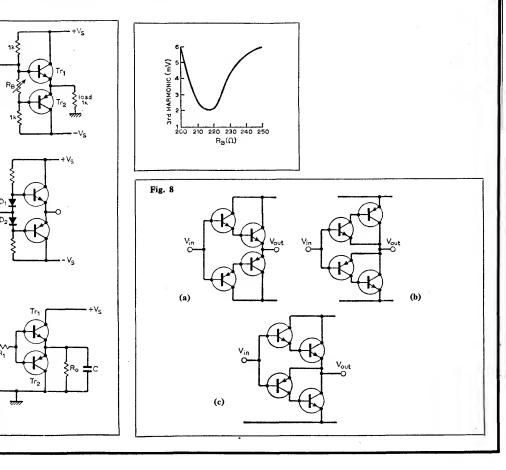

The pièce de resistance might be the long-tailed pair or differential amplifier (where would the linear i.c. be without it?) which provides some satisfying amplifying properties—some possible variations for small-signal operation are shown in Fig. 1. For example, the connection shown in Fig. 1(a) converts a signal difference between two inputs to equal, but antiphase collector signals. Signals common to both inputs (e.g. superposed noise signals from the same source) are reduced without affecting the differential gain, which is that due to a single transistor.

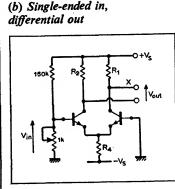

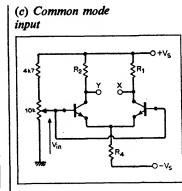

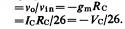

The ability of this amplifier to prevent amplification of a common signal is called the common-mode rejection ratio, being the ratio of the differential voltage gain to the common mode gain, usually expressed in dB. The single-ended inputs of Fig. 1(b) and (e) produce an output at  $Tr_2$  collector, equivalent to  $Tr_1$  as an emitter-follower driving  $Tr_2$  as a common-base amplifier. In addition, the output of  $Tr_1$  is equal in magnitude but antiphase to that of  $Tr_2$ , on the assumption of constant total current (long-tail). Hence the differential output in Fig. 1(b) is twice the singleended output. The voltage gains are approximately  $R/h_{ib}$  and  $\bar{R/2h_{ib}}$  for Fig. l(b) and (e) respectively, where  $h_{ib}$  is the effective input resistance of the common base configuration. Fig. 1(c) and (f) are not used as amplifiers, but are useful as a means of determining the gain to common mode signals. This should be much less than unity to give good rejection.

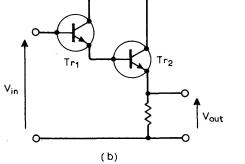

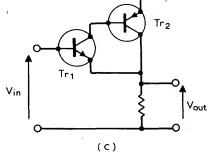

The common-emitter, common-base, connection shown in Fig. 2(a) is the cascode amplifier, where the first stage transistor  $Tr_1$  has current gain, and the second stage  $Tr_2$  has voltage gain. The advantages are a large gain-bandwidth

product and also, for high voltage outputs, the high breakdown value of the common base transistor  $Tr_2$  is essential.

The common collector-common collector pair of Fig. 2(b) is the familiar

Darlington connection, where the effective current would be approximately  $\beta^2$ , if the transistors were identical. This would be true for short-circuit outputs, but a practical value for the  $\beta$  of each transistor

Fig. 1. Variations of the long-tailed pair include circuits with differential input, differential output (a), single-input, differential output (b) & (c), differential input, single output (d), and single input and output (e) & (f).

Vin (a)

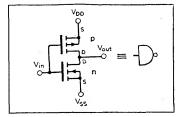

Fig. 2. Other ways of connecting two transistors are common-emitter, common-base i.e. cascode (a), common-collector pair i.e. Darlington (b), complementary pair with only one  $V_{be}$  drop (c), complementary pair with no  $V_{be}$  drop (d), symmetrical complementary pair i.e. class B amplifier (e), and the regenerative pair (f).

would be to specify the minimum value quoted by a manufacturer (assuming that discrete transistors are being discussed, because it must be remembered that super- $\beta$  packages are also available with defined current gains). The complementary connection of Fig. 2(c) provides only one  $V_{be}$  drop compared with Fig. 2(b), and that of (d) cancels the  $V_{be}$  drops, but offers some second-order residual offset between input and output, and requires a separate bias path (not shown) for  $Tr_1$  emitter current and  $Tr_2$  base current. Complementary versions may provide an advantage, in that the transistor choice for the first stage can be that with the highest current gain at low currents.

When opposite types of transistors are connected in complementary form, such as Fig. 2(e), we have the basis of a class-B amplifier. The circuit for each half-cycle of signal is essentially identical, and the load is driven from a low-impedance source, because each transistor acts as an emitter follower. An advantage is that interstage and output transformers are not necessary when such a circuit is used at audio frequencies.

The interconnection of n-p-n and p-n-p transistors as in Fig. 2(f) provides a regenerative switching action due to the positive feedback between collectors and bases. It is similar in operation to a unijunction transistor, and there are of course similarities with the thyristor. Switching speeds can be faster than a single unijunction device because high-frequency transistors can be employed. The same arrangement is the basis for a constant-current circuit (Circards set 6, card 5), while those sources which may

be classed as current controlled tend to use the current-mirror—no self-respecting operational amplifier would be without one!

The complementary-symmetry m.o.s. pair has been an excellent addition to the pair family. Besides being the basis of several logic gates, it also has application in multivibrators and as a linear amplifier.

A close study of most linear integratedcircuits will reveal the use of two or more of the pairs mentioned, to provide a composite arrangement which offers advantages that no single transistor or pair can do.

## Set 20: Transistor pairs—

### High current-gain pairs—1

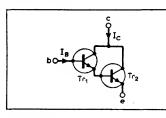

Darlington pair

**Components** Tr<sub>1</sub>: BFR41 Tr<sub>2</sub>: TIP3055

Description and characteristics A Darlington pair as shown above is a frequently used two-transistor circuit, the purpose being to obtain high gain through cascading two transistors. Because large currents are obtained in the second transistor one frequently finds this to be a power transistor and that the arrangement is used in many switching applications. As the circuit has only three terminals it can be regarded as a single high-gain transistor. The basic action is that  $I_b$ produces, through  $Tr_1$ , a large base drive for  $Tr_2$ . The total  $I_c$  is the sum of the two collector currents although the contribution of  $Tr_1$  to  $I_c$  will be small if the gain of  $Tr_2$  is large.

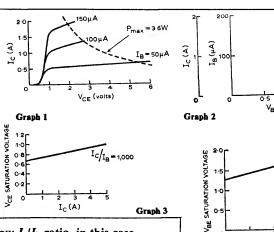

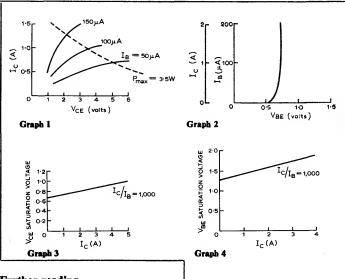

The characteristics obtained for the components quoted are as shown. From graph 1 we obtained an hoe of about 25mS and an hre of about 11,000. Graph 2 shows an hie of around 70. These figures are in line with theory (see reference). Graph 2 also shows the dependence of I<sub>c</sub> on I<sub>b</sub>, the two graphs being indistinguishable because of the scales chosen. For switching applications the value of  $V_{CE}$  is important. V<sub>CE</sub>sat is defined as that V<sub>CE</sub> corresponding to an arbitrarily

low  $I_c/I_b$  ratio, in this case 1,000 (graph 3). With higher  $I_c/I_b$  ratios, corresponding to lower I<sub>B</sub> values the value of V<sub>CE</sub> will be lower. The corresponding graph of V<sub>BE</sub>sat. is shown in graph 4. Graph 5 shows the dependence of h<sub>FE</sub> on I<sub>c</sub>, the drop in h<sub>FE</sub> at high I<sub>c</sub> being due to saturation and that at low I<sub>c</sub> being due to lack of base drive to Tr<sub>1</sub>.

#### Complementary Darlington pair

Components Tr<sub>1</sub>: BFR81 Tr<sub>2</sub>: TIP3055

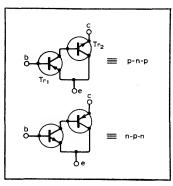

#### Description and characteristics The basic action of this circuit is the same as that of the normal Darlington pair. Note that the circuit in this format is acting as a single p-n-p transistor. An n-p-n version is shown below. It is the input transistor which indicates whether the combination is p-n-p or n-p-n but one can readily check the bias voltages.

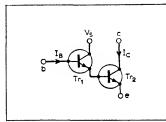

Graph 1 shows the output characteristics: not eminently suitable for a small-signal amplifier, but as the circuit tends to be used for switching applications this is not too serious. We obtained for these components an  $h_{fe}$  of 8,500 approx and an  $h_{oe}$  of greater than 0.1S.

Graph 2 shows  $I_B$  and  $I_c$ against  $V_{BE}$  and these again coincide because of the scale chosen. Note in this case that  $V_{BE}$  during conduction is about 0.7V as opposed to 1.5V for the normal Darlington; this is due to the fact that there is only one junction between b and e. This shows up again in graph 4.

By the same token, the graph of  $V_{CE}$ sat (graph 3) is much the same as that for the normal Darlington.

Graph 5 again has much the same shape as that for the normal Darlington though with a lower maximum value, which is in line with the reduced  $h_{FE}$ .

Further reading

Burwen, E. High-gain triple Darlington has low saturation voltage, *Electronics*, 3 Oct., 1974.

#### Reference

Ajdler, J. Transistor circuits, *Electronic Engineering* 1965, p.757. See also p.338 and p.112, same year.

## Set 20: Transistor pairs-2

### High current-gain pairs—2

Components Tr<sub>1</sub>: BFR41 Tr<sub>2</sub>: TIP3055

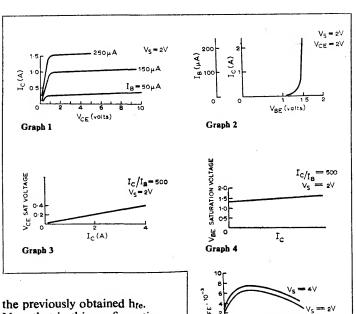

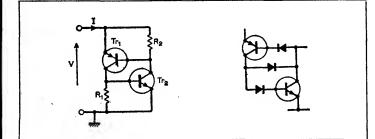

Performance and description The Darlington circuits on card 1 are both super  $\beta$  circuits but have the additional charactistic that they only have three terminals and so can be regarded as a single transistor. The circuit shown above also has high gain but has four terminals, three of which can

be regarded as base, emitter and collector, the fourth being connected to a voltage which gives some control over the characteristics. The principal difference in performance of this circuit is that a low saturation voltage is obtained. From graph 1 we obtained an hre of 7,000 and an hoe of 25mS for  $V_8 = 2.0V$ . Characteristics for  $V_8 = 4.0V$ are virtually identical. Graph 3 shows the low Vcesat values obtained, slightly lower values being obtained for  $V_{s} = 4.0V.$

Graph 4 shows the expected V<sub>BE</sub>sat values around 1.5V since two base-emitter junctions are between b and e. Again slightly lower values are obtained for  $V_s = 4.0V$ . The graph of  $h_{FE}$  is shown in graph 5, the figures being in line with

Note that in this configuration Tr<sub>1</sub> will have supply voltage V<sub>s</sub> across it and will normally require a current-limiting resistor in its collector lead.

#### **Components** Tr<sub>1</sub>: BFR81

Tr<sub>2</sub>: TIP3055

#### **Circuit description**

First given by Baxandall and Shallow, this circuit has a gain producing action similar to that of the Darlington's and the circuit overleaf. Base current to Tr<sub>1</sub> produces large base drive to Tr<sub>2</sub> thereby giving large gain. In this case, however, bias  $(I_1)$ must be provided for correct action. As there are more than three terminals it cannot be considered as identical to a single transistor, and it displays some characteristics

that one does not obtain with single transistors. In particular, one obtains collector current Ic in the absence of any  $V_1$ , this being due to the action of  $I_1$ . The characteristics shown were obtained with a  $V_{CE}$  of 1V and exhibit an overall gm of 6A/V, obtained at  $V_1$  of zero. The components used were chosen for comparison with the other super  $\beta$  pairs but certain features would dictate other choices. For example, the circuit simulates a p-n-p transistor whilst having an n-p-n output stage. In monolithic i.cs with lateral

transistors, n-p-n transistors have low gain so that  $Tr_1$ would dictate the overall gain. As  $Tr_1$  has a very low voltage across it, viz  $V_{be}$  of  $Tr_2$ , then Tr<sub>1</sub> can be made to have high gain-see MC1538R. When used as shown above right, the circuit exhibits extremely high output resistance which, allied to the high current gain, gives large voltage gain. The reason for this is that  $v_1 = v_3 + v_2 + v_{in}$  and as  $v_3$  and  $v_2$  cancel, both being base-emitter voltages, then  $v_1 = v_{in}$  and the current in  $R_L$ is thus defined by  $I_1$  and the current in R, no matter the

value of  $R_L$ .

The circuit therefore, must have a large output resistance. Values as high as  $50M\Omega$  have been quoted.

#### Further reading

Baxandall, P. J. and Shallow, E. W. Constant-current source with unusually high internal resistance and good temperature stability; Electronics Letters vol. 2, p.351 1966. Jarger, R. C. A high output resistance source, IEEE Journal of Solid-State Circuits, Aug. 1974, pp.192-4.

## Set 20: Transistor pairs-

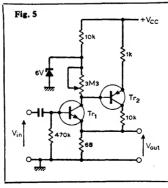

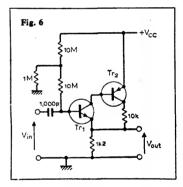

## **Cascode amplifier**

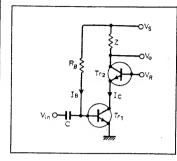

#### **Circuit description**

Tr<sub>1</sub> is a common-emitter amplifier which is feeding Tr<sub>2</sub> in common-base mode. The load on Tr<sub>1</sub> is therefore a near short-circuit a.c.-wise. In addition, the current gain of Tr<sub>2</sub> is near unity but its output impedance is high, due to the common-base mode of operation. The combination therefore shows the gain characteristics of a shortcircuited c.e. stage plus the output impedance characteristics of c.b. It is therefore ideally suited for the driving of tuned resonant loads or indeed of any high impedance load.

The basic equations are  $I_c = g_m V_{in}$   $I_c \approx I_L$   $g_m = I_c/26mV$  $V_o = Z_L I_L$

The second equation assumes unity current gain through  $Tr_2$ and the last equation assumes that  $h_{ob}$  (for  $Tr_2$ ) is very low. The net result is  $V_0/V_{1n} = g_m Z_L$

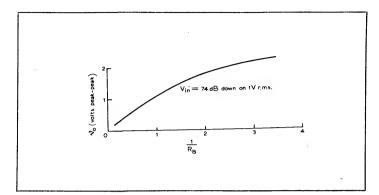

Since  $I_e$  is almost linearly related to  $I_B$ , particularly if  $V_{CE}$  of  $Tr_1$  is constant which it is in this case, then  $g_m$  is controllable by  $R_B$ . The net result is the graph shown. For each result the circuit was retuned for resonance, the change in resonant frequency being around 1.5% over the complete range.

With  $R_B=1M\Omega$ , the resonant frequency was 924kHz and the bandwidth 18.5kHz giving a Q of 50. V<sub>R</sub> is not critical—it is only required to produce correct transistor action. In these results it was 3V. A 1.5-nF supply decoupling capacitor was necessary. Note that the graph represents Components  $Tr_1$ ,  $Tr_3$ : BFR41  $V_s$ : 10V Z: 660mH coil plus stray capacitance plus c.r.o. loading C: coupling capacitor  $R_B$ : see graph  $V_0$ : see graph

a range of voltage gain from 50dB to 71dB and that the range of R<sub>B</sub> is 20:1. The circuit above has two disadvantages viz, it is not a three-terminal device and also requires a biasing voltage. The above circuit suffers from neither of these disadvantages. The circuit is self-biasing provided only that I<sub>c</sub> is less than I<sub>d</sub> by an amount sufficient that the resulting  $V_{gs}$ keeps the bipolar transistor well out of saturation. Typically Vce would need to be in the range 0.2 to 1.0V (though a higher value would be preferable for higher gain). This means that the operating current is restricted to the Id of the f.e.t. with  $V_{gs}$  in the range of -0.2 to -1.0V. In practice the current is defined by some other requirement (drift, matching etc) and is often much less than Idss-the f.e.t. current with  $V_{gs}=0$ (which would give no gain from the bipolar anyway). The f.e.t. will frequently be required to operate near pinch-off. The circuit, above centre, is a less common form which loses the merit of low capacitive feedback. It does, however,

have the merit of increased current capability since the f.e.t. can operate with  $V_{gs} = 0V$ . The circuit right is of a form found as the input of some commercially available differential amplifiers. Each two-transistor block can be regarded as a single transistor and the circuit is then recognisable as a long-tailed pair. The tail uses the high output impedance of the pair to provide an excellent constant-current source the other two pairs being used for their high voltage gain.

Cross references Set 20, cards 4, 10.

## Set 20: Transistor pairs—4

### Long-tailed pair

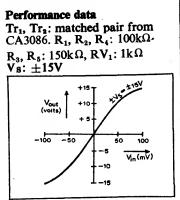

(a) Differential indifferential out

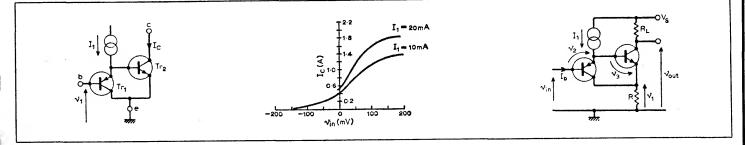

**Circuit description** This emitter-coupled differential amplifier should have a large value for  $R_4$  to provide a high common-mode rejection ratio (c.m.r.r.). This implies that the differential output voltage between collectors for a common signal at the bases, is very small and ideally zero. In general, the output signal depends on the difference between the signals at the

Useful relationships Bipolar transistor collector current related to base-emitter voltage by  $I_C \approx I_S \exp q V_{BE}/kT$  $\frac{dI_C}{dV_{BE}} = \frac{qI_C}{kT} = g_m$ At room temperature  $g_m \approx \frac{I_C}{26} (mA/V)$

Differential input signal can be considered as

transistor bases. Each transistor receives half the signal i.e. the gain to each output is half of that provided by a single transistor under the same conditions.

Gain slope: typically 230. Variation in gain:  $\pm 1\%$ for several choices of CA3086. Reducing R<sub>1</sub>, R<sub>2</sub> by similar ratios will maintain slope at same order of magnitude.

V<sub>in</sub>: 10mV d.c. (20mV) V<sub>out</sub>: 2.39V d.c. (4.79V) i.e. gain slope similar to (a)  $\frac{dV_{out}}{dV_{in}} = 240$

For single-ended output:  $V_{out}$ =voltage between X and ground.

$\frac{\Delta V_{\text{out}}}{\Delta V_{\text{in}}} = \frac{10.28 \text{V} - 9.06 \text{V}}{20 \text{mV} - 10 \text{mV}} = 122.$ i.e. gain is halved.

(c)

$\frac{dV_{xy}}{dV_{in}} = \frac{0.149 - 0.142}{2 - 1} = 0.007$ For single-ended output (terminal X to ground):  $\frac{dV_{out}}{dV_{in}} = 0.0045$ c.m.r.r. improved by trimming R<sub>1</sub>, R<sub>2</sub> for zero balance. Figure of merit is c.m.r.r.

or voltage gain for differential inputs divided by voltage gain for common-mode inputs that is 0.007/230.

theoretically zero—a basic advantage of the differential mode.

$$V_{\rm BE} \approx \frac{kT}{q} \log \left(\frac{I_{\rm c}}{AT^{\rm r}}\right)$$

A is dependent on transistor area. Two transistors on same chip, but different areas, provides a  $V_{BE}$  variation given by

$$\Delta V_{\rm BE} = \frac{kT}{q} \log \left(\frac{A_2}{A_1}\right)$$

Temperature drift is

$$\frac{d\Delta V_{\rm BE}}{dt} = \frac{k}{q} \log \left(\frac{A_2}{A_1}\right) = \frac{\Delta V_{\rm BE}}{T}$$

At room temperature (300K) drift is  $3.3\mu$ V/deg C for each mV of initial offset.

#### Further reading

Thermal variation of the emitter-base voltage of bipolar transistors. Widlar, R. J. *Proc. IEEE* Jan. 1967. Limits of temperature drift in non-compensated d.c. amplifiers. *IEEE Journal of Solid-State Circuits*, Feb. 1970.

Cross reference Set 12, card 10

$v_{C_1} = -g_m \frac{v_{in}}{2} R_C$   $v_{C_2} = -g_m \frac{-v_{in}}{2} R_C$ Differential output given by  $v_0 = v_{C_1} - v_{C_2}$   $= -g_m v_{in} R_C.$ Voltage gain  $A_V$

This single-ended input signal can be considered as the algebraic sum of differential and common-mode signals: i.e.  $v_{in} = v_{in}/2 + v_{in}/2$ and  $\mathbf{0} = \underbrace{v_{in}/2}_{v_{in}/2} - \underbrace{v_{in}/2}_{v_{in}/2}$

common differential mode mode If c.m.r.r. high, effect of common-mode signals negligible. Hence single-ended input equivalent to differential input. For identical transistors the collectors are at equal potentials for common-mode signals. Hence they can be considered connected together

$v_{\rm out} \approx \frac{-v_{\rm in}}{R_{\rm E}} \cdot \frac{R_{\rm c}}{2}$

Note: If  $R_E$  replaced by a constant-current circuit,  $v_{out}(cm)$  can be  $\ll 1$ .  $-g_m \cdot R_C$

$c.m.r.r. = \frac{-g_m \cdot R_c}{R_c/2R_E}$  $= \frac{-g_m R_E}{2}$

#### **Temperature drift**

For a pair of identical transistors, balanced to provide zero difference between the base-emitter voltages of each, then the temperature drift is 159

Set 20: Transistor pairs-

### **Current mirrors**

#### **Description (bipolar)**

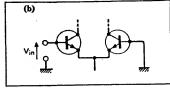

The current mirror is an extremely useful two-transistor circuit extensively used as an integral part of monolithic operational amplifiers to define one current, the mirror current  $I_M$ , in terms of a reference current  $I_R$ . With identical transistors the base-emitter voltages are identical and if  $Tr_2$  has a high current  $I_R$  and  $I_M$

#### Typical data

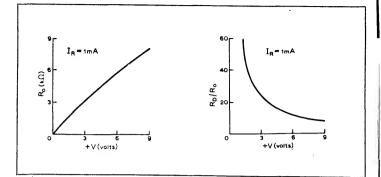

Tr<sub>1</sub>, Tr<sub>2</sub>: part of CA3086 I<sub>R</sub>: 1mA from commercial current generator,  $\pm 0.05\%$ I<sub>M</sub>: measured using 4-digit multimeter. Curves opposite show R<sub>0</sub> and R<sub>D</sub> as functions of +V.

are matched, to a first order. Any matched pair of n-p-n transistors may be used but those on a single chip are preferred; the variable temperature sensitivity of discrete device reduces reliability of the circuit. An important requirement in many applications of the current mirror is a high output resistance. The left-hand graph above shows that the static

output resistance  $(R_0 = V/I_M)$ increases with V for a given reference current value. However, the right-hand graph shows that whilst the dynamic output resistance  $(R_D = \delta V/\delta I_M)$ also increases with V, the far more rapid rise in  $R_0$  causes the ratio of dynamic to static output resistance to fall rapidly with increasing V. Hence, a compromise must be made between the values of  $R_0$  and  $R_{\rm D}$  to be used with a given value of  $I_{\rm M}$ .

For currents in the microamp range the output resistance of the current mirror can be increased by inserting a negative feedback resistor in the emitter lead of  $Tr_2$ .

For higher current requirements, transistors on the same chip can be connected in parallel to increase the junction areas.

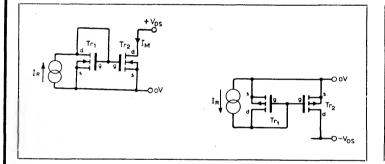

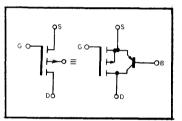

#### Description (m.o.s.)

Current mirror circuits can also be produced using m.o.s. transistors, the basic form using n-channel devices shown above left. Transistor Tr<sub>1</sub> is diode-connected performing as a transistor with 100% feedback. Thus its drain current is still controlled by its gatesource voltage V<sub>GS</sub>, i.e.  $I_{\rm D} \approx g_{\rm ss} V_{\rm gs}$  where  $g_{\rm ss}$  is the forward transconductance. Forcing a current IR into this diode-connected transistor causes VGS to rise until a state of equilibrium is attained when  $Tr_1$  sinks the reference current. The gate-source voltage of Tr<sub>2</sub>

is identical to that of  $Tr_1$ , due to the parallel connections. Hence if both have identical characteristics,  $Tr_2$  is also capable of sinking an identical current, the mirror current  $I_M$ . A reasonably good degree of matching can be obtained between the n-channel devices on a monolithic chip, the mirror current being typically within 10% of the reference current.

A current mirror using monolithic p-channel i.g.f.e.ts, shown centre left, provides better performance than the n-channel type due to the ability to provide much closer

matching of the characteristics of p-channel devices. Such a circuit provides an  $I_M/I_R$  ratio which is to a first order independent of  $V_{DS}$ , as shown centre right. The graph above right shows that the normalized ratio of  $I_M/I_R$  is within 1% of its nominal value over a wide range of ambient temperatures and I<sub>R</sub> values.

#### Further reading

Jaeger, R. C. High output resistance current source, *IEEE Journal of Solid-State Circuits*, pp.192-4, August, 1974. RCA Solid State Databook SSD-201B, pp.183-8 and 213-25, 1974. Hart, B. L. Bidirectional Wireless World, vol. 76, 1970, pp.511-4. Hart, B. L. Bidirectional current source, Electronics Eng. pp.39-41, July, 1974.

Cross references Set 3, card 9. Set 6, card 4. Set 9, card 5. Set 10, cards 1, 3, 7. Set 12, cards 4, 7. Set 15, card 6. Set 16, card 1.

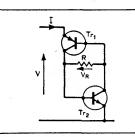

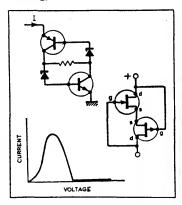

### **Complementary switching transistors**

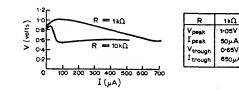

#### Circuit description The arrangement of the complementary pair of transistors, with or without the resistor R, or connected between two other points, is a frequently used combination (see cross refs.). With the resistor R as shown, the circuit acts over a portion of its I-V characteristics as a negative resistance, of value -Rapproximately. Graphs obtained are shown for values of 1k and 10k $\Omega$ .

#### Components Tr<sub>1</sub>: BFR81, Tr<sub>2</sub>: BFR41 R: 1k. $10k\Omega$

$\mathbf{R}: \mathbf{1}\mathbf{k}, \mathbf{10}\mathbf{k}\mathbf{\Omega}$

#### Performance

Slope in negative resistance region  $0.75k\Omega$  and  $8k\Omega$  for  $R=1k\Omega$  10k $\Omega$  respectively (see graph).

Initially with low I, V may be considered as  $V_{EB_1} - V_R + V_{BE_2}$ . As V<sub>R</sub> is low initially V is the sum of the two exponential emitter-base voltages. As I increases these two voltages tend to 0.6V but V<sub>R</sub> continues to rise and because of the minus sign V starts to fall, at a value slightly less than 1.2V. The fall continues (negative resistance region) until both transistors saturate. At this point we can no longer assume that all the current is passing

through both collectors and R and we are best to view V as being  $V_{\rm EC_1} + V_{\rm R} + V_{\rm CE_2}$ . Since the two transistor voltages are relatively fixed, V then starts rising again. The value of the trough is given by  $V_{\rm EC_1}$ sat +  $V_{\rm BE_2}$ sat  $\approx V_{\rm BE_2}$ sat. The voltage range of the circuit is readily increased by the modification shown opposite with Zener diodes appropriate to the application. These circuits are described as being open-circuit stable, i.e. for any current drive there is a unique voltage. The dual of this is the voltage driven, short-circuit-stable device. An

f.e.t. realization of this is shown with the corresponding characteristic (see Further reading).

10 kΩ

0.91

3 µ A

0.58

60µA

#### **Circuit description**

The circuit shown overleaf, with  $R = \infty$ , is the basis of simulated thyristors, silicon controlled switches and simulated unijunction transistors. The action, with  $R = \infty$ , can be deduced from the V-I graph shown, bearing in mind that the negative resistance slope is now  $-\infty$ . Alternatively, the circuit above can be considered as follows. Initially Tr<sub>1</sub> and Tr<sub>2</sub> are in the non-conducting state. A positive voltage of about 0.7V on the base of  $Tr_2$  causes that transistor to conduct and lower its collector voltage. This causes

Tr<sub>1</sub> to conduct and providing Tr<sub>1</sub> and Tr<sub>2</sub> produce sufficient current through R<sub>2</sub> and R<sub>1</sub> respectively to keep the transistors conducting, then the action is self-sustaining with a voltage of approximately one  $V_{BE}$  across the circuit. The circuit can thus be used as a switch, triggered by a suitable voltage at either base. With  $R_1 = R_2 = 1 k \Omega$  a value of 1.3mA for I was found to be the minimum which would maintain conduction. This value is as expected as the current I will split fairly evenly between Tr<sub>1</sub> and R<sub>1</sub> and Tr<sub>2</sub> and R<sub>2</sub>. Since approximately

0.65V is required at the base of each transistor to maintain conduction, it will be provided by 0.65mA in each path. For high-speed switching it is important to prevent the transistors from saturating. Addition of the anti-saturation diodes shown prevents the collector voltages from dropping below VBE. The base lead diodes are not essential. Increasing R<sub>1</sub> increases the trigger voltage necessary and reduces the effect of trigger point transients. Transients in the supply line give rise to false triggering due to rate effect. This can be reduced as R<sub>2</sub> is reduced although this increases the holding current necessary.

#### **Further reading**

G.E. Transistor Manual. Sharma, S. M. Currentcontrolled negative resistance circuit. *Int. J. Electronics*, 1974, vol. 37, pp.209-18. Negative resistance shown in dual f.e.t. device, *Electronics*, April 18, 1974, p.5E. Cross references Set 10, card 5. Set 8, card 3. Set 6, card 9. Set 3, card 4.

## Set 20: Transistor pairs—6

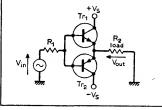

### **Complementary emitter-follower**

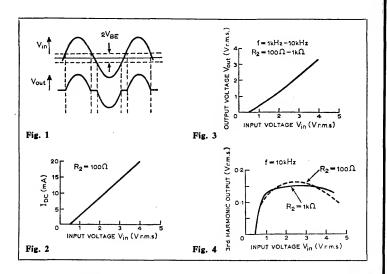

**Circuit description** The basic circuit comprises a complementary n-p-n/p-n-p pair operating under class-C bias, and is the basis for many audio power/amplifiers. When a positive-going input signal exceeds about 0.7V, transistor Tr<sub>1</sub> will turn on, increasing its collector current which develops a voltage across the load R<sub>2</sub>, but with a voltage gain of less than unity. At the same time Tr<sub>2</sub> is biased off. Similarly, a negative-going input signal turns Tr<sub>2</sub> on and Tr<sub>1</sub> off, and the circuit thus provides bidirectional currents through the emitter load. The base-emitter diode characteristic is non-linear at low voltages. resulting in cross-over distortion (approximately  $2V_{BE}$ ) across the load. The resulting distortion on a sine wave input is shown in Fig. 1. Without an additional bias network, the effect of this distortion can be minimized by ensuring that  $V_{\rm S} \gg V_{\rm BE}$ . Using both positive and negative power supplies permits operation down to zero frequency. For a single supply a capacitor is required in series with the load, to provide the base and collector currents of Tr<sub>2</sub> during negative-going input signals.

#### **Component changes**

$R_2$ : Range from 100 to  $1k\Omega$ . Variation in gain minimal. Frequency: Up to 30kHz, little difference from lower frequency operation. Variation of mean current with input level in Fig. 2.  $R_1$ : Chosen to suppress parasitic oscillations. Alternative may be to keep interconnections very short to minimize series inductance.

#### Typical data

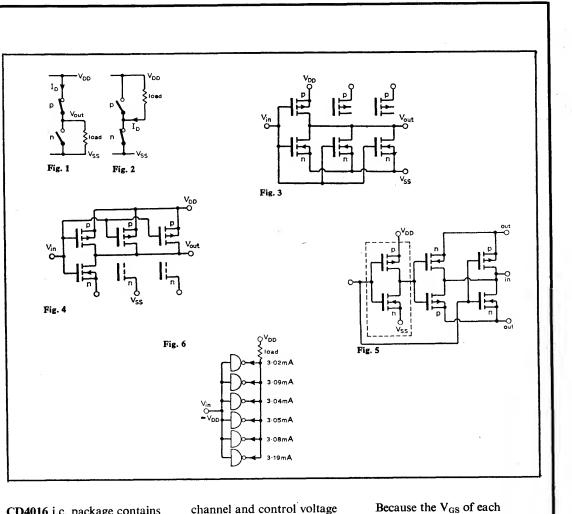

$V_s: \pm 6V$   $T_1: BFR41, T_2: BFR81$   $R_1: 330\Omega, R_2: 1k\Omega$ Signal frequency: 1kHz Fundamental/3rd harmonic output/input shown on graphs

#### Effect of bias (Figs. 5 & 6) **R**<sub>B</sub> varied until transistors just on the point of conduction. Graph shows 3rd harmonic distortion optimized by R<sub>B</sub>. The above is a basic method of biasing to ensure class B or AB operation. Diodes $D_1$ , $D_2$ may be chosen to achieve temperature independence of quiescent current. Where increased current gain is needed for high power outputs, the Darlington pair of Fig. 8 (a) and compound emitter followers of (b) and (c) are useful, but may provide more difficult biasing problems.

## Line driver (Fig. 7) Driving $50-\Omega$ cable with line capacitance slows pulse edges.

Fig. 5

Fig. 6

J)

Fig. 7

Improved using complementary pair. Typical fall time  $\leq 100$ ns but dependent on simulated cable capacitance (R<sub>0</sub>: 50 $\Omega$ , C: 3nF, t<sub>F</sub>: 75ns).

#### Further reading

Williams, P. Voltage following, Wireless World, Sept., 1968. Williams, G. E. Practical transistor circuit design and analysis, McGraw-Hill 1973. Markus, T. Electronic circuits manual, McGraw-Hill.

Cross references Set 7, cards 1, 3. Set 20, card 1.

163

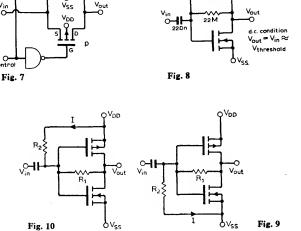

### **CMOS** circuits

#### Description

The c.m.o.s. inverter shown above comprises a p-type and n-type enhancement mode m.o.s. transistor on the same chip.  $V_{DD} - V_{SS}$  may be in the range 3 to 15V. The pair is useful in digital circuits because of well-defined threshold that V<sub>in</sub> must exceed before the device turns on.

n-type: VGS positive for ON p-type: VGS negative for ON Where the output has to sink or source current, the pair can be envisaged as the series switches. Fig. 1 is a source condition, obtained for  $V_{in} =$  $V_{ss}$  and  $V_{out} = V_{DD} - I_d R_o$ where  $R_o$  is the output resistance of p-transistor in the on state. For  $V_{in} = V_{DD}$ , the n-type sinks current for Fig. 2;  $V_{out} = I_d R_o$ .

Basic i.c. package CD4007 contains one inverter and two complementary pairs with the drains unconnected. This permits a variety of interconnections: n-types are paralleled to increase sink current capability, Fig. 3. p-types are paralleled to increase source current capability, Fig. 4. Fig. 5 is a dual bi-directional transmission gate where the two outputs and input may be

interchanged for two inputs and one output. Note that the position of the transistors in the middle pair have been reversed.

The CD4049 package contains six inverters with current drive capability almost an order of magnitude greater than basic package. Parallel connection for increasing current sinking indicates typical current sharing for d.c. condition, Fig. 6.

CD4016 i.c. package contains four analogue switches (transmission gates). Each switch comprises an inverter and a parallel pair of n- and pchannel transistors, Fig. 7. For a threshold of approximately 2V in each channel and control voltage 10V, the gate control voltage of the p-m.o.s. is 0V. If V<sub>in</sub> > 8V, the n-channel will be open, but the gate-source voltage of the p-m.o.s. is -8V(greater than threshold) and signal is switched through.

full supply range can be switched through. 8V d A.C. amplifier (Fig. 9) Best linearity and voltage swing if  $V_{out} = V_{DD}/2$  and this is provided by the resistive connections (Figs. 9 & 10). Supply drain  $\approx 2mA$  for 10V supply.

transistor never equals the

threshold of the transistors, the

#### Further reading

RCA Solid-State Databook Series SSD—203A 1973. Design Ideas with COS/MOS New Electronics, April 30, 1974. I.C. op-amp has CMOS output Electronics, Sept. 19, 1974. Fitchen, F. C. and Ellerbruch, V. G. Linear operation of the MOSFFT complementing pair, IEEE Journal of Solid-State Circuits, Dec., 1971.

Cross references Set 8, card 1. Set 10, card 7. Set 11, card 5. Set 12, card 1.

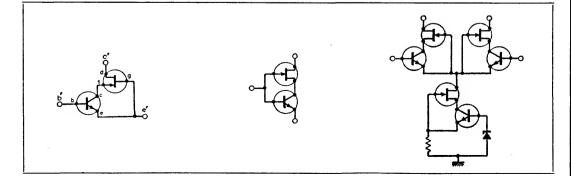

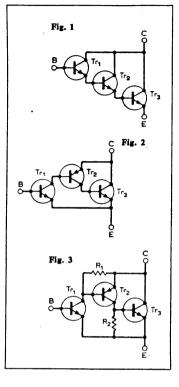

## **Triples & mixed pairs**

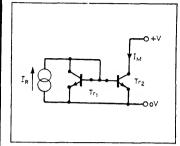

The principle of using transistors in pairs can often be usefully extended to the use of devices in triples, the resulting equivalent transistor having a current gain equal to the product of those of the individual transistors. In all such arrangements, two of which are shown above, the equivalent transistor has the same "polarity" as the input transistor.

The three n-p-n transistors in Fig. 1 act as a compound emitter-follower having a current gain of approximately  $h_{te}$ , for large  $h_{te}$ , and is useful for driving currents of several amps from a driver stage delivering less than a milliamp. The complementary transistor triple in Fig. 2 is useful in voltage regulators as a low-dissipation series element,

the  $V_{BE}$  and  $V_{CE}$  values of the equivalent transistor being the lowest possible for a triple. In this arrangement the temperature coefficient of only one transistor affects the output. The operating current in the input transistor will be very small, reducing its current gain. This effect can remove much of the benefit of using a triple instead of a pair. By using resistors as shown in Fig. 3 the operating currents in the earlier stages are increased and stabilized.

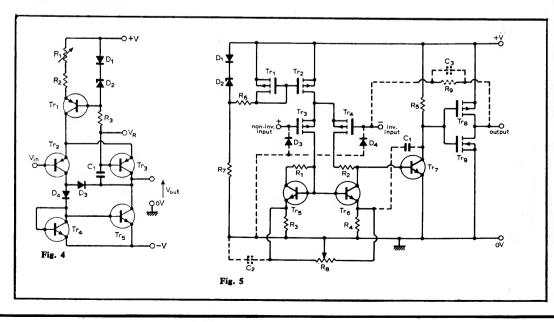

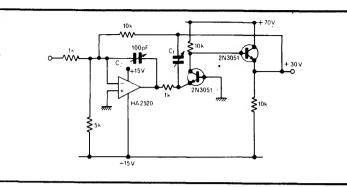

Thinking of the various pairs of devices discussed on other cards as elementary building blocks can prove a powerful method of developing more complicated circuit functions. For example, a long-tailed pair  $Tr_1$ ,  $Tr_2$  and  $Tr_3$  may be used to drive a current mirror  $Tr_4$ and  $Tr_5$  as shown in Fig. 4 to produce a waveform generator which provides a symmetrical

**Typical values.** Supply  $\pm 10V$ , V<sub>R</sub> 0V, R<sub>1</sub> 5k $\Omega$ , R<sub>2</sub> 2·2k $\Omega$ , R<sub>8</sub> 4·7k $\Omega$ , C<sub>1</sub> 33nF, D<sub>1</sub> 1N914, D<sub>2</sub> 1N5234, D<sub>3</sub>, D<sub>4</sub> HP5082 – 2800, Tr<sub>1</sub>, Tr<sub>2</sub>, Tr<sub>3</sub> 2N3546, Tr<sub>4</sub>, Tr<sub>5</sub>  $\frac{1}{2} \times$  SL301-A. triangular output when driven by input pulses. This circuit uses the long-tailed pair to

switch a defined current into two paths; which combined with a closely-matched current mirror permits the capacitor to be charged and discharged at the same rate when the charging current is varied. This concept of mixing elementary pairs of devices can be developed to build a single-supply operational amplifier using bipolar and

m.o.s. transistor pairs, as shown in Fig. 5, having a unity-gain bandwidth of about 10MHz. The operational amplifier, which requires two CA3600E and one CA3046 packages, has three stages. The differential input stage uses two p-channel m.o.s. transistors Tr<sub>3</sub>, Tr<sub>4</sub>, the second stage uses an n-p-n bipolar transistor Tr, and the output stage is a complementary m.o.s. transistor pair Tr<sub>8</sub>, Tr<sub>9</sub>. The zener network, using two diode-connected transistors  $D_1$ ,  $D_2$  of the CA3046, feeds a p-channel current mirror Tr<sub>1</sub>,  $Tr_2$  that establishes a 400 $\mu$ A constant current in the input

stage. This differential-input amplifier is loaded by four resistors,  $R_1$  to  $R_4$ , and a bipolar current mirror, Tr<sub>5</sub>, Tr<sub>6</sub>, to provide optimum balance, any voltage offset being nulled with the potentiometer  $R_8$ . The current in the second stage. determined by R5, is adjusted to equal the 400- $\mu$ A first-stage current to provide similar negative and positive slew rates. The output stage is biased as a class-A amplifier by  $R_5$  and may be driven to within a few millivolts of the ground rail. The overall voltage gain varies inversely with the load resistance which, as with a monolithic operational amplifier, would have a value

of about  $2k\Omega$ . Compensation requires inclusion of the feedback capacitor  $C_1$ , with  $C_2$ added when using the operational amplifier as a unity-gain follower. In this configuration, R<sub>9</sub> and C<sub>3</sub> should be added to avoid the possibility of latch up and D<sub>3</sub> and D<sub>4</sub> added to the inputs to prevent negative-going input signals exceeding about 700mV which could also cause latch up. Typical values are: V+15V;  $R_1, R_2, R_3, R_4 200\Omega \pm 1\%;$  $R_{5} 20k\Omega \pm 1\%$ ;  $R_{6} 11k\Omega \pm 1\%$ ;  $R_7 7.5k\Omega \pm 1\%$ ;  $R_8 10k\Omega$ ;  $R_{9} 1k\Omega; C_{1} 39pF; C_{2} 300pF;$ C<sub>3</sub> 150pF; D<sub>3</sub>, D<sub>4</sub> 1N914.

#### **Further reading**

Williams, P. Voltage Following, Wireless World, vol. 74, 1968, pp. 295-8. Nowicki, J. R. Compound transistor connections, *Electronic Engineering*, September, 1971, p.63. Burwen, E. High-gain triple Darlington has low saturation voltage, *Electronics*, Oct. 3, 1974.

## Pot pourri

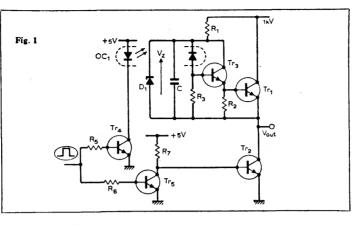

## n-n-p/p-n-p simulation at high voltage

Optical couplers are used to provide fast high voltage switching with a simulated complementary pair. Transistors  $Tr_1$  and  $Tr_2$  are high-voltage n-p-n types:  $Tr_1$  is on when  $Tr_2$ is off and vice versa. With  $Tr_1$ off, C charges to  $V_Z$ , storing charge. This is used to turn  $Tr_1$ on fast when the optical coupler operates.

Optical coupler provides the polarity inversion when  $Tr_4$  and  $Tr_5$  are driven by 5V pulses.

r<sub>3</sub>, r<sub>4</sub>, r<sub>5</sub>: 2N2222 R<sub>1</sub>: 270kΩ (10W), R<sub>3</sub>: 1kΩ R<sub>3</sub>: 100Ω, R<sub>4</sub>: 47Ω R<sub>5</sub> R<sub>6</sub>: 680Ω, C: 10nF D<sub>1</sub>: 6.8V zener, OC1: Monsanto MCO1 Rise and fall times of around 2us are claimed for

components used.

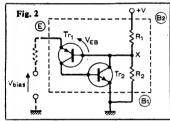

#### Unijunction from bipolar pair

Tr<sub>1</sub>: 2N4126, Tr<sub>2</sub>: 2N4124 R<sub>1</sub>, R<sub>2</sub>: 4.7k $\Omega$ , V: +3 to 25V Because the collector current of Tr<sub>1</sub> is the base current of Tr<sub>2</sub> and vice versa, then any change of current provides a positive feedback action. B<sub>1</sub>, B<sub>2</sub> and E are the equivalent unijunction terminals. When E is open-circuit

$V_{\rm x} = R_2 V/(R_1 + R_2).$

When the potential at E exceeds  $V_{EB}$  and  $V_X$ , both transistors saturate, and  $R_a$  is short-circuited. This condition is maintained for a potential at E down to  $V_{EB} + V_{CES}$  of  $Tr_2$ . Switching speed depends on maximum frequency of of operation of the transistors. For  $Tr_1$ ,  $Tr_2$  silicon drift of  $V_{EB} < 3mV/deg C$ .

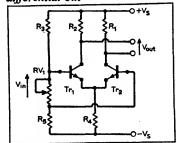

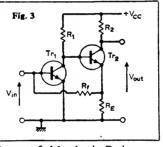

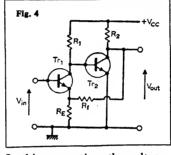

Shunt-series d.c. feedback pair

Current fed back via  $R_f$  is proportional to  $Tr_2$  collector current, and thus the circuit provides current-shunt negative feedback, which primarily controls the overall current-gain.

Effective current gain is  $A_1/(1 + \beta A_1)$  where  $A_1$  is the current gain of the two stages, with  $R_1$  connected between  $Tr_1$  base and ground.  $\beta \approx R_E/R_t$ . For  $\beta < 0.1$ , input resistance is  $R_1/(1 + \beta A_1)$  where  $R_1$  is input resistance without feedback.

Voltage gain  $\approx \frac{R_t}{R_E} \cdot \frac{R_2}{R_S}$

where  $R_s$  is source resistance. Voltage gain can be increased by by-passing  $R_E$ , or by-passing the mid-point of the feedback resistor  $R_t$ . Series-shunt d.c. feedback pair

In this connection, the voltage gain is now mainly affected by the feedback, and the input resistance is increased. Voltage gain is  $A_v/(1+\beta A_v) \approx 1/\beta$  if  $A_v$  is large.  $A_v$  is the product of the gains of each stage, with  $R_F$  connected from  $Tr_2$ collector to ground, and  $\beta = R_E/R_F$ . Input resistance is  $R_1(1+\beta A_v)$ , where  $R_1$  is effective input resistance of the first stage. Note: Biasing networks for those CE-CE amplifiers are not shown.

## Common emitter pairs with composite transistors

Tr<sub>1</sub>, Tr<sub>2</sub>: 2N4355 V<sub>cc</sub>: 15 to 30V Voltage gain  $\approx 100$ Cut-off frequency  $\approx 10$ kHz Input resistance > 200k $\Omega$ By sacrificing voltage gain, a high input impedance can be obtained with the circuit shown. below.

Tr<sub>1</sub>, Tr<sub>2</sub>: 2N4355 V<sub>CC</sub>: +10 to 30V Voltage gain $\approx$ 10 Input impedance: 5M $\Omega$

Further reading for circuits 1-6 1. Mitchell, P. & Robbins, K. Simulating an npn/pnp pair for high voltage switching. *Electronics*, Aug. 22, 1974. 2. Shyne, N. A. Bipolar pair simulates unijunction, *Electronics*, Jan. 24, 1974. 3, 5, 6. Cowles, L. G. Transistor circuit design, Prentice-Hall, 1972.

4. Millman & Halkias, Electronic **Devices** and Circuits, McGraw-Hill, 1967, p.502.

Cross references Set 20, cards 6, 7. Set 12, card 9.

1. The common-base and common-collector pair used in the d.c. feedback pair configuration has a low input impedance, low output impedance and wide bandwidth. Using high voltage transistors it is suitable as a pulse-amplifier to produce very fast positive edges even into capacitive loads (a complementary class B output stage would be needed to make the falling edge equally fast). It lacks d.c. stability but can be combined with a high speed op-amp as shown to give an output slew rate claimed in

the reference to be  $200V/\mu_S$ and full power output of 60V peak to peak at 1MHz. The overall feedback brings the output stage within the loop reducing the offset and drift to that of the op-amp. The latter provides current drive

2. A recent paper has considered the complex behaviour of apparently simple m.o.s. transistors. If the substrate connection is available, then for a p-channel enhancement mode f.e.t. that substrate also acts as the base of a p-n-p transistors with source and drain representing the emitter and collector respectively. To a first-order approximation the devices are

shown to be independent when conducting with the total current being equal to the sum of the individual currents. The m.o.s. action is controlled by a square-law transconductance equation, while the bipolar transistor has a collector current proportional to the base current to a first order of magnitude (low current gain in this example). Thus the waveform in a load resistor connected to a negative supply could be varied by applying an input signal separately or into the c.b. stage but does not need to supply a large voltage swing reducing the demands on its slew rate. The reference describes other more complex circuits capable of extending the small-signal bandwidth to 20MHz and slew-rate to  $1200V/\mu s$  or even higher using special amplifiers. Precautions on layout and decoupling are given.

#### Reference

Bunin, H. Low-cost v.c.o. driver amplifiers really perform if designed right, *EDN*, 1974, Oct. 5, pp. 51-5.

jointly to the gate and substrate terminals. This parallel combination should also be amenable to other waveform processing methods by combining feedback networks with it.

#### Reference

Hart, B. L. and Barker, R. W. J. First-order theory of m.o.s.f.e.t. hybrid-mode operation, *Int.J. Electronics*, 1975, vol. 38, pp. 625-30.

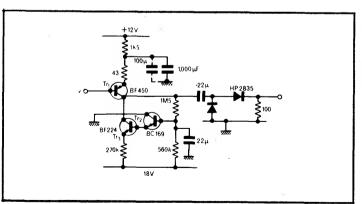

3. This circuit is not strictly a two-transistor arrangement but illustrates how a circuit can be partitioned to reveal familiar pairs. It is a wide band precision rectifier that uses a high output impedance rather than negative feedback to overcome the diode non-linearities. A Darlington pair composed of  $Tr_2$ ,  $Tr_3$  is modified to remove the collector of Tr<sub>2</sub> from the circuit output, by returning it to ground. This leaves Tr<sub>3</sub> providing a low-capacitance constant-current sink. D.c. negative feedback defines the operating points (with negligible loading because

the current gain is high allowing high-value resistors. The  $43\Omega$  resistor defines the circuit transconductance and Schottky diodes maintain

the bandwidth with minimum p.d. and hence non-linearity at low levels. Where large electrolytics are needed to extend low frequency response (20Hz is quoted in reference) then parallel tantalum capacitors are added to maintain low impedance at high frequencies. The source has to be capable of carrying the base current of  $Tr_1$ . The reference indicates the upper cut-off frequency as 80MHz with good accuracy to 10MHz, and good linearity and repeatability for 200mV r.m.s. full-scale.

#### Reference

Knott, K. F. Sensitive wideband linear a.c.-d.c. converter, *Proc.IEE*, 1975, vol. 122, pp. 249-52.