## Analog Engineer's Circuit: Amplifiers

SBOA221A-January 2018-Revised February 2019

# Window comparator circuit

#### **Design Goals**

| Input             |                   | Output            |                   | Supply          |                 |                  |

|-------------------|-------------------|-------------------|-------------------|-----------------|-----------------|------------------|

| V <sub>iMin</sub> | V <sub>iMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | V <sub>cc</sub> | V <sub>ee</sub> | V <sub>ref</sub> |

| 0V                | 5V                | 0V                | 36V               | 5V              | 0V              | 2.5V             |

| V <sub>L</sub> (Lower Threshold) | V <sub>H</sub> (Upper Threshold) | Upper to Lower Threshold Ratio |

|----------------------------------|----------------------------------|--------------------------------|

| 1.66V                            | 3.33V                            | 2                              |

#### **Design Description**

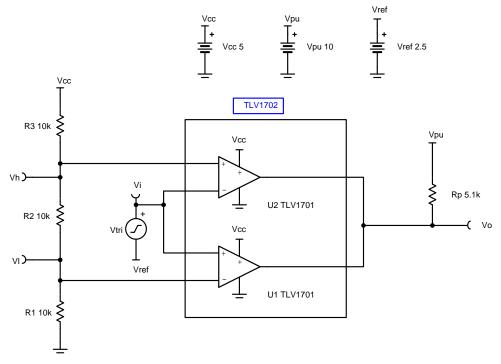

This circuit utilizes two comparators in parallel to determine if a signal is between two reference voltages. If the signal is within the window, the output is high. If the signal level is outside of the window, the output is low. For this design, the reference voltages are generated from a single supply with voltage dividers.

#### **Design Notes**

- 1. The input should not exceed the common mode limitations of the comparators.

- 2. If higher pullup voltages are used,  $R_p$  should be sized accordingly to prevent large current draw. The TLV1701 supports pullup voltages up to 36V.

- 3. Comparator must be open-drain or open-collector to allow for the ORed output.

www.ti.com

#### **Design Steps**

1. Define the upper (V\_H) and lower (V\_L) window voltages.

$$V_{H} = V_{cc} \times \frac{R_{1} + R_{2}}{R_{1} + R_{2} + R_{3}} = 3.33 V$$

$$V_{L} = V_{cc} \times \frac{R_{1}}{R_{1} + R_{2} + R_{3}} = 1.66 V$$

$$\frac{V_{H}}{V_{I}} = 1 + \frac{R_{2}}{R_{1}} = \frac{3.33V}{1.66V} = 2$$

2. Choose resistor values to achieve the desired window voltages.

$$rac{V_{H}}{V_{L}} = 1 + rac{R_{2}}{R_{1}} = 2$$

, so  $R_{2} = R_{1}$

$R_1 = R_2 = 10 k\Omega$  (Selected standard values)

$$R_3 = \frac{R_1 \times V_{cc}}{V_L} - (R_1 + R_2)$$

$R_3 = \frac{10 k \Omega \times 5 V}{1.66 V} -$  20k $\Omega =$  10 .12 k $\Omega$   $\thickapprox$  10k $\Omega$  (Standard Value)

#### **Design Simulations**

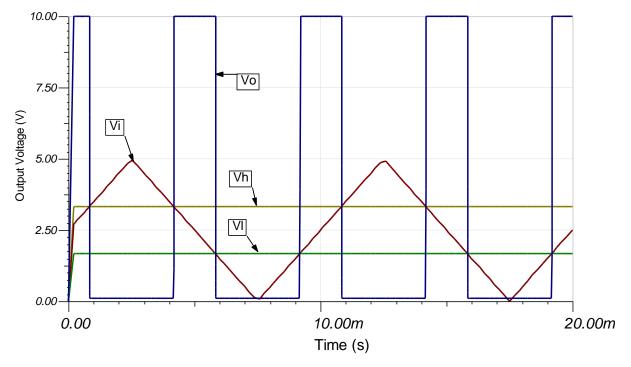

#### **Transient Simulation Results**

#### www.ti.com

#### **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See the circuit SPICE simulation file SBOC516.

See TIPD178, www.ti.com/tool/tipd178.

### **Design Featured Op Amp**

| TLV1702                    |                          |  |  |  |

|----------------------------|--------------------------|--|--|--|

| V <sub>cc</sub>            | 2.2V to 36V              |  |  |  |

| V <sub>inCM</sub>          | Rail-to-rail             |  |  |  |

| V <sub>out</sub>           | Open Collector (36V Max) |  |  |  |

| V <sub>os</sub>            | 2.5mV                    |  |  |  |

| l <sub>q</sub>             | 75µA/Ch                  |  |  |  |

| I <sub>b</sub>             | 15nA                     |  |  |  |

| Rise Time                  | 365ns                    |  |  |  |

| Fall Time                  | 240ns                    |  |  |  |

| #Channels                  | 1, 2, 4                  |  |  |  |

| www.ti.com/product/tlv1702 |                          |  |  |  |

#### **Revision History**

| Revision | Date          | Change                                                                                                                                 |

|----------|---------------|----------------------------------------------------------------------------------------------------------------------------------------|

| A        | February 2019 | Downscale the title and changed title role to 'Amplifiers'.<br>Added links to circuit cookbook landing page and SPICE simulation file. |