# CHAPTER 6 Signal Amplifiers

- Section 6-1: Audio Amplifiers

- Section 6-2: Buffer Amplifiers/Driving Cap Loads

- Section 6-3: Video Amplifiers

- Section 6-4: Communications Amplifiers

- Section 6-5: Amplifier Ideas

- Section 6-6: Composite Amplifiers

This page intentionally left blank

# CHAPTER 6 Signal Amplifiers

Walt Jung, Walt Kester

SECTION 6-1 Audio Amplifiers Walt Jung

## Audio Preamplifiers

Audio signal preamplifiers (preamps) represent the low-level end of the dynamic range of practical audio circuits using modern IC devices. In general, amplifying stages with input signal levels of 10 mV or less fall into the preamp category. This section discusses some basic types of audio preamps, which are:

*Microphone*—including preamps for dynamic, electret, and phantom-powered microphones, using transformer input circuits, operating from dual and single supplies.

*Phonograph*—including preamps for moving magnet and moving coil phono cartridges in various topologies, with detailed response analysis and discussion.

In general, when working signals drop to a level of  $\approx 1$  mV, the input noise generated by the first system amplifying stage becomes critical for wide dynamic range and good signal-to-noise ratio. For example, if internally generated noise of an input stage is 1  $\mu$ V and the input signal voltage 1 mV, the best signal-to-noise ratio possible is just 60 dB.

In a given application, both the input voltage level and impedance of a source are usually fixed. Thus, for best signal-to-noise ratio, the input noise generated by the first amplifying stage must be minimized when operated from the intended source. This factor has definite implications to the preamp designer, as a "low noise" circuit for low impedances is quite different from one with low noise operating from a high impedance.

Successfully minimizing the input noise of an amplifier requires a full understanding of all the various factors that contribute to total noise. This includes the amplifier itself as well as the external circuit in which it is used; in fact, *the total circuit environment must be considered* both to minimize noise and maximize dynamic range and signal fidelity.

A further design complication is the fact that not only is a basic gain or signal scaling function to be accomplished, but *signal frequency response* may also need to be altered in a predictable manner. Microphone preamps are an example of wideband, flat frequency response, low noise amplifiers. In contrast to this, phonograph preamp circuits not only scale the signal, they also impart a specific frequency response characteristic to it. A major part of the design for the RIAA phono preamps of this section is a systematic analysis process, which can be used to predictably select components for optimum performance in frequency response terms. This leads to very precise functioning, and excellent correlation between a computer-based design and measured lab operation.

# **Microphone Preamplifiers**

The microphone preamplifier (mic preamp) is a basic low level audio amplification requirement. Mic preamps can assume a variety of forms, considering the wide range of possible signal levels, the microphone types, and their impedances. These factors influence the optimum circuit for a specific application. Discussed in this section are mic preamps that work with both high and low impedance microphones, both with and without phantom power, and with transformer input stages.

#### Single-Ended, Single-Supply High-Impedance Mic Preamp

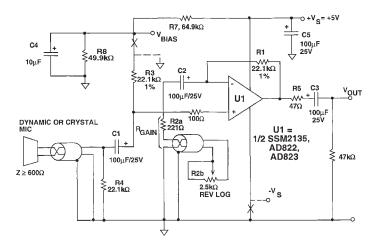

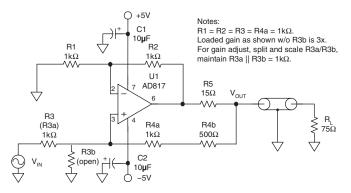

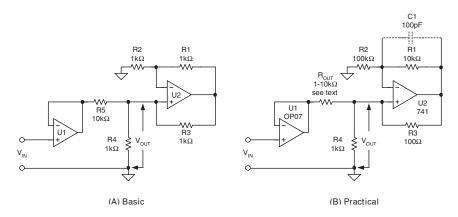

A very simple form of mic preamp is shown in Figure 6-1. This is a noninverting stage with a single-ended input, most useful with high-impedance microphones such as dynamic and piezoelectric types. As shown, it has adjustable gain of 20 dB–40 dB via  $R_{GAIN}$ , and is useful with audio sources with 600  $\Omega$  or greater source impedances.

Figure 6-1: A single-ended, single-supply mic preamp

The U1 op amp can greatly affect the overall performance, not only in general amplification terms but also in suitability for single supply operation (as shown here). In terms of noise performance, the U1 device should have a low input noise with  $\geq$ 500  $\Omega$  sources, with the external circuit values adjusted so that the source impedance (microphone) dominates the overall source resistance.

For very low noise on 5 V supplies, very few devices are suitable. Among these the dual SSM2135 or the OP213, and AD822/AD823 stand out, and are recommended as first choices. For very low power, minimal quiescient current parts like the AD8541 can be considered. Many other low noise devices can also work well in this circuit for total supply voltages of 10 V or more, for example the OP275, and OP270/OP470 types. The circuit is also easily adapted for dual supply use, as noted below.

In this circuit, gain-determining resistors R1||R2 (where R2a + R2b =  $R_{GAIN}$ ) are scaled such that their total resistance is less than the expected source impedance, that is 1 k $\Omega$  or less. This minimizes the contribution of the gain resistors to input noise, at high gain. As noted, gain of the circuit is adjusted in the feedback path via resistor R<sub>GAIN</sub>. In a system sense, control of a microphone or other low level channel signal level is preferably done *after* it has undergone some gain, as the case here. R<sub>GAIN</sub> can of course be a fixed value.

Because of the single supply operation, input/output coupling is via polar capacitors, namely C1, C2, and C3. C4 is a noise filter, and C5 a bypass. For lowest noise in the circuit, the amplifier biasing must also be

*noiseless*; that is, free from noise added directly or indirectly by the biasing (see Reference 1). Resistors with dc across them should have low excess noise (film types), or be ac-bypassed. Thus R1, R2, R3, R4, R7, and R8 are preferably metal films, with R7–R8 bypassed. A 2.2 V bias provided from R7–R8 biases the output of U1 to near midsupply. If higher supply voltage is used, R7–R8 can be adjusted for maximum output with a particular amplifier. For example, with low bias current, rail-rail output op amps, R7 and R8 should be high, equal values ( $\geq 100 \text{ k}\Omega$ ).

While the OP213 or SSM2135 for U1 is optimum when operating from lower impedance sources, FET input types such as the AD82x families (or a select CMOS part) is preferable for high impedance sources, such as crystal or ceramic mics. To adapt the circuit for this, R3 and R4 should be  $1M\Omega$  or more, and C1 a 0.1  $\mu$ F film capacitor.

Bandwidth using the OP213 or SSM2135 is about 30 kHz at maximum gain, or about 20 kHz for similar conditions with the AD822 (or AD820). Distortion and noise performance will reflect the U1 device and source impedance. With a shorted input, an SSM2135 measures output noise of about 110  $\mu$ V rms at a gain of 100, with a 1 kHz THD + N of 0.022% at 1 V rms into a 2 k $\Omega$  load. The AD820 measures about 200  $\mu$ V rms with 0.05% THD + N for similar conditions. For both, the figures improve at lower gains.

The circuit of Figure 6-1 is a good one if modest performance and simplicity are required, but requires attention to details. The input cable to the microphone must be shielded, and no longer than required. Similar comments apply to a cable for  $R_{GAIN}$  (if remote).

To adapt this circuit for dual supply use, R3 is returned to ground as noted, plus the bias network of R7, R8, and C4 is eliminated. U1 is operated on symmetric supplies ( $\pm 5$  V,  $\pm 15$  V, and so forth), with the  $-V_s$  rail bypassed similar to  $+V_s$ . Coupling caps C1, C2, and C3 are retained, but must be polarized to matched the amplifier used (or nonpolar types). Although microphones with output impedances of less than 600  $\Omega$  can be used with this circuit, the noise performance will not be optimum. Also, many of these typically require a balanced input interface. Subsequent circuits show methods of optimizing noise with low impedance, balanced output microphones, as suited for professional applications.

#### Electret Mic Preamp Interface

A popular mic type for speech recording and other noncritical applications is the electret type. This is a permanently polarized condenser mic, typically with a built-in common-source FET amplifier. The amplified output signal is taken from the same single ended lead which supplies the microphone with dc power, typically from a 3-10 V dc source.

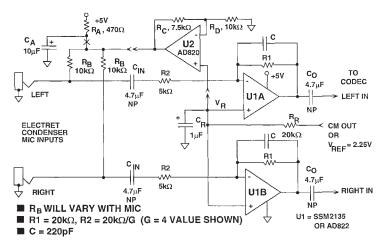

Figure 6-2 illustrates a basic interface circuit that is useful in powering and scaling the output signal of an electret mic for further use. In this case the scaled output signal from this interface is fed into the LEFT and RIGHT inputs of a 5 V supply powered CODEC for digitization and processing. Dc phantom power is fed to the mic capsules by the  $R_A$ - $C_A$ - $R_B$  decoupling network from the 5 V supply, and the ac output signal is tapped off by  $C_{IN}$ -R2, and fed to U1. The  $R_B$  resistors will vary with different mics and supply voltages, and the values shown are typical. For a quiet mic supply voltage, a filtered/scaled  $V_R$  can be generated by the optional U2 connection shown.

Figure 6-2: An electret mic interface for 5 V powered CODECs

The U1 dual scaling amplifier is an SSM2135 or AD822, and is used to normalize the mic signal to either a 1 V rms line level or 100 mV rms mic level typically required by CODEC inputs, and also to low-pass filter it prior to digitization. With a wide variety of electret mics and operating parameters, some signal level scaling is often required.

The scaling gain is simply R1/R2, and R2 is selected to provide a gain "G," to yield 0.1 V rms at the mic inputs of the CODEC, with the rated output from the mic. The U1 stages are inverting, so G can be greater or less than unity, i.e., other than 4 as is shown here, to normalize any practical input signal to an optimum CODEC level. The amplifier's low-pass corner frequency is set by the time constant R1-C, which results in a –3 dB point of 36 kHz. Bias for the U1 stages is provided from the CODEC, via the reference or CMOUT pins, typically a 2.25 V–2.5 V reference voltage. The low frequency time constants  $C_{IN}$ -R<sub>B</sub>/R2 and  $C_{O}$ -20 k $\Omega$  are wideband to minimize LF phase shift. These (nonpolar) capacitors can be reduced to 1 µF or less, for narrowband uses.

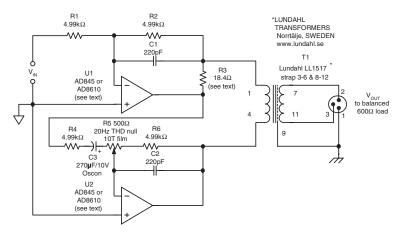

#### Transformer-Coupled Low-Impedance Microphone Preamps

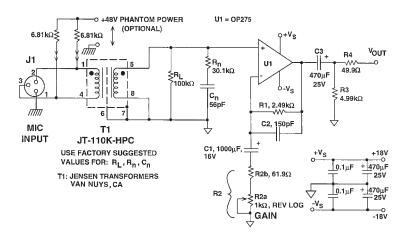

For any op amp, the best noise performance is attained when the characteristic *noise resistance* of the amplifier,  $R_n$ , is equal to the source resistance,  $R_s$ . Examples of microphone preamps that make use of this factor are discussed in this section. They utilize an input matching transformer to more closely optimize an amplifier to a source impedance which is unequal to the amplifier  $R_n$ . A basic circuit operating on this principle is shown in Figure 6-3. In order to select an optimum transformer turns ratio for a given source resistance ( $R_s$ ), calculate the characteristic  $R_n$  of the op amp in use.

Figure 6-3: Transformer input mic preamplifier with 28 dB to 50 dB gain

$R_n$  must first be calculated from the op amp's  $e_n$  and  $i_n$  data as:

$$R_n = \frac{e_n}{i_n}$$

Eq. 6-1

where  $e_n$  is in  $V/\sqrt{Hz}$  and  $i_n$  is in  $V/\sqrt{Hz}$ . A turns ratio for T1 may be calculated as:

$$\frac{N_s}{N_p} = \sqrt{\frac{R_n}{R_s}}$$

Eq. 6-2

where  $N_s/N_p$  is the transformer secondary/primary turns ratio. For the OP275 op amp, the values of  $e_n$  and  $i_n$  are 7 nV/ $\sqrt{\text{Hz}}$  and 1.5 pA/ $\sqrt{\text{Hz}}$ , respectively; thus,

$$R_n = \frac{e_n}{i_n} = \frac{7 \times 10^{-9}}{1.5 \times 10^{-12}} = 4.7 k\Omega$$

Since both  $e_n$  and  $i_n$  vary with frequency,  $R_n$  will also vary with frequency. Therefore, a value calculated for  $R_n$  from the data sheet (such as above) is most accurate at the specified frequency. If the amplifier is to be optimized for a specific frequency, the  $e_n$  and  $i_n$  values should be for that frequency. However, audio amplifiers are wideband circuits, so latitude is due here. When available, a minimum noise-figure plot for the amplifier will allow graphical determination of the optimum source resistance for noise.

For this case, an optimum transformer turns ratio can be calculated to provide the optimum  $R_n$  to the op amp, working from a given  $R_s$ . For example, if  $R_s$  is 150  $\Omega$ , an optimum turns ratio for an OP275 (or other amplifier) with an  $R_n$  of 4.7 k $\Omega$  will be:

$$\frac{N_{s}}{N_{p}} = \sqrt{\frac{R_{n}}{R_{s}}} = \sqrt{\frac{4.7 \times 10^{3}}{1.5 \times 10^{2}}} \approx 5.6$$

Other examples matching these criteria would include OP27 family types.

Transformers are catalogued in fairly narrow and specific impedance ranges, so a unit with a rated secondary impedance in the range of 5 k $\Omega$  to 10 k $\Omega$  will be useful (the amplifier minimum noise impedance is reasonably broad). A suitable unit for this purpose is the Jensen JT-110K-HPC. Note that T1 must be adequately shielded and otherwise suitable for operation in low level environments. The use of the matching transformer allows the circuit to achieve an equivalent input noise (referred to the transformer input) that is only a few decibels above the theoretical limit, or very close to the thermal noise of the source resistance. For example, the thermal noise of a 150  $\Omega$  resistor in a 20 kHz noise bandwidth at room temperature is 219 nV. A real circuit has a higher input referred noise, due to the transformer plus op amp noise.

An additional advantage of the transformer lies in the *effective voltage gain* that it provides, due to the step up turns ratio. For a given circuit total numeric gain,  $G_{total}$ , this reduces the gain required from the op amp U1,  $G_{(U1)}$ , to:

$$G_{(U1)} = \frac{G_{total}}{N_s / N_p}$$

Eq. 6-3

Thus, in the composite circuit of Figure 6-3 gain  $G_{total}$  is the product of the transformer step up,  $N_s/N_p$ , and (R1 + R2)/R1, which is  $G_{(UI)}$ . This has advantages of allowing more amplifier loop gain, thus greater bandwidth and accuracy, lower distortion, and so forth.

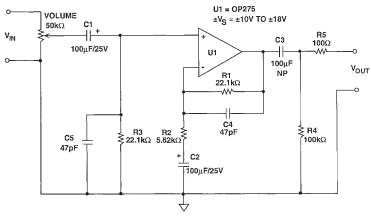

The transformer input example mic preamp stage of Figure 6-3 uses the JT-110K-HPC transformer for T1 with a primary/secondary ratio of about 1/8 (150  $\Omega$ /10 k $\Omega$ ). The op amp section has a variable gain of about 3.3-41 times, which, in combination with the 17.8 dB transformer gain, yields a composite gain of 28 dB to 50 dB (26 to 300 times). Transient response of the transformer plus U1 amplifier is excellent. U1 here is one-half an OP275, operating on ±18 V power. Supplies should be well regulated and decoupled close to U1, particularly with low impedance loads. *Care should be used to operate U1 below maximum voltage rating*. The OP275 is rated for maximum supplies of ±22 V.

For best results, passive components should be high quality, such as 1% metal film resistors, a reverse log taper film pot for R2a, and low ESR capacitors for C1 and C3. Microphone phantom powering (see References 2 and 3) can be used, simply by adding the  $\pm 0.1\%$  matched 6.81 k $\Omega$  resistors and a 48 V dc source, as shown. Close matching of the dc feed resistors is recommended by the transformer manufacturer whenever phantom power is used, to optimize CMR and to minimize the transformer's primary dc current flow (see Reference 4). Note that use of phantom powering has little or no effect on the preamp, since the transformer decouples the CM dc variations at the primary. CMR in an input transformer such as the JT-110K-HPC is typically 85 dB or more at 1 kHz, and substantially better at lower frequencies.

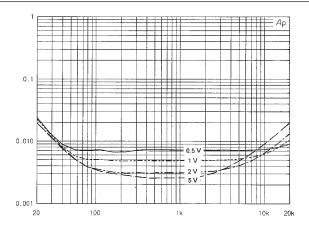

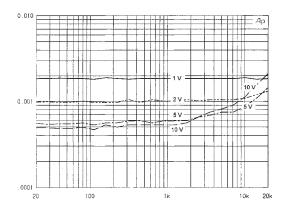

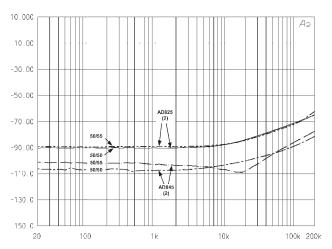

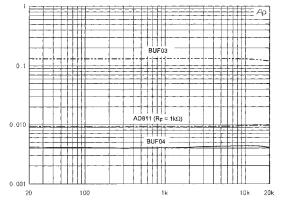

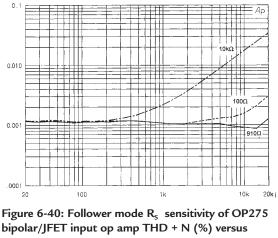

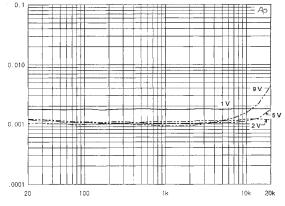

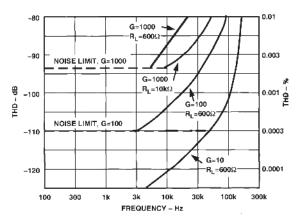

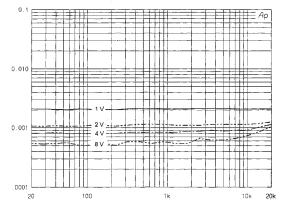

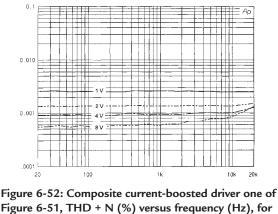

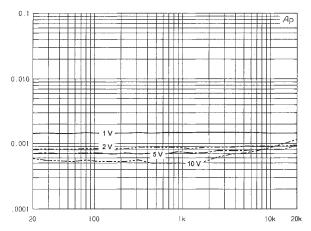

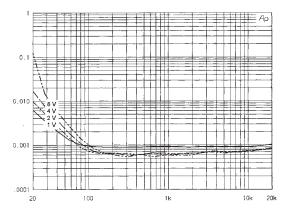

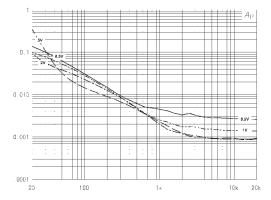

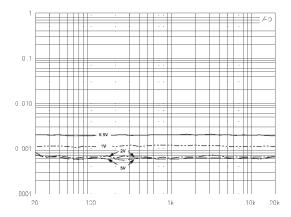

THD + N performance versus frequency of this OP275 mic preamp is shown in the family of curves in Figure 6-4. The test conditions are 35 dB gain, and successive input sweeps resulting in outputs of 0.5, 1, 2, and 5 V rms into 600  $\Omega$ . For these distortion tests as well as most of those following throughout these sections, THD + N frequency sweeps at various levels are used for sensitivity to slewing related distortions (see References 5–7), and output loaded tests are used for sensitivity to load related nonlinearities.

Figure 6-4: Transformer-coupled mic preamplifier THD + N (%) versus frequency (Hz) for 35 dB gain, outputs of 0.5, 1, 2, and 5 V rms into 600  $\Omega$

For the OP275 data shown in Figure 6-4, there are three interest regions, a sub-100 Hz region where distortion is largely transformer-related, a 100 Hz–3 kHz region where distortion is lowest, and a greater-than-3 kHz region where it again rises. For most of the spectrum THD + N is  $\leq 0.01\%$  for medium outputs, and slightly higher at high frequencies.

The -3 dB bandwidth of this circuit is about 100 kHz, and is dominated by the JT-110K-HPC transformer and its termination network, assuming a 150  $\Omega$  source impedance. Conversely, for higher or lower source impedances, the bandwidth will lower or rise in proportion, so application of this circuit should take this into account. For example, capacitor microphone capsules with emitter follower outputs appear as a  $\approx 15 \Omega$  source.

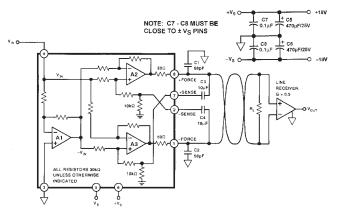

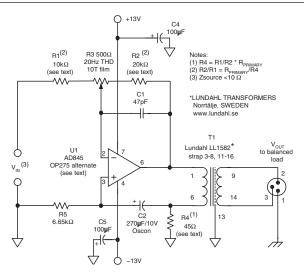

#### Very Low Noise Transformer Coupled Mic Preamp

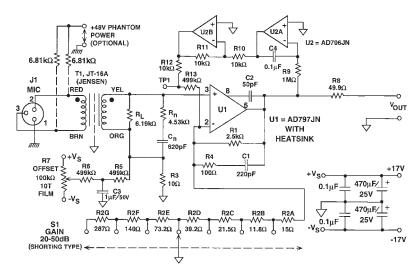

A high performance low noise mic preamp is shown in Figure 6-5, using a lower ratio transformer, the Jensen JT-16A. This transformer has a lower nominal step up ratio of about 2/1, and is optimized for use with

Figure 6-5: Low noise transformer input 20 dB to 50 dB gain mic preamp

#### Chapter Six

lower noise resistance amplifiers such as the AD797. As can be noted from the figure, the general topology is similar to the previous transformer coupled preamp, but some details allow premium levels of performance.

This preamp has a selectable gain feature, using GAIN switch S1 to alter R2 of the feedback network. This varies U1's gain (and thus overall gain) over a range of 20 dB–50dB, making the preamp suitable for a wide range of uses. With the R2 step values shown, gain is selectable in 5 dB increments. This ranges from 50 dB with R2 (total) = 15  $\Omega$ , down to 20 dB with R2 (total) = 588.5  $\Omega$ . The transformer provides a fixed gain of about 5.6 dB.

Inasmuch as the AD797 has high precision as well as low distortion audio characteristics, this circuit can be dc-coupled quite effectively. This has the worthwhile advantage of eliminating large electrolytic coupling caps in the gain network and in the output coupling between U1 and  $V_{OUT}$ . This is accomplished as follows:

The initial device offset of the AD797 is 80  $\mu$ V(max), a factor that allows a relatively simple trim by OFF-SET trimmer R7 to null offset. R7 has a range of ±150  $\mu$ V at the AD797 input, with noise well decoupled by C3. With the preamp warmed up well, and working at a midrange gain setting of 35 dB, the offset can be trimmed out. This is best done with the servo temporarily defeated, by grounding test point TP1. Under this condition the V<sub>OUT</sub> dc level is then trimmed to <1 mV, via R7. This nulls out the residual offset of the AD797, and also ensures that the gain-range network sees minimal dc, which minimizes "pops" with gain changes. The offset shift thereafter with gain is only a few mV, and is of little concern, since the servo circuit of U2A and U2B holds the longer-term dc offset to 100  $\mu$ V or less, with little gain interaction. Note that for the gain-change scheme to work properly, S1 *must* be a shorting (make-before-break) type.

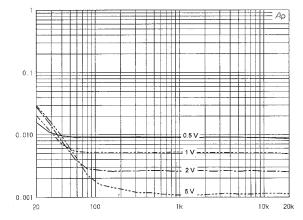

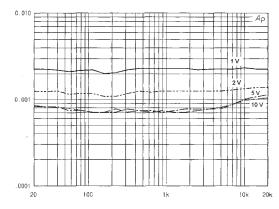

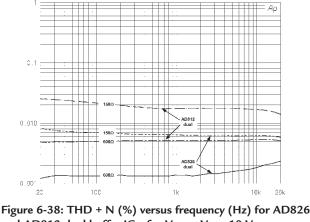

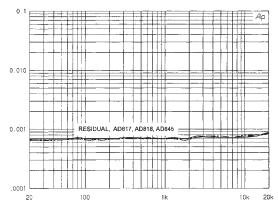

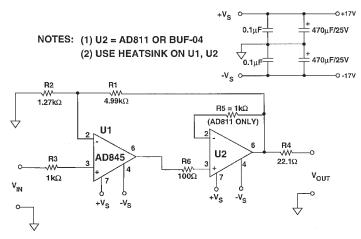

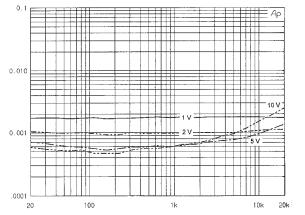

THD + N performance versus frequency of this mic preamp is shown in Figure 6-6, for conditions of 35 dB gain, and successive input sweeps resulting in outputs of 0.5, 1, 2, and 5 V rms into 600  $\Omega$ . From these data it is essentially clear that the only distortion in the circuit is due to the transformer, which is small and occurs only at the low frequencies. Above 100 Hz, the apparent distortion is noise limited, to the highest frequencies.

Figure 6-6: Low noise transformer input mic preamp THD + N (%) versus frequency (Hz) for 35 dB gain, outputs of 0.5, 1, 2, and 5 V rms into 600  $\Omega$

The -3 dB bandwidth of this circuit is just under 150 kHz, and while this is essentially dominated by the JT-16A transformer and termination, bandwidth does reduce slightly at the highest gain (50 dB). Like the previous transformer coupled circuit, this circuit also assumes a 150  $\Omega$  source impedance, and similar application caveats apply.

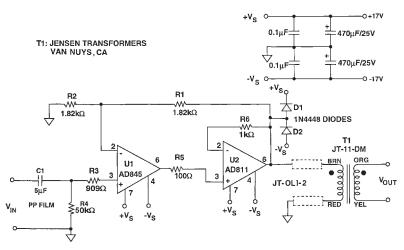

The basic circuit as shown is single-ended with  $V_{OUT}$  taken from R8. However, a transformer can be simply added, as an option for driving balanced lines. When this is done, a nickel core type is suggested, for lowest distortion. One type suitable would be a Jensen JT-11-DM (or similar). It is coupled to the U1 output via a 10  $\Omega$  resistor.

Just as shown the circuit is suited for local, higher impedance loads of  $1 \text{ k}\Omega$  and more. For very high levels of output drive or to drive long lines, a dedicated high current output driver should be used with U1, as generally described in the "Line Drivers" section. This can be most simply implemented by making U1 a composite amplifier, using a AD797 input section plus a follower-type output stage. A good choice for this would be a BUF04 IC, connected between Pin 6 of the AD797 and the remaining circuitry. The buffer will isolate the U1 stage, allowing it to operate with highest linearity with difficult loads. Note also that  $\pm 17 \text{ V}$  supplies won't be necessary with the AD797 unless extreme voltage swings are required. More conventional ( $\pm 15 \text{ V}$ ) supplies will minimize the U1 heating.

#### **References: Microphone Preamplifiers**

- C. D. Motchenbacher, F. C. Fitchen, Low-Noise Electronic Design, Wiley, New York, 1973, ISBN 0-471-61950-7.

- 2. G. Bore, "Powering Condenser Microphones," db, June 1970.

- "ANSI Standard 268-15 (Revision 1987, amendments 1989, 1990, 1991)." American National Standards Institute, 11 W. 42nd St., New York, NY, 10036.

- 4. Steve Hogan, "Standard Mic Input Application," Jensen Transformers Application note JT99-0003, November, 1992.

- W. Jung, M. Stephens, C. Todd, "Slewing Induced Distortion & Its Effect on Audio Amplifier Performance—With Correlated Measurement/Listening Results," presented at 57th AES convention, May 1977, AES preprint # 1252.

- 6. W. Jung, M. Stephens, C. Todd, "An Overview of SID and TIM," Parts 1–3, Audio, June, July, August, 1979.

- 7. Walter G. Jung, Audio IC Op Amp Applications, 3rd Ed., Howard W. Sams & Co., 1987, ISBN 0-672-22452-6.

- W. Jung, A. Garcia, "A Low Noise Microphone Preamp with a Phantom Power Option," Analog Devices AN242, November 1992.

- 9. Walt Jung, "Audio Preamplifiers, Line Drivers, and Line Receivers," within Chapter 8 of Walt Kester, **System Application Guide**, Analog Devices, Inc., 1993, ISBN 0-916550-13-3, pp. 8-1 to 8-100.

- 10. Walt Jung, "Microphone Preamplifiers for Audio," Analog Dialogue, Vol. 28, No. 2, 1994, pp. 12–18.

# **RIAA Phono Preamplifiers**

An example of an audio range preamplifier application requiring equalized frequency response is the RIAA phono preamp. While LP record sales have faded with the establishment of new digital media, for completeness equipment is still designed to include phono playback stages. RIAA preamp stages, as amplifiers with predictable, nonflat frequency response, have more general application connotations. The design techniques within this section are specific to RIAA as an example, but they are also applicable to other frequency dependent amplitude designs in general. The techniques are also useful as a study tool, considering the various approaches advanced to optimize the function of high performance gain with predictable equalization (EQ). These last two points make these discussions useful in a much broader sense.

#### Some RIAA Basics

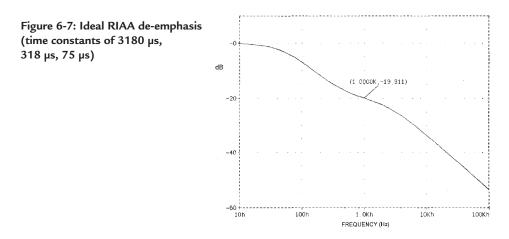

The RIAA equalization curve (see Reference 1) is shown in Figure 6-7, expressed as it is relative to dc. This curve indicates maximum gain below 50 Hz (f1), with two high frequency inflection points. Above f1, the gain rolls off at 6 dB/octave until a first high frequency breakpoint is reached at 500 Hz (f2). Gain then remains relatively constant until a second high frequency breakpoint is reached at about 2.1 kHz (f3), where it again rolls off at 6 dB/octave through the remainder of the audio region and above.

Use of a low frequency roll-off (f0, not shown) is at the option of the designer. Frequency response can be extended towards dc, or, alternately, rolled off at a low frequency below 50 Hz. When applied, this roll-off is popularly called a "rumble" filter, as it reduces turntable/record related low frequency disturbances, lessening low frequency driver overload. This roll-off may or may not coincide with a fourth time constant (below).

However, gain at the frequencies f1, f2, and f3 describes the basic RIAA curve. In the standard, this is described in terms of three corresponding time constants, T1, T2, and T3, defined as 3180 µs, 318 µs, and 75 µs, respectively (Reference 1, again). The T1–T3 are here described as they correspond to *ascend*-*ing frequency*, the reverse of the terminology in Reference 1 (however, the time constants themselves are identical). In some literature one may occasionally find the frequencies corresponding to T1, T2, and T3 referenced. These exact frequencies can be found simply by the basic relationship of:

$$f = 1/(2 \bullet \pi \bullet T)$$

Eq. 6-4

So, for the three time constants specified, the frequencies are:

fl =

$$1/T1 = 1/(2 \cdot \pi \cdot 3180E - 6) = 50$$

Hz

f2 =  $1/T2 = 1/(2 \cdot \pi \cdot 318E - 6) = 500$  Hz

f3 =  $1/T3 = 1/(2 \cdot \pi \cdot 75E - 6) = 2122$  Hz

An IEC amendment to the basic RIAA response adds a fourth time constant of 7950  $\mu$ s, corresponding to an f0 of 20 Hz when used (see Reference 2). Use of this roll-off has never been standardized in the US, and isn't treated in detail here.

The characteristic gain in dB for an RIAA preamp is generally specified relative to a 1kHz reference frequency. For convenience in evaluating the RIAA curve numerically, Figure 6-8 is a complete 10 kHz–100 kHz relative decibel table for the three basic RIAA time constants. From these data several key points

| FREQ      | VDB(6) <sup>(1)</sup> | VDB(5) <sup>(2)</sup> |

|-----------|-----------------------|-----------------------|

|           |                       |                       |

| 1.000E+01 | 1.974E+01             | -1.684E-01            |

| 1.259E+01 | 1.965E+01             | -2.639E-01            |

| 1.585E+01 | 1.950E+01             | -4.109E-01            |

| 1.995E+01 | 1.928E+01             | -6.341E-01            |

| 2.512E+01 | 1.895E+01             | -9.654E-01            |

| 3.162E+01 | 1.847E+01             | -1.443E+00            |

| 3.981E+01 | 1.781E+01             | -2.103E+00            |

| 5.012E+01 | 1.694E+01             | -2.975E+00            |

| 6.310E+01 | 1.584E+01             | -4.067E+00            |

| 7.943E+01 | 1.455E+01             | -5.362E+00            |

| 1.000E+02 | 1.309E+01             | -6.823E+00            |

| 1.259E+02 | 1.151E+01             | -8.398E+00            |

| 1.585E+02 | 9.877E+00             | -1.003E+01            |

| 1.995E+02 | 8.236E+00             | -1.167E+01            |

| 2.512E+02 | 6.645E+00             | -1.327E+01            |

| 3.162E+02 | 5.155E+00             | -1.476E+01            |

| 3.981E+02 | 3.810E+00             | -1.610E+01            |

| 5.012E+02 | 2.636E+00             | -1.727E+01            |

| 6.310E+02 | 1.636E+00             | -1.828E+01            |

| 7.943E+02 | 7.763E-01             | -1.913E+01            |

| 1.000E+03 | 8.338E-07             | -1.991E+01            |

| 1.259E+03 | -7.682E-01            | -2.068E+01            |

| 1.585E+03 | -1.606E+00            | -2.152E+01            |

| 1.995E+03 | -2.578E+00            | -2.249E+01            |

| 2.512E+03 | -3.726E+00            | -2.364E+01            |

| 3.162E+03 | -5.062E+00            | -2.497E+01            |

| 3.981E+03 | -6.572E+00            | -2.648E+01            |

| 5.012E+03 | -8.227E+00            | -2.814E+01            |

| 6.310E+03 | -9.992E+00            | -2.990E+01            |

| 7.943E+03 | -1.184E+01            | -3.175E+01            |

| 1.000E+04 | -1.373E+01            | -3.365E+01            |

| 1.259E+04 | -1.567E+01            | -3.558E+01            |

| 1.585E+04 | -1.763E+01            | -3.754E+01            |

| 1.995E+04 | -1.960E+01            | -3.951E+01            |

| 2.512E+04 | -2.158E+01            | -4.149E+01            |

| 3.162E+04 | -2.357E+01            | -4.348E+01            |

| 3.981E+04 | -2.557E+01            | -4.548E+01            |

| 5.012E+04 | -2.756E+01            | -4.747E+01            |

| 6.310E+04 | -2.956E+01            | -4.947E+01            |

| 7.943E+04 | -3.156E+01            | -5.147E+01            |

| 1.000E+05 | -3.356E+01            | -5.347E+01            |

|           |                       |                       |

Notes: <sup>(1)</sup> Denotes 1 kHz 0 dB reference

<sup>(2)</sup> Denotes dc 0 dB reference

Figure 6-8: Idealized RIAA frequency response referred to 1 kHz and to dc

can be observed: If the 1 kHz gain is taken as the zero dB reference, frequencies below or above show higher or lower dB levels, respectively (Note 1, column 2). With a dc 0 dB reference, it can be noted that the 1 kHz gain is 19.91 dB below the dc gain (Note 2, column 3).

Expressed in terms of a gain ratio, this means that in an ideal RIAA preamp the 1 kHz gain is always 0.101 times the dc gain. The constant 0.101 is unique to all RIAA preamp designs following the above curve, therefore it can be designated as " $K_{RIAA}$ ", or:

$$K_{RIAA} = 0.101$$

Eq. 6-5

This constant logically shows up in the various gain expressions of the RIAA preamp designs following. In all examples discussed here (and virtually all RIAA preamps in general), the shape of the standard RIAA curve is fixed, so specifying gain for a given frequency (1 kHz) also defines the gain for all other frequencies.

It can also be noted from the RIAA curve of Figure 6-7 that the gain characteristic continues to fall at higher frequencies. This implies that an amplifier with unity-gain stability for 100% feedback is ultimately required, which can indeed be true, when a standard feedback configuration is used. Many circuit approaches can be used to accomplish RIAA phono-playback equalization; however, all must satisfy the general frequency response characteristic of Figure 6-7.

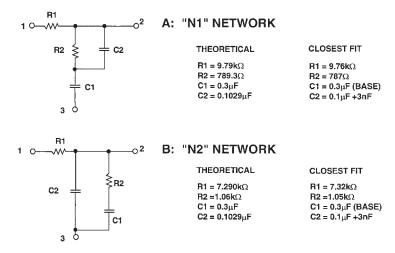

#### Equalization Networks for RIAA Equalizers

Two equalization networks well suited in practice to RIAA phono reproduction are illustrated in Figure 6-9a and 6-9b, networks N1 and N2. Both networks with values as listed can yield with high accuracy the three standard RIAA time constants of 3180 µs, 318 µs, and 75 µs as outlined by network theory (see References 3-6). For convenience, both theoretical values for the ideal individual time constants are shown at the left, as well as closest fit standard "no trim" values to the right. Designers can, of course, parallel and/or series RC values as may be deemed appropriate, adhering to network theory.

There are of course an infinite set of possible RC combinations from which to choose network values, but practicality should rule any final selection. A theoretical starting point for a network value selection can begin with *any* component, but in practice the much smaller range of available capacitors suggests their

Figure 6-9: Two RIAA EQ networks (T1 = 3180 µs, T2 = 318 µs, T3 = 75 µs)

selection first, then resistors, since they have a much broader span of (stock) values. Note that precision film resistors can in fact be obtained (on special order) in virtually *any* value, up to several megohms. The values listed here are those taken as standard from the E96 series.

Very high standards of EQ accuracy are possible, to tolerances of noticeably better than  $\pm 0.1$  dB (see for example data from Reference 8, also quoted in 6). In the design process, there are several distinct general aspects of EQ component selection which can impact the ultimate accuracy. These are worth placing in perspective before starting a design.

The *selection tolerance* of the component defines how far an ideal (zero manufacturing tolerance) component deviates from the theoretical value. A good design will seek to minimize this error by using either carefully selected standard values, or series and/or shunt combinations, so as to achieve selection tolerance of less than 1%, preferably zero.

The *manufacturing tolerance* of the component defines how far an otherwise ideal component deviates from its stated catalog value, such as  $\pm 1\%$ ,  $\pm 2\%$ , and so forth. This can obviously be controlled by tighter specifications, but usually at some premium, particularly with capacitors of  $\pm 1\%$  or less. Note that a "hidden" premium here can be long delivery times for certain values. Care should be taken to use standard stock values with capacitors—even to the extent that multiple standard values may be preferable (three times 0.01 µF for 0.03 µF, as an example).

*Topology-related parasitics* must also be given attention, as they can also potentially wreck accuracy. Amplifier gain-bandwidth is one possible source of parasitic EQ error. However, a more likely error source is the parasitic zero associated with active feedback equalizers. If left uncompensated below 100 kHz, this alone can be a serious error.

In any event, for high equalization accuracy to be "real," once a basic solid topology is selected, the designer must provide for the qualification of components used, by precise measurement and screening, or tight purchase tolerances. An alternative is iterative trimming against a reference standard such as that of Reference 9, but this isn't suited for production. An example is the data of Reference 8, derived with the network of Reference 9. If used, the utility of such a trim technique lies in the reduction of the equipment accuracy burden. While the comparator used needs to have high *resolution*, the accuracy is transferred to the network comparison standard used.

It should be understood that an appropriately selected high quality network will allow excellent accuracy, for example either N1 or N2 with the "closest fit" (single component) values of exact value yield a broadband error of about  $\pm 0.15$  dB. Accuracy about three times better than this is achieved with the use of N1 and the composite C2, as noted. The composite C2 is strongly suggested, as without it there is a selection error of about 3%.

It is also strongly recommended that only the highest quality components be employed for use in these networks, for obvious reasons. Regardless of the quality of the remainder of the circuit, it is surely true that the equalization accuracy and fidelity can be no better than the quality of those components used to define the transfer function. Thus only the best available components are used in the N1 (or N2) RC network, selected as follows:

*Capacitors*—should have close initial tolerance (1%-2%), a low dissipation factor and low dielectric absorption, be noninductive in construction, and have stably terminated low-loss leads. These criteria in general are best met by capacitors of the Teflon, polypropylene and polystyrene film families, with 1%-2% polypropylene types being preferred as the most practical. Types to definitely avoid are the "high K" ceramics. In contrast, "low K" ceramic types, such as "NPO" or "COG" dielectrics, have excellent dissipation factors. See the passive component discussions of Chapter 7 on capacitors, as well as the component-specific references at the end of this section.

#### Chapter Six

*Resistors*—should also be close tolerance ( $\leq 1\%$ ), have low nonlinearity (low voltage coefficient), be temperature stable, with solid stable terminations and low-loss noninductive leads. Types that best meet these criteria are the bulk metal foil types and selected thick films, or selected military grade RN55 or RN60 style metal film resistor types. See the passive component discussions of Chapter 7 on resistors, as well as the component-specific references at the end of this section.

It should be noted also that the specific component values suggested might not be totally optimum from a low impedance, low noise standpoint. But, practicalities will likely deter using appreciably lower ones. For example, one could reduce the input resistance of either network down to say 1 k $\Omega$ , and thus lower the input referred noise contribution of the network. But, this in turn would necessitate greater drive capability from the amplifier stage, and raise the C values up to 1  $\mu$ F–3  $\mu$ F, where they are large, expensive, and most difficult to obtain. This may be justified for some uses, where performance is the guiding criterion rather than cost effectiveness, or the amplifiers used are sufficiently low in noise to justify such a step. Regardless of the absolute level of impedance used, in any case the components should be adequately shielded against noise pickup, with the outside foils of C1 or C2 connected either to common or a low impedance point.

These very same N1/N2 networks can suffice for both active and passive type equalization. Active (feed-back) equalizers use the network simply by returning the input resistor R1 to common, that is jumpering points 1–3, and employing the network as a two-terminal impedance between points 1+3, and 2. Passive equalizers use the same network in a three-terminal mode, placed between two wideband gain blocks.

#### **RIAA Equalizer Topologies**

Many different circuit topologies can be used to realize an RIAA equalizer. Dependent upon the output level of the phono cartridge to be used, the 1 kHz gain of the preamp can range from 30 dB to more than 50 dB.

Magnetic phono cartridges in popular use consist of two basic types: moving magnet (MM) and moving coil (MC). The moving magnet types, which are the most familiar, are suitable for the first two circuits described. The moving coil cartridge types are higher performance devices; they are less commonplace but still highly popular.

Functionally, both types of magnetic cartridges perform similarly, and both must be equalized for flat response in accordance with the RIAA characteristic. A big difference in application, however, is the fact that moving magnet types have typical sensitivities of about 1 mV of output for each cm/s of recorded velocity. In moving coil types, sensitivity on the order of 0.1 mV is more common (for a similar velocity). In application then, a moving coil RIAA preamp must have more gain than one for moving magnets. Typically, 1 kHz gains are 40 dB–50 dB for moving coils, but only 30 dB–40 dB for moving magnets. Noise performance of a moving coil preamp can become a critical performance factor however, because of low-output voltage and low impedance involved—typically this is in the range of just 3  $\Omega$ –40  $\Omega$ . The following circuit examples illustrate techniques that are useful to these requirements.

#### Actively Equalized RIAA Preamp Topologies

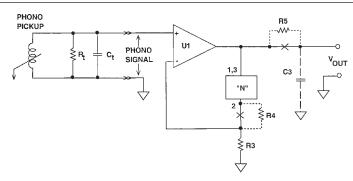

The most familiar RIAA topology is shown in general form in Figure 6-10, and is called an active feedback equalizer, as the network N used to accomplish the EQ is part of an active feedback path (see References 10, 11). In these and all of the following discussions it is assumed that the input from the pickup is appropriately terminated by  $R_t$ – $C_t$ , which are selected for flat *cartridge* frequency response driving U1. The following discussions deal with the *amplification* frequency response, given this ideal input signal.

Assuming an adequately high gain amplifier for U1, the gain/frequency characteristics of this circuit are determined largely by the network. The gain of the stage is set by the values of the network N and  $R_3$ , and

Figure 6-10: Active feedback RIAA equalizer

the U1 output is a low impedance,  $V_{OUT}$ . The 1 kHz gain of this stage is defined by the RIAA curve and resistors  $R_1$  and  $R_3$ , and is:

$$G = 0.101 \bullet \left[ 1 + (R_1/R_3) \right]$$

Eq. 6-6

where 0.101 is the constant  $K_{RIAA}$ .  $R_1$  is within N;  $R_4$  and  $R_5$  are discussed momentarily.

As noted previously, an ideal RIAA response continues to fall with increasing frequency, and can in fact be less than unity at some high frequency (Figure 6-7, again). But, the basic U1 topology of Figure 6-10 can't achieve this, as the minimum gain seen at the output of U1 approaches unity at some (high) parasitic zero frequency, where the network equivalent series capacitive impedance of  $C_1$  and  $C_2$  is equal to  $R_3$ . At this zero frequency, the response from U1 simply levels off and ceases to track the RIAA curve.

However, in terms of practical consequence the error created by this zero may or may not be of significance, dependent upon where the zero falls (as determined by gain). If well above audibility (i.e.,  $\geq$  100 kHz), it will introduce a small equalization error at the upper end of the audio range. For example, if it falls at 100 kHz, the 20 kHz error is only about 0.3 dB. Fortunately, this error is easily compensated by a simple low-pass filter after the amplifier,  $R_5$ – $C_3$ . The filter time constant is set to match the zero  $T_4$ , which is:

$$T4 = R_3 \bullet C_{EQUIV} \qquad Eq. \ 6-7$$

where  $R_3$  is the value required for a specific gain in the design.

C<sub>EQUIV</sub> is the series equivalent capacitance of network capacitors C<sub>1</sub> and C<sub>2</sub>, or:

$$\mathbf{C}_{\text{EQUIV}} = (\mathbf{C}_1 \bullet \mathbf{C}_2) / (\mathbf{C}_1 + \mathbf{C}_2)$$

Eq. 6-8

Here the  $C_{EQUIV}$  is 7.6 nF and  $R_3 200 \Omega$ , so T4 = 1.5µs The product of R5 and C4 are set equal to T4, so picking a R5 value solves for C4 as:

$$C4 = T4/R5$$

Eq. 6-9

The 1.5  $\mu$ s R<sub>5</sub>-C<sub>4</sub> time constant is realized with R<sub>5</sub> = 499  $\Omega$  and C4 = 3 nF. This design step increases the output impedance, making it more load susceptible. This should be weighed against the added parts and loading. In general, R<sub>5</sub> should be low, i.e.,  $\leq 1 \text{ k}\Omega$ .

In some designs, a resistor  $R_4$  (dotted in Figure 6-10) may be used with N (for example, for purposes of amplifier stability at a gain higher than unity). With  $R_4$ , T4 is calculated as:

$$T4 = (R_3 + R_4) \bullet C_{EQUIV} \qquad Eq. 6-10$$

The  $R_5-C_3$  product is again chosen to be equal to this T4 (more on this below).

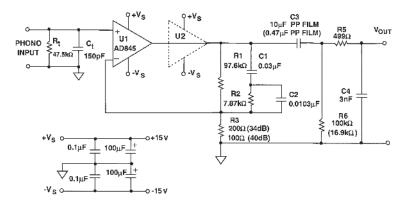

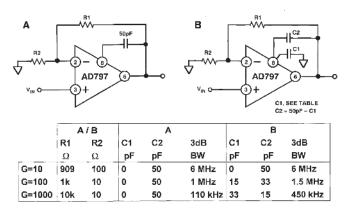

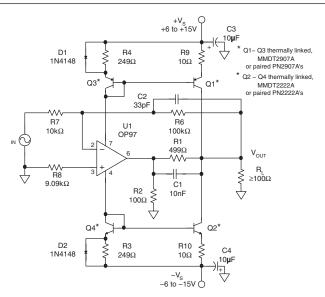

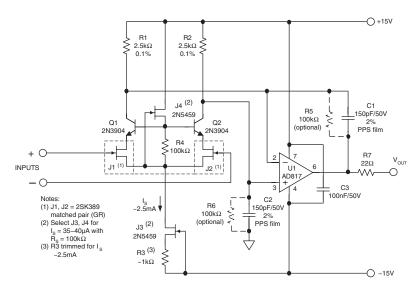

The next two schematics illustrate variations of the most popular approach to achieving a simple RIAA phono preamp, using active feedback, as just described. Figure 6-11 is a high performance, dc-coupled version using precision 1% metal film resistors and 1% or 2% capacitors of polystyrene or polypropylene type. Amplifier U1 provides the gain, and equalization components R1-R2-C1-C2 form the RIAA network, providing accurate realization with standard component values. N1 is the network, with 1 and 3 common.

Figure 6-11: A dc-coupled active feedback RIAA moving magnet preamp

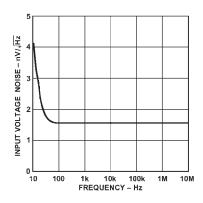

As mentioned, input RC components  $R_t$ - $C_t$  terminate the moving magnet cartridge with recommended values (shown as typical). In terms of desired amplifier parameters for optimum performance, they are considerably demanding. For lowest noise from a cartridge's inductive source, the amplifier should have an input voltage noise density of 5 nV/ $\sqrt{Hz}$  or less (favoring a bipolar), and an input current noise density of 1 pA/ $\sqrt{Hz}$  or less (favoring a FET). In either case, the 1/F noise corner should be as low as possible.

For bipolar-input amplifiers, dc input-bias current can be a potential problem when direct coupling to the cartridge, so in this circuit only a very low input bias current type is suggested. If a bipolar input amplifier is used for U1, it should have an input current of <<100 nA for minimum dc offset problems (assuming a typical phono cartridge of  $\approx 1 \text{ k}\Omega$  resistance). Examples are the OP27, OP270 families. FET-input amplifiers generally have negligible bias currents but also tend typically to have higher voltage noise. FET-input types useful for U1 are the AD845 and OP42, even though their voltage noise is not as low as the best of the bipolar devices mentioned. On the plus side, they both have a high output current and slew rate, for low distortion driving the feedback network load (approximately the R3 value at high frequencies). Of the two, the OP42 has lower noise, the AD845 higher output current and slew rate.

For high gain accuracy at high stage gains, the amplifier should have a high gain-bandwidth product; preferably >5 MHz at audio frequencies. Because of the 100% feedback through the network at high frequencies, the U1 amplifier must be unity-gain-stable. To minimize noise from sources other than the amplifier, gain resistor  $R_3$  is set to a relatively low value, which generates a low voltage noise in relation to the amplifier.

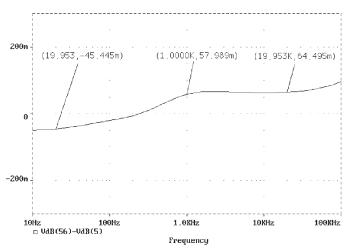

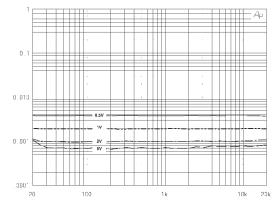

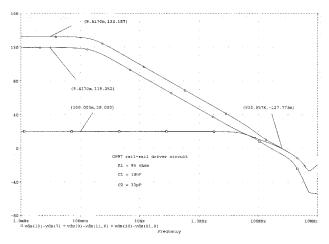

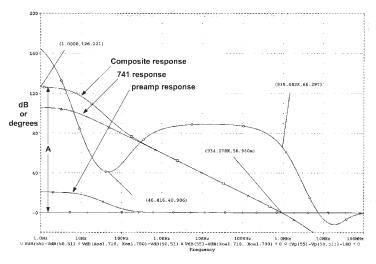

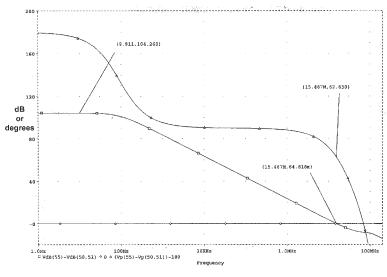

RIAA accuracy is quite good using the stock equalizer values. A PSpice simulation run is shown in Figure 6-12 for the suggested gain of 34 dB. In this expanded scale plot over the 20 kHz–20 kHz range, the error relative to the 1 kHz gain is less than  $\pm 0.1$  dB.

As can be noted from Figure 6-12, the relative amplitude is expanded, to easily show response errors. A perfect response would be a straight line at 0 dB, meaning that the circuit under test had exactly the same gain as an ideal RIAA amplifier of the same 1 kHz gain. This high sensitivity in the simulation is done via the use of a feature in PSpice allowing the direct entry of Laplace statements (see Reference 10). With this evaluation tool, the ideal transfer function of an RIAA equalizer can be readily generated. The key parameters are the three time constants described above, and the ideal dc gain.

Figure 6-12: Relative error (B) versus frequency for dc-coupled active feedback RIAA moving magnet preamp, gain of 34 dB

The syntax to enable this mode of comparison is contained in the listing of Figure 6-13, which is the PSpice CIR file for the circuit of Figure 6-11. The Laplace details are all contained within the dotted box, and need only the editing of one value, "ENORM," for gain normalization from one circuit to another (see boldface). In this case ENORM is set to 490.7, to match the ideal R1 and R3 values of Figure 6-13. When the analysis is run, a difference display of the circuit-under-test and the ideal outputs (i.e., VdB(56)–VdB(5)) shows the relative response (Figure 6-12). Vertical axis scaling is easily adjusted for sensitivity, and is ±300 mB as displayed in Figure 6-12.

```

RIAA34LP: 34 dB gain RIAA preamp with AD845

+

.OPT ACCT LIST NODE OPTS NOPAGE LIBRARY

.AC DEC 10 10 100KHZ

.LIB D:\PS\ADLIB\AD_RELL.LIB

.PRINT AC VDB(5) VDB(56)

. PROBE

VIN 1 0 AC 1E-3

VCC 52 0 +15V

VEE 53 0 -15V

* ----- V(5) = idealized RIAA frequency response ------

* Uses Laplace feature of PSpice Analog Behavioral option

* for frequency response reference.

* ENORM = ideal U1 DC gain = 1+(R1/R3) Use ideal values for R1, R3

* T1 - T3 are time constants desired (in µs).

* Input = node 1, Laplace Output = node 5

.PARAM ENORM = \{490.7\}

.PARAM T1 = {3180} ; Reference RIAA constants, do not alter!

.PARAM T2 = {318} ; Reference RIAA constants, do not alter!

.PARAM T3 = {75} ; Reference RIAA constants, do not alter!

ERIAA 5 0 LAPLACE {ENORM*V(1)}={(1+(T2*1E-6)*S)/((1+(T1*1E-6)*S)*(1+(T3*1E-6)*S))}

RDUMMY5 5 0 1E9

_____

*

(+) (-) V+ V- OUT

1 21 52 53 55 AD845

XU3

* Active values Theoretical values

R1 55 21 97.6K

; 97.9k

R2 21 8 7.87K

; 7.8931563k

C1 55 8 30NF

; 30nF

C2 21 8 10.3NF

; 10.2881nF R3 21 0 200

; 199.9148

C3 55 100 10E-6

R6 100 0 100K R5 100 56 499

C4 56 0 3.0000E-9

.END

```

Figure 6-13: An example PSpice circuit file that uses the Laplace feature for ideal RIAA response comparison

The 1 kHz gain of this circuit can be calculated from Eq. 6-6. For the values shown, the gain is just under 50 times ( $\approx$ 34 dB). Higher gains are possible by decreasing R<sub>3</sub>, but gains >40 dB may show increasing equalization errors, dependent upon amplifier bandwidth. For example, R<sub>3</sub> can be 100  $\Omega$  for a gain of

about 100 times ( $\approx$ 40 dB). Note that if R<sub>3</sub> is changed to 100  $\Omega$ , C<sub>4</sub> should also be changed to 1.5 nF, to satisfy Eq. 6-9.

Dependent upon the amplifier in use, this circuit is capable of very low distortion over its entire range, generally below 0.01% at levels up to 7 V rms, assuming  $\pm 15$  V supplies. Higher output with  $\pm 17$  V supplies is possible, but will require a heat sink for the AD845. U2 is an optional unity-gain buffer useful with some op amps, particularly at higher gains or with a low-Z network. But this isn't likely to be necessary with U1 an AD845.

For extended low-frequency response,  $C_3$  and  $R_6$  are the large values, with  $C_3$  preferably a polypropylene film type. If applied, the alternate values form a simple 6 dB per octave rumble filter with a 20 Hz corner. As can be noted from the figure's simplicity,  $C_3$  is the only dc blocking capacitor in the circuit. Since the dc circuit gain is on the order of 54 dB, the amplifier used must be a low offset-voltage device, with an offset voltage that is insensitive to the source. Since these preamps are high gain, low level circuits ( $\geq$ 50 dB of gain at 50 Hz/60 Hz), supply voltages should be well regulated and noise-free, and reasonable care should be taken with the shielding and conductor routing in their layout.

Alternately, an inexpensive ac-coupled form of this circuit can be built with higher bias current, low noise bipolar op amps, for example the OP275,  $I_B = 350 \text{ nA}(\text{max})$ , which would tend to make direct coupling to a cartridge difficult. This form of the circuit is shown in Figure 6-14, and can be used with many unity gain stable bipolar op amps.

Figure 6-14: An ac-coupled active feedback moving magnet RIAA preamp

Here input ac coupling to U1 is added with C<sub>5</sub>, and the cartridge termination resistance R<sub>t</sub> is made up of the R<sub>6</sub>-R<sub>7</sub> parallel equivalent. R<sub>3</sub> of the feedback network is ac-grounded via C<sub>4</sub>, a large value electrolytic. These measures reduce the dc offset at the output of U1 to a few mV. Nearest 5% values are also used for the network components, making it easily reproducible and inexpensive. C<sub>3</sub> is a nonpolar electrolytic type, and the R<sub>3</sub>-C<sub>4</sub> time constant as shown provides a corner frequency of  $\leq 1$  Hz at the 34 dB gain.

Frequency response of this version (not shown) isn't quite as good as that of Figure 6-11, but is still within  $\pm 0.2$  dB over 20 Hz–20 kHz (neglecting the effects of the low frequency roll-off). If a tighter frequency response is desired, the N1 network values can be adjusted. With a higher rated maximum supply voltage for the OP275, the power supplies of this version can be  $\pm 21$  V if desired, for outputs up to 10 V rms.

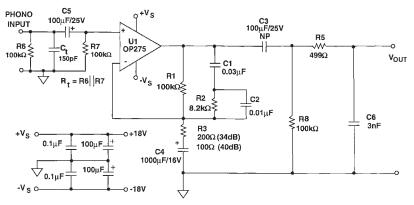

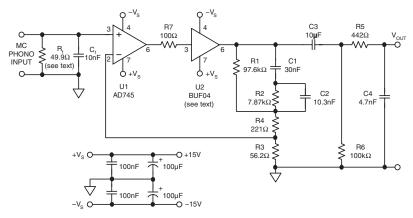

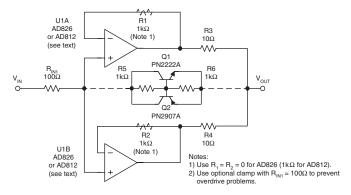

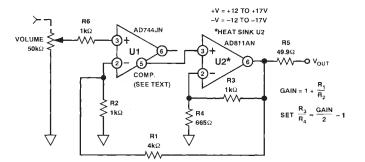

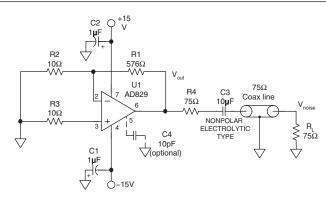

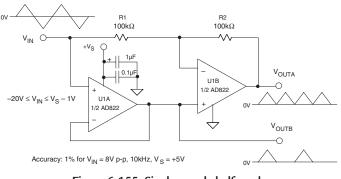

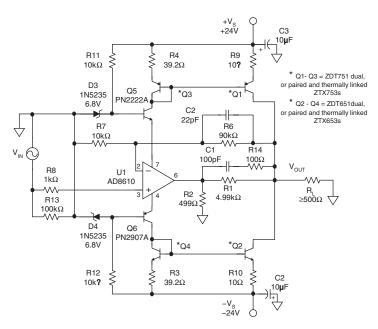

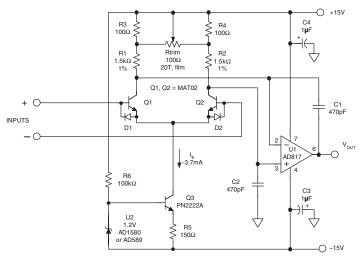

There is another, very useful variation on the actively equalized RIAA topology. This is one that operates at appreciably higher gain and with lower noise, making it suitable for operation with higher output moving coil (MC) cartridges. In this design example, shown in Figure 6-15, the basic circuit is used is quite similar to that of Figure 6-11. The lower  $R_t$  and  $C_t$  values shown are typical for moving coil cartridges. They are of course chosen per the manufacturer's recommendations (in particular the resistance).

Figure 6-15: A low noise dc-coupled active feedback RIAA moving coil preamp with 45 dB of gain

To make it suitable for a high-output MC cartridge, a very low-noise FET op amp is used for U1, the AD745. The AD745 is stable at a minimum gain of five times, as opposed to the unity-gain stable op amps of the prior examples. This factor requires a modification to gain resistors R1-R3. This is the inclusion of an extra resistor, R4. With the ratio shown, R3 and R4 form a 5/1 voltage divider for the voltage seen at the bottom of network N (the R1-R2-C2 node). This satisfies U1's gain-of-five stability requirement.

In this gain setup, R3 is still used for the gain adjustment, and R1-R2-C1-C2 still form the basic N1 RIAA network. With R4 used, Eq. 6-9 is used to calculate the T4 time constant. With C4 chosen as a standard value, R5 is then calculated. With these N1 network values and a 45 dB 1 kHz gain, R3 is 56.2  $\Omega$ , which is still suitable as a low noise value operating with either an AD745 or an OP37 used for U1.

Some subtle points of circuit operation are worth noting. The dc gain of this circuit is close to 1800, which can result in saturation of U1 if offset isn't sufficiently low. Fortunately, the AD745 has a maximum offset of 1.5 mV over temperature, making the output referred offset always less than 3 V. While this may limit the maximum output swing some due to asymmetrical clipping, 5 V rms or more of swing should be available operating from  $\pm 15$  V supplies. Coupling capacitor C3 decouples the dc output offset at U2, so any negative consequences of dc-coupling the U1 gain path are minimal.

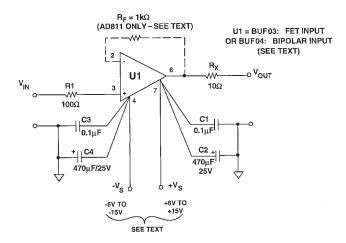

For minimal loading of U1 and maximum linearity at high gains, the unity-gain buffer amplifier U2 is used, a BUF04. The BUF04 is internally configured for unity-gain operation, and needs no additional components. Note that this buffer is optional, and is not absolutely required. Other buffer amplifiers are discussed later in this chapter.

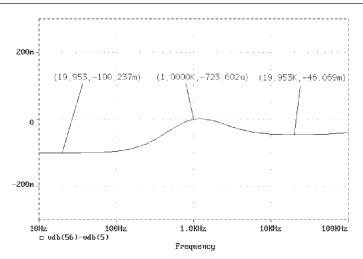

This Figure 6-15 circuit was analyzed with PSpice using the Laplace comparison technique earlier described, and the results are displayed in Figure 6-16. As was true previously, the vertical scaling of this

Figure 6-16: Relative error (B) versus frequency for dc-coupled active feedback RIAA moving coil preamp, gain of 45 dB (simulation)

display is very sensitive;  $\pm 300 \text{ mB}$  (or  $\pm 0.3 \text{ dB}$ ). Thus, placed in context, gain errors relative to 1 kHz over 20 kHz–20 kHz are extremely small,  $\approx 0.1 \text{ dB}$ . Lab measurements of the circuit were also consistent with the simulation. Of course in terms of audible effects, errors of  $\pm 0.1 \text{ dB}$  or less aren't likely to be apparent.

Distortion/noise measurements of the circuit are essentially dominated by noise (as opposed to actual distortion) measuring ~0.01% THD + N or less, over output levels ranging from 0.5 to 5 V rms, from 20 Hz–20 kHz. Of course, as with any high gain circuit, layout and lead dress into the circuit are extremely critical to noise, and must be arranged for minimum susceptibility. Supply voltages must be low in noise, and well regulated.

This exercise has illustrated both the basic design process of the active RIAA equalizer, as well as a convenient SPICE analysis method to optimize the design for best frequency response. It is not suggested that the exact network values shown of the examples are the only ones suitable. To the contrary, great many sets of values can be used with success comparable to that shown above.

This final active equalizer circuit example is the best of the bunch, and has a virtue of being easily adapted for other operating conditions; i.e., higher gain, other networks, and so forth. For example, note that even lower noise MC operation is possible, by using the  $\leq 1 \text{ nV}/\sqrt{\text{Hz}}$  AD797 for U1, and scaling the N1 RC components further downward. This will have the desirable effect of making R3 lower than 50  $\Omega$ , which minimizes the R1–R4 network's noise. Note that gains of 50 dB or more are also possible, suitable for very low output moving coil cartridges (given suitable attention to worst-case U1 offsets).

#### Passively Equalized RIAA Preamp Topologies

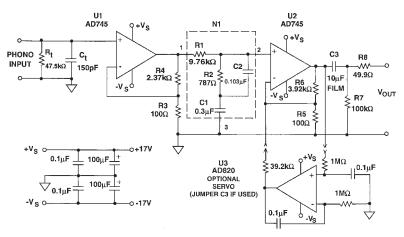

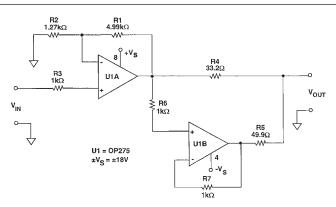

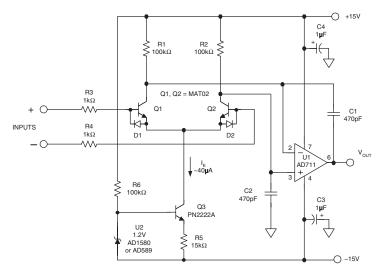

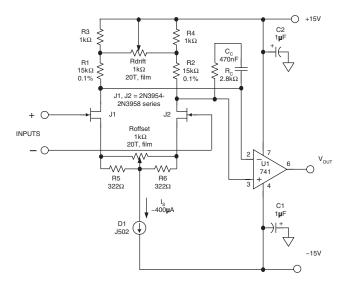

Another RIAA design approach is the so-called *passively equalized* preamp (see Reference 11). This topology consists of two high quality, wideband gain blocks, separated by a three terminal passive network, N (N can be either network N1 or N2). The gain blocks are assumed very wide in bandwidth, so in essence the preamp's entire frequency response is defined by the passive network, thus the name passively equalized. A circuit topology useful for such RIAA phono applications is shown in Figure 6-17. This circuit consists of two high-quality wide bandwidth gain blocks, U1 and U2, as discussed above. Selection of these amplifiers and their operating conditions optimizes the preamp for gain, noise, and overload characteristics. The circuit can be set up for either MM or MC operation by simple value changes and op amp selection.

Figure 6-17: A passively equalized RIAA preamp with 40 dB gain

The gain stages are set up for the required total gain, via  $R_4$ - $R_3$  and  $R_6$ - $R_5$ . In general, the total 1 kHz gain of this circuit G is:

$$G = 0.101 \bullet \left[ 1 + (R_4/R_3) \right] \bullet \left[ 1 + (R_6/R_5) \right]$$

Eq. 6-11

The op amp gain blocks could be made identical for purposes of simplicity but are not necessarily so for the following reasons. A preamplifier topology such as this must be carefully optimized for signal-handling capability, both from an overload standpoint and from a low-noise viewpoint. Stage U1 is chosen for a gain sufficiently high that the input-referred noise will be predominantly due to this stage and the cartridge, but not so high that it will readily clip at high level high frequency inputs. Amplifiers with a  $\approx 10$  V rms output capability allow U1 to accept  $\approx 400$  mV rms at high frequencies using  $\pm 18$  V supplies, while still operating with useful gain (about 25 times).

The gain of the two blocks are set by  $R_4$ - $R_3$  and  $R_6$ - $R_5$ , as defined by Eq. 6-11. The gain values shown yield a 1 kHz gain that is the product of the U1-U2 stage gains (24.7 times 40.2), times that of the interstage network N (0.101). This yields an overall 40 dB 1 kHz gain. Other gains are realized most simply by changes to  $R_5$  or  $R_3$ .

As previously noted, a passively equalized preamplifier such as this must be carefully optimized both from an overload standpoint and from a low noise viewpoint. Stage U1 is chosen for a gain sufficiently high that the input-referred noise will be predominantly due to this stage (and the cartridge, when connected), but not so high that it will readily clip at high level high frequency inputs. To aid this objective, maximum supply voltage and a high output capability amplifier should be used for U1.

Note that U1 operates at relatively high gain, but it needn't be unity gain stable. Decompensated low noise op amps such as the OP37 and the FET input AD745 will provide best signal/noise ratio here. For other FET-input types, the AD845, as well as the OP17 family types, will also yield good performance, but with higher noise levels.

In general, the preceding factors dictate that gain distribution between U1 and U2 be LOW/HIGH from an overload standpoint, but HIGH/LOW from a noise standpoint. Practically, these conflicting requirements can be mitigated by choosing the highest allowable supply voltage for U1, as well as a low noise device. Because of nearly 40 dB loss in the network N at 20 kHz, the output overload of the circuit will be noted at high frequencies first. With the gain distribution shown, the circuit allows a 3 V rms undistorted output to 20 kHz with  $\pm 15$  V supplies, or more with higher supply voltages.

The equalization network N following U1 should use the lowest impedance values practical from the standpoint of low noise, as the noise output at Pin 2 of the network is equivalent to the input referred noise of A2. The network of Figure 6-17 uses the "N1" RC values of  $R_1$ - $R_2$ - $C_1$ - $C_2$  of Figure 6-9a. As noted, scaling can be applied to either network of Figure 6-9 for component selection, as long as the same ratios are maintained.

Noise in amplifier U2 is less critical than U1 at low frequencies, but is still not negligible. A low voltage noise device is very valuable to the U1 and U2 positions, as is a relatively low input current noise. If extremely low noise performance is sought, such as for a moving coil preamp, the N1 values can be reduced further, and R3 be lowered for lower noise and additional gain. For example, a 45 dB gain preamp could be realized by just dropping R3 to 56.2  $\Omega$ , and using an OP37 for U1.

As mentioned before, a low bias current device is appropriate to U1 using bipolar amplifiers. With a 100nA or less bias current device, direct coupling to a moving magnet phono cartridge is practical. For example, the 80 nA (maximum) bias current of the OP37 will induce only an additional 80  $\mu$ V–160  $\mu$ V input voltage offset at U1 for a typical 1 k $\Omega$ –2 k $\Omega$  cartridge resistance. For lower dc resistance MC cartridges, this will be much less of course. Similarly, the bias current induced offset voltage of U2, from the 10 k $\Omega$  dc resistance of R<sub>1</sub> will also be low relative to the amplified offset of U1. As a result, the worst-case overall output dc offset using two AD745s can be held to under 2 V for a 40 dB gain, allowing a single C<sub>3</sub> coupling capacitor for dc blocking purposes.

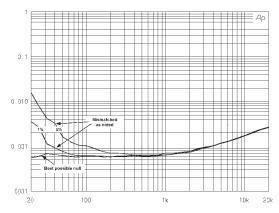

Frequency response of this passively equalized preamp tends to be better than that of the active versions, because of less interaction with the amplifier(s) as compared to the active preamps. It can approach the inherent accuracy of the network components in the audio range, with potentially greater errors at higher frequencies.

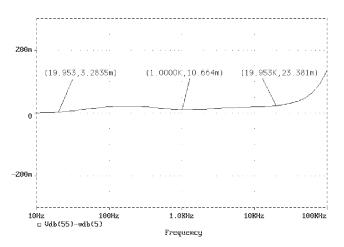

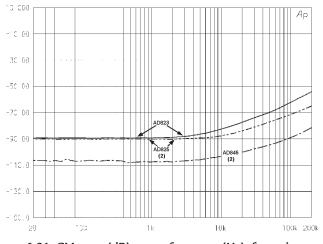

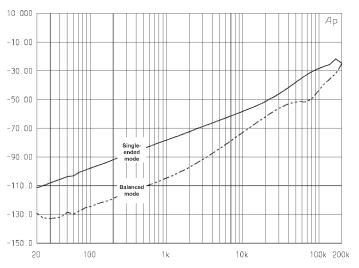

Figure 6-18 illustrates this point, in a simulation of the Figure 6-17 circuit using the OP37 models. The midband error is on the order of  $\pm 0.02$  dB with the N1 network composite values. For practical purposes

Figure 6-18: Relative error (B) versus frequency for passively equalized RIAA preamp, gain of 40 dB (simulation)

then, the frequency response errors of this circuit will be governed by the tolerances of the network components used within it.

This circuit also can be optionally adapted to servo control of the output offset. This is accomplished by deleting coupling capacitor  $C_3$ , substituting a jumper in its place, and using the noninverting servo integrator U3 around stage U2. This is shown as an option within Figure 6-17. A general-purpose noninverting servo can be used for U3, along with a low-offset op amp, such as the AD820, or the OP97.

#### **References: RIAA Phono Preamplifiers**

- 1. RIAA, "Standard Recording and Reproducing Characteristic, Bulletin E1," November 6, 1978, RIAA, 1 E. 57th St, NY, NY, 10022.

- 2. IEC, "Publication 98 (1964), Amendment #4," September 1976.

- 3. F. Bradley, R. McCoy, "Driftless DC Amplifier," Electronics, April 1952.

- 4. G. Korn, T. Korn, Electronic Analog and Hybrid Computers, 2nd Ed., McGraw-Hill, 1972, ISBN 0-07-035363-8.

- 5. D. Stout, M. Kaufman, Handbook of Operational Amplifier Circuit Design, McGraw-Hill, 1976, ISBN 0-07-061797-X.

- 6. S. Lipshitz, "On RIAA Equalization Networks," JAES, Vol. 27 #6, June 1979, pp. 458–481.

- 7. P. Baxendall, "Comments on 'On RIAA Equalization Networks'," **JAES**, Jan/Feb 1981. See also: S. Lipshitz, "Author's Response."

- 8. Walt Jung, "The PAT-5/WJ-1 Equalization Errors" (Letters), The Audio Amateur, issue 3/78, pp. 49–53.

- 9. S. Lipshitz, W. Jung, "A High Accuracy Inverse RIAA Network," **The Audio Amateur**, issue 1/80, pp. 22-24.

- 10. Walt Jung, "SPICE Technique Compares Frequency Responses," EDN, November 25, 1993, pp. 188 and 190.

- 11. Walt Jung, "Topology Considerations for RIAA Phono Preamplifiers," **67th AES Convention**, November 1980, preprint #1719.

- 12. G. Erdi, et al, "Op Amps Tackle Noise and for Once Noise Loses," Electronic Design, December 20, 1980, pp. 65–71.

- 13. Walt Jung, "Audio Preamplifiers, Line Drivers, and Line Receivers," within Chapter 8 of Walt Kester, **System Application Guide**, Analog Devices, Inc., 1993, ISBN 0-916550-13-3, pp. 8-1 to 8-100.

- 14. W. Jung, R. Marsh, "Picking Capacitors," Parts 1&2, Audio, February & March 1980.

- 15. B. Duncan, "With a Strange Device," multiple part series on capacitors, **Hi-Fi News And Record Review**, April-November 1985.

- 16. B. Duncan, M. Colloms, "Pièce de Résistance, Parts 1–3," **Hi-Fi News And Record Review**, March, April 1987 (Duncan); June 1987 (Colloms).

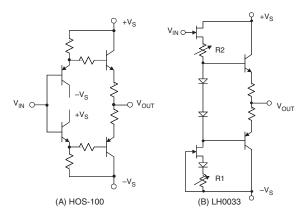

# Audio Line Level Stages

Audio line level stages represent an intermediate level in dynamic range for practical audio circuits using modern IC devices. Line level amplifying stages generally work with single-ended or balanced input/output signal levels of 1 V-10 V, and at medium levels of power. This section discusses some basic types of audio line stages which are:

*Line receivers*—including line receiver stages that accept single-ended or balanced line level signals with maximum noise immunity, and provide scaled outputs for further processing.

*Line amplifiers*—including amplifiers that scale a received signal in single-ended form and feature low distortion designs.

*Line drivers*—including single-ended and balanced drivers capable of driving appreciable output levels in terms of voltage, swing, current levels, and/or difficult loads, such as capacitive lines.

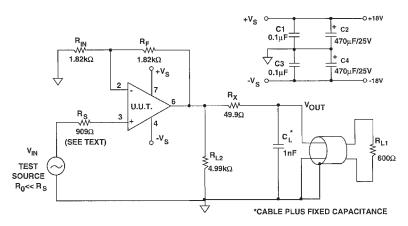

Some general concepts of line driving and buffer amplifier design have been covered previously, with emphasis on video applications (see References 1–3). Some of the material in this section continues and expands on those themes with audio line-receiver and line-driver discussions in a wide variety of applications. Video applications for line driving and receiving is discussed in detail within Section 6-2.

Audio transmission systems, unlike their video counterparts, do *not* use terminated transmission lines as a rule, so long transmission lines usually appear capacitive. Therefore, the concepts of capacitive load isolation are also important to audio drivers. In general, when building practical audio circuits of any type, "housekeeping" rules of layout and bypassing are strongly recommended, particularly so for audio buffer and line driver circuits. They are discussed in further detail in that section.

The function of sending/receiving audio signals between various system components has traditionally involved trade-offs of one form or another. Fully differential or *balanced* transmission systems are best at rejecting low frequency and RF noise, so they are used for highest performance, and are discussed in some detail following.

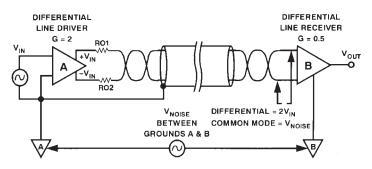

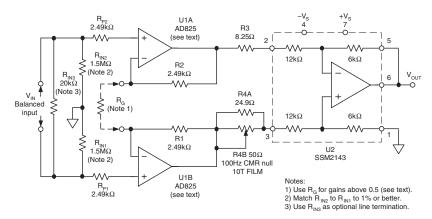

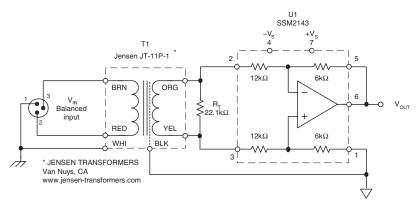

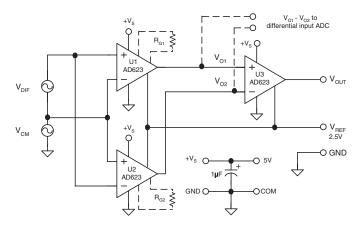

A typical audio system block diagram using differential or balanced transmission is shown in Figure 6-19. In concept, a balanced transmission system like this could use several input/output coupling schemes within the driver and receiver. Some major points distinguishing coupling method details are discussed briefly, before addressing actual circuits.

Figure 6-19: An audio balanced transmission system

*Transformers* (see References 4–7) have been a traditional audio line coupling element. They can be used at either input or output stage. They also have well-known problems with noise pickup, frequency response, distortion, and operating level. While these problems are soluble to some degree, answers are usually costly. Nevertheless, transformers are unexcelled in notable areas.

The single most outstanding virtue of transformer operation lies in the ability to isolate while transmitting the signal, which shows up in two regards. The first of these is that transformers, which transmit an audio signal between the end terminals of an isolated winding, thus *galvanically isolate* driver and receiver stages. This is accomplished at common-mode voltage (ground difference) levels up to the breakdown potential of the windings, allowing signals to be transmitted across very high ground potential differences (tens or hundreds of volts). This feature is very difficult to achieve with solid-state circuitry. Secondly, suitably designed transformers can have very high common-mode rejection (CMR) over the audio range,  $\geq 100 \text{ dB}$  in some cases, a factor basically intrinsic to their nature. Some transformer-isolated stages are described in this section.

In practice the general system of Figure 6-19 can use either transformer-based or active stage coupling to the line, at either end. The goal for either approach is to reproduce a final signal  $V_{OUT}$  equal to  $V_{IN}$ , while rejecting noise between grounds A and B by a factor of 80 dB–100 dB. Typically, a unity gain (overall) design uses a balanced line drive of  $\pm V_{IN}$ , followed by a receiver gain "G" of <sup>1</sup>/<sub>2</sub>, which maximizes the receiver CM range.

A point worth noting that the  $\pm$  voltage drive to the line need *not* be exactly balanced to reap the benefits of balanced transmission. In fact the drive can be asymmetrical to some degree, and the signal will still be received at V<sub>OUT</sub> with correct amplitude, and with good noise rejection. What *does* need to be provided is two well-balanced line-driving impedances, R<sub>01</sub> and R<sub>02</sub>. Also, in conjunction with these balanced drive impedances, the associated (+) and (–) receiver input impedances should also be equal. The technical reasons for this will be apparent shortly.

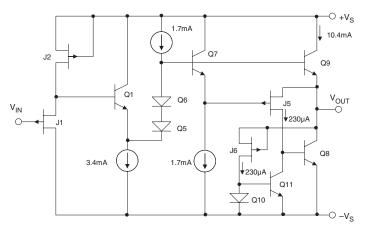

#### Audio Line Receivers

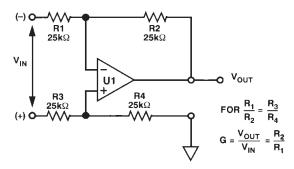

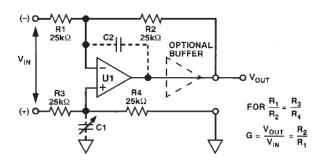

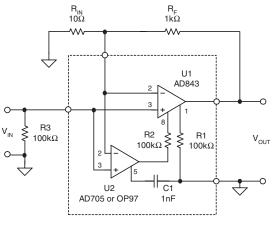

A brief review of the topologies and application points of audio line receivers helps in understanding their evolution, and more importantly, how their audio performance differs with topological changes. Figure 6-20 is a diagram of a classic 4-resistor differential amplifier. This general circuit is also known as the most simple instrumentation amplifier form, even though its performance as an in amp has severe limitations. Within audio applications, this and related circuits are called "line receivers" for the sake of brevity. Various in amp type topologies have developmental histories dating from the late sixties up to and including today's modern in amp ICs (see References 8–12 and Chapter 2).

Figure 6-20: A simple line receiver using a 4-resistor differential amplifier

In today's professional audio world, signals by and large get transmitted in balanced mode (Figure 6-19). This fact is simply due to the much greater noise immunity of this method, vis-à-vis the more simple, but highly noise-susceptible single ended method.

Yet, even within the professional audio world there is no real unanimity on signal driver and receiver circuits for use within balanced circuits—they take on many forms and have differing performance, and a wide variety of circuits find use. Before getting into actual receiver circuitry, it is helpful to take a brief look at some problems impacting circuit performance in terms of common mode (CM) noise susceptibility. This will illustrate how careful hardware choices lowers system cost/size, and maintains excellent performance. Conversely, simple receivers can also be used, for modest performance.

#### Source-Load Interactions within Balanced Systems

Some recent attention has focused on the general problem of noise susceptibility in audio system interfacing (see References 13 and 14). The discussions below are concerned with how balanced system drivers and receivers interact fundamentally to produce undesired side effects of noise susceptibility. Suggestions for practical solutions are then offered.

In most simple form, a balanced audio transmission system consists of a differential output driver, an interconnecting cable, and a differential input receiver, such as shown in Figure 6-19 (again). The driver produces nominally equal and out-of-phase output signals, with some characteristic (and matched) source impedances,  $R_{OUT1}$  and  $R_{OUT2}$ . As will be seen, from a noise susceptibility standpoint, it is highly desirable that these two impedances be well balanced, i.e., matched. The driver is connected to the input end of a balanced transmission line, typically a shielded twisted pair. At the opposite end of this line, a differential input receiver receives the balanced signal, and (ideally) rejects the CM noise voltage  $V_{NOISE}$ .

The design of both the driver and the receiver has great influence upon how well the overall scheme works in transmitting a noise-free audio signal from driver to receiver. References 14 and 15 discuss different driver and receiver types, active and passive. These papers bring out the inherent degradation in noise sensitivity active receivers can trigger, if they do not have input characteristics which are an appropriate complement to the system driving impedances.

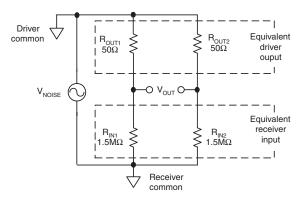

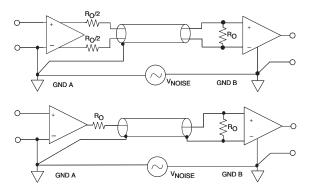

From a noise introduction point of view, the balanced transmission system under discussion can be analyzed as a bridge circuit, as shown in Figure 6-21. Here the two source resistances  $R_{OUT1}$  and  $R_{OUT2}$  correspond to the output resistances of the differential driver voltage sources. Similarly, input resistances  $R_{IN1}$

Figure 6-21: A conceptual driver/receiver diagram of a balanced line audio system with key impedances and CM noise

and  $R_{IN2}$  correspond to the input resistances of the differential receiver.  $V_{OUT}$  represents the output of this bridge, which is due solely to the bridge mismatching and CM noise  $V_{NOISE}$ .

Such a bridge as Figure 6-21, when *maximized* for output sensitivity, will produce a differential output  $V_{OUT}$  which is highest as a function of element unbalance when all four resistances are of the same order.

The following general expression illustrates the intrinsic common-mode rejection (CMR) of this bridge as a function of the resistance values and their deviation,  $K_R$ :

$$CMR(dB) = 20 \bullet \log_{10} \left[ \left( 1 + \left( R_{IN} / R_{OUT} \right) \right) / K_{R} \right]$$

Eq. 6-12

Some sample calculations with this relationship show that *CMR* is a *minimum* for a given change in  $K_R$  (the total resistor deviation expressed in fractional form) when  $R_{IN} \approx R_{OUT}$ . A CMR minimum is simply another way of saying that the bridge is most sensitive to the excitation voltage  $V_{NOISE}$  when  $R_{IN} \approx R_{OUT}$ . To place this in perspective, a conventional instrumentation bridge operates thusly, with all four arms nominally equal. This yields the highest sensitivity to the applied voltage (see Chapter 4).

On the other hand, CMR is maximum and bridge sensitivity is *minimized*, when the upper and lower arm resistances differ widely. This improves substantially as  $R_{IN}$  becomes >>  $R_{OUT}$ . Or, within an audio system, as the driver  $R_{OUT}$  is by design made much less than the receiver  $R_{IN}$ . With the example values above, there is a 1/30,000 ratio between the  $R_{OUT}/R_{IN}$  upper/lower elements. This factor makes relatively high percentage changes in either the upper (or the lower) arm resistances a somewhat harmless phenomenon. In other words, small  $R_{OUT}$  or  $R_{IN}$  changes will then have little CMR effect upon the output.

For example, taking the Figure 6-21 values and assuming a 10% change in  $R_{OUT}$ , will produce an output which is about 110 dB down from the noise voltage  $V_{NOISE}$ . By contrast, if all the bridge values were to be equal, the same 10% deviation would produce an output only 26 dB down. Note that there are two control point towards this. One can *lower*  $R_{OUT}$ , for a given  $R_{IN}$ , and increase CMR. Or, one can achieve the same effect by *increasing*  $R_{IN}$ , for a given  $R_{OUT}$ . This makes the point that *a high ratio between*  $R_{IN}$  and  $R_{OUT}$  aids in maintaining high CMR, as is shown by Figure 6-22.

In a real transmission system, there will be inevitable noise potentials developed between the respective driver and receiver chassis common points, since they are located separately and are powered with different power sources. The resulting noise voltage can be predicted with the aid of Figure 6-22. As a minimum, a good system should maintain an  $R_{IN}/R_{OUT}$  of at least 1000, with 10 k or more a goal. Under such conditions, with a bridge unbalance of 10%, this will still allow a theoretical CMR of 80 dB to 100 dB (see center column, with cited examples shown in boldface).

| R <sub>IN</sub> /R <sub>OUT</sub> | CMR(dB) for $K_R = 0.1$ | CMR(dB) for $K_{\rm B} = 0.01$ |

|-----------------------------------|-------------------------|--------------------------------|

|                                   |                         |                                |

| 10                                | 40.8                    | 60.8                           |

| 100                               | 60.1                    | 80.1                           |

| 400                               | 72.1                    | 92.1                           |

| 1k                                | 80                      | 100                            |

| 10k                               | 100                     | 120                            |

| 30k                               | 109.5                   | 129.5                          |

| 100k                              | 120                     | 140                            |

Figure 6-22: High  $R_{IN}/R_{OUT}$  minimizes sensitivity to CM noise, bridge imbalance